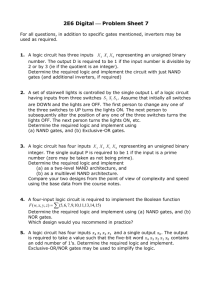

Week 11b OUTLINE – Synthesis of logic circuits – Minimization of logic circuits

advertisement

Week 11b OUTLINE – Synthesis of logic circuits – Minimization of logic circuits Reading: Hambley Ch. 7 through 7.6 EECS42, Fall 2005 Week 11b, Slide 1 Prof. White Combinational Logic Circuits • Logic gates combine several logic-variable inputs to produce a logic-variable output. • Combinational logic circuits are “memoryless” because their output value at a given instant depends only on the input values at that instant. • Next time, we will study sequential logic circuits that possess memory because their present output value depends on previous as well as present input values. EECS42, Fall 2005 Week 11b, Slide 2 Prof. White Boolean Algebra Relations A•A = A A•A = 0 A•1 = A A•0 = 0 A•B = B•A A•(B•C) = (A•B)•C A+A = A A+A = 1 A+1 = 1 A+0 = A A+B = B+A A+(B+C) = (A+B)+C A•(B+C) = A•B + A•C A•B = A + B A•B = A + B EECS42, Fall 2005 Week 11b, Slide 3 De Morgan’s laws Prof. White Boolean Expression Example F = A•B•C + A•B•C + (C+D)•(D+E) F = C•(A+D+E) + D•E EECS42, Fall 2005 Week 11b, Slide 4 Prof. White Logical Sufficiency of NAND Gates • If the inputs to a NAND gate are tied together, an inverter results • From De Morgan’s laws, the OR operation can be realized by inverting the input variables and combining the results in a NAND gate. • Since the basic logic functions (AND, OR, and NOT) can be realized by using only NAND gates, NAND gates are sufficient to realize any combinational logic function. EECS42, Fall 2005 Week 11b, Slide 5 Prof. White Logical Sufficiency of NOR Gates • Show how to realize the AND, OR, and NOT functions using only NOR gates • Since the basic logic functions (AND, OR, and NOT) can be realized by using only NOR gates, NOR gates are sufficient to realize any combinational logic function. EECS42, Fall 2005 Week 11b, Slide 6 Prof. White Synthesis of Logic Circuits Suppose we are given a truth table for a logic function. Is there a method to implement the logic function using basic logic gates? Answer: There are lots of ways, but one simple way is the “sum of products” implementation method: 1) Write the sum of products expression based on the truth table for the logic function 2) Implement this expression using standard logic gates. • We may not get the most efficient implementation this way, but we can simplify the circuit afterwards… EECS42, Fall 2005 Week 11b, Slide 7 Prof. White Example: the half adder and the full adder A B Carry Sum An+1 Bn+1 Cn+1 Cn Sn+1 EECS42, Fall 2005 An Bn Cn-1 Sn Week 11b, Slide 8 Prof. White Logic Synthesis Example: Adder Input A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Output C S1 0 0 1 0 0 0 1 1 0 0 1 1 0 1 1 1 EECS42, Fall 2005 S0 0 1 1 0 1 0 0 1 S1 using sum-of-products: 1) Find where S1 is 1 2) Write down each product of inputs which create a 1 ABC ABC ABC ABC 3) Sum all of the products ABC+ ABC+ ABC+ ABC 4) Draw the logic circuit Week 11b, Slide 9 Prof. White NAND Gate Implementation • De Morgan’s law tells us that is the same as • By definition, is the same as All sum-of-products expressions can be implemented with only NAND gates. EECS42, Fall 2005 Week 11b, Slide 10 Prof. White Creating a Better Circuit What makes a digital circuit better? • Fewer number of gates • Fewer inputs on each gate – multi-input gates are slower • Let’s see how we can simplify the sum-ofproducts expression for S1, to make a better circuit… – Use the Boolean algebra relations EECS42, Fall 2005 Week 11b, Slide 11 Prof. White Karnaugh Maps • Graphical approach to minimizing the number of terms in a logic expression: 1. 2. 3. 4. Map the truth table into a Karnaugh map (see below) For each 1, circle the biggest block that includes that 1 Write the product that corresponds to that block. Sum all of the products 4-variable Karnaugh Map 2-variable Karnaugh Map B 0 1 EECS42, Fall 2005 00 BC 00 01 11 10 0 1 A CD 00 01 11 10 3-variable Karnaugh Map AB 0 A 01 11 1 10 Week 11b, Slide 12 Prof. White Karnaugh Map Example Input A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Output C 0 1 0 1 0 1 0 1 EECS42, Fall 2005 S1 0 0 0 1 0 1 1 1 S0 0 1 1 0 1 0 0 1 Simplification of expression for S1: BC A 00 01 11 10 0 0 1 0 0 1 1 1 0 1 BC AC AC AB S1 = AB + BC + AC Week 11b, Slide 13 Prof. White Further Comments on Karnaugh Maps • The algebraic manipulations needed to simplify a given expression are not always obvious. Karnaugh maps make it easier to minimize the number of terms in a logic expression. EECS42, Fall 2005 Week 11b, Slide 14 Prof. White Homework Assignment 9 -- LogicWorks This 40-point assignment is to simulate one stage of a full adder using the LogicWorks program available on Windows machines in 199 Cory. Use your EE43 account log-in and password, or use this temporary log-in: ee42-temp pwd: Go Bears 005 Print out your circuit and the timing diagram and hand them in Thursday April 21 in the usual homework box. To help the grader, put “bus bars” with A and B and their complements on your circuit as shown on the next page here. There’s a LogicWorks manual/tutorial on those machines. Note: on your display be sure “show Window’s contents while dragging” is disabled. Your GSI has floppies you can use to store your work (temp account won’t allow machine storage). You can print your work on the printer in 199 Cory. If the Control bar doesn’t appear when you launch LogicWorks, on the Main toolbar at the top of the screen, click on Tools and then on Simulate. EECS42, Fall 2005 Week 11b, Slide 15 Prof. White Homework 9 -- continued EECS 40 Fall 2001 Lecture 2 W. G. Oldham Copyright Regents of University of California A B C A B C ABC A ABC B F C ABC ABC Exam ple of general purpose circuit to implement the truth table of Table 22.4. (This solution is NOT minimized.) Two sets of “bus bars” on left provide variables and their complements for whatever you connect on the right side. EECS42, Fall 2005 Week 11b, Slide 16 Prof. White Homework 9 -- concluded a. Draw and run your circuit as derived from the sum-of-products expressions for your sum and carry outputs using whatever gates you require. b. Then try to simplify those expressions using Boolean algebra. c. Then simply if possible using Karnaugh maps. d. Then draw the simplified circuit using whatever gates you need. e. How do you think the simplification has reduced the amount of space and number of transistors needed to make the full adder stage (qualitative answer acceptable)? Note: We could go further and realize the circuits entirely with NAND gates and obtain a quantitative answer, since we’ve already seen what transistors are inside a NAND gate in the Slide 6 of Week 10b, reprinted on next slide here. EECS42, Fall 2005 Week 11b, Slide 17 Prof. White CMOS NAND Gate VDD A A B 0 0 0 1 1 0 1 1 B F 1 1 1 0 F A B EECS42, Fall 2005 Week 11b, Slide 18 Prof. White