L18-ddg-singlecpu-co..

advertisement

inst.eecs.berkeley.edu/~cs61c

CS61C : Machine Structures

Lecture #18

Single Cycle CPU Control

CPS

today!

2005-11-02

There is one handout

today at the front and

back of the room!

Lecturer PSOE, new dad Dan Garcia

www.cs.berkeley.edu/~ddgarcia

Data Transfer Record!

A Japanese company

(Kansai Electric) claims fiber-optic

cables on power-transmitting steel

towers have achieved 1 Terabit/sec,

100 times faster than normal.

5:00:00 send

2 hr movie

5:00:01 get

2 hr movie

(< 1 second!)

news.softpedia.com/news/Japanese-Claim-New-Fiber-Optic-Transmission-Record-11257.shtml

CS61C L18 Single Cycle CPU Control (1)

Garcia, Fall 2005 © UCB

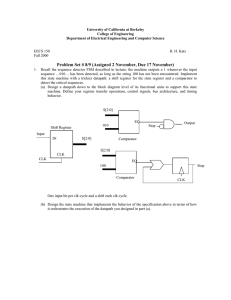

Summary: A Single Cycle Datapath

• Rs, Rt, Rd, Imed16 connected to datapath

• We have everything except control signals

Instruction<31:0>

MemWr

Clk

MemtoReg

0

32

Data In32

ALUSrc

Rs Rd Imm16

WrEn Adr

Data

Memory

32

Mux

32

1

<0:15>

Extender

16

ALU

busA

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

imm16

Rt

Zero

ALUctr

Mux

busW

32

Clk

Clk

<11:15>

Rt

RegDst

1 Mux0

Rs Rt

RegWr 5 5 5

<16:20>

Rd

Instruction

Fetch Unit

<21:25>

nPC_sel

1

ExtOp

CS61C L18 Single Cycle CPU Control (2)

Garcia, Fall 2005 © UCB

An Abstract View of the Critical Path

Critical Path (Load Operation) =

• This affects

Delay clock through PC (FFs) +

how much you Instruction Memory’s Access Time +

can overclock

Register File’s Access Time, +

your PC!

ALU to Perform a 32-bit Add +

Data Memory Access Time +

Ideal

Stable Time for Register File Write

Instruction

Instruction

Memory

Rd Rs Rt

5 5

5

PC

Clk

A

32

Rw Ra Rb

32 32-bit 32

Registers B

Clk

CS61C L18 Single Cycle CPU Control (3)

ALU

Next Address

Instruction

Address

Imm

16

32

Data

32 Address

Data

In

Ideal

Data

Memory

Clk

Garcia, Fall 2005 © UCB

Recap: Meaning of the Control Signals

0 PC <– PC + 4

1 PC <– PC + 4 +

“n”=next

{SignExt(Im16) , 00 }

• Later in lecture: higher-level connection

between mux and branch cond

• nPC_MUX_sel:

nPC_MUX_sel

Inst

Adr Memory

Adder

imm16

PC

Mux

Adder

PC Ext

CS61C L18 Single Cycle CPU Control (4)

00

4

Clk

Garcia, Fall 2005 © UCB

Recap: Meaning of the Control Signals

° MemWr: 1 write memory

• ExtOp: “zero”, “sign”

° MemtoReg: 0 ALU; 1 Mem

• ALUsrc: 0 regB;

1 immed

° RegDst: 0 “rt”; 1 “rd”

• ALUctr: “add”, “sub”, “or” ° RegWr: 1 write register

RegDst

ALUctr MemWr MemtoReg

=

32

WrEn Adr

Data In

Data

Clk Memory

ExtOp ALUSrc

CS61C L18 Single Cycle CPU Control (5)

32

0

Mux

ALU

Mux

Extender

Equal

Rd Rt

1 0

Rs Rt

RegWr 5 5 5

busA

Rw

Ra

Rb

busW

32

32 32-bit

32

Registers busB

0

32

Clk

1

imm16

32

16

1

Garcia, Fall 2005 © UCB

RTL: The Add Instruction

31

26

op

6 bits

21

rs

5 bits

16

rt

5 bits

11

6

0

rd

shamt

funct

5 bits

5 bits

6 bits

add rd, rs, rt

• MEM[PC]

Fetch the instruction

from memory

• R[rd] = R[rs] + R[rt] The actual operation

• PC = PC + 4

Calculate the next

instruction’s address

CS61C L18 Single Cycle CPU Control (6)

Garcia, Fall 2005 © UCB

Instruction Fetch Unit at the Beginning of Add

• Fetch the instruction from Instruction

memory: Instruction = MEM[PC]

• same for

all instructions

Inst

Memory

Adr

Instruction<31:0>

nPC_MUX_sel

Adder

imm16

PC

Mux

Adder

PC Ext

CS61C L18 Single Cycle CPU Control (7)

00

4

Clk

Garcia, Fall 2005 © UCB

The Single Cycle Datapath during Add

31

26

21

op

rs

16

11

rt

6

rd

shamt

• R[rd] = R[rs] + R[rt]

5

Zero

ALU

16

Extender

imm16

1

32

Rd

Clk

Imm16

MemtoReg = 0

MemWr = 0

0

32

Data In 32

ALUSrc = 0

Rs

WrEn Adr

32

Mux

busA

Rw Ra Rb

32

32 32-bit

Registers

busB

0

32

Rt

<0:15>

5

ALUctr = Add

Rt

<11:15>

5

Rs

Mux

32

Clk

Clk

1 Mux 0

RegWr = 1

busW

Rt

Instruction

Fetch Unit

<16:20>

RegDst = 1

Rd

funct

Instruction<31:0>

<21:25>

nPC_sel= +4

0

1

Data

Memory

ExtOp = x

CS61C L18 Single Cycle CPU Control (8)

Garcia, Fall 2005 © UCB

Instruction Fetch Unit at the End of Add

• PC = PC + 4

• This is the same for all instructions except:

Branch and Jump

Inst

Memory

Adr

Instruction<31:0>

nPC_MUX_sel

CS61C L18 Single Cycle CPU Control (9)

PC

Mux

Adder

imm16

Adder

0

00

4

1

Clk

Garcia, Fall 2005 © UCB

Single Cycle Datapath during Or Immediate?

31

26

op

21

rs

16

0

rt

immediate

• R[rt] = R[rs] OR ZeroExt[Imm16]

Instruction<31:0>

Zero MemWr =

32

ALUSrc =

0

32

Data In32

Clk

Imm16

MemtoReg =

WrEn Adr

32

Mux

ALU

Extender

16

1

Rs Rd

<0:15>

busA

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

imm16

Rt

ALUctr =

<11:15>

5

Rs Rt

5

5

Mux

32

Clk

Clk

1 Mux 0

RegWr =

busW

Rt

<16:20>

RegDst =

Rd

Instruction

Fetch Unit

<21:25>

nPC_sel =

1

Data

Memory

ExtOp =

CS61C L18 Single Cycle CPU Control (10)

Garcia, Fall 2005 © UCB

Single Cycle Datapath during Or Immediate?

31

26

op

21

16

rs

0

rt

immediate

• R[rt] = R[rs] OR ZeroExt[Imm16]

1

32

Imm16

MemtoReg = 0

MemWr = 0

0

32

Data In32

ALUSrc = 1

Rs Rd

Clk

WrEn Adr

32

Mux

ALU

Extender

16

Zero

<0:15>

busA

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

imm16

Rt

ALUctr = Or

<11:15>

Rs Rt

5

5

Mux

32

Clk

Clk

1 Mux 0

RegWr = 15

busW

Rt

<16:20>

RegDst = 0

Rd

Instruction

Fetch Unit

<21:25>

nPC_sel= +4

Instruction<31:0>

1

Data

Memory

ExtOp = 0

CS61C L18 Single Cycle CPU Control (11)

Garcia, Fall 2005 © UCB

The Single Cycle Datapath during Load?

31

26

21

op

rs

16

0

rt

immediate

• R[rt] = Data Memory {R[rs] + SignExt[imm16]}

Instruction<31:0>

5

busA

Rw Ra Rb

32

32 32-bit

Registers

busB

0

32

Rt

Zero

32

Imm16

MemtoReg =

MemWr =

0

32

Data In 32

ALUSrc =

Rd

Clk

Mux

ALU

16

Extender

imm16

1

Rs

<0:15>

5

ALUctr

=

Rt

<11:15>

5

Rs

Mux

32

Clk

Clk

1 Mux 0

RegWr =

busW

Rt

<21:25>

RegDst =

Rd

Instruction

Fetch Unit

<16:20>

nPC_sel=

1

WrEn Adr

Data

Memory

32

ExtOp =

CS61C L18 Single Cycle CPU Control (12)

Garcia, Fall 2005 © UCB

The Single Cycle Datapath during Load

31

26

21

op

rs

16

0

rt

immediate

• R[rt] = Data Memory {R[rs] + SignExt[imm16]}

busA

Rw Ra Rb

32

32 32-bit

Registers

busB

0

32

Rt

Zero

32

Imm16

MemtoReg = 1

MemWr = 0

0

32

Data In 32

ALUSrc = 1

Rd

Clk

Mux

ALU

16

Extender

imm16

1

Rs

<0:15>

5

ALUctr

= Add

Rt

<11:15>

5

Rs

Mux

32

Clk

Clk

1 Mux 0

RegWr = 1 5

busW

Rt

<16:20>

RegDst = 0

Rd

Instruction

Fetch Unit

<21:25>

nPC_sel= +4

Instruction<31:0>

1

WrEn Adr

Data

Memory

32

ExtOp = 1

CS61C L18 Single Cycle CPU Control (13)

Garcia, Fall 2005 © UCB

The Single Cycle Datapath during Store?

31

26

op

21

rs

16

0

rt

immediate

• Data Memory {R[rs] + SignExt[imm16]} = R[rt]

1 Mux 0

RegWr = 5

Rs Rt

5

5

Rt

ALUctr =

busA

16

Extender

imm16

1

32

ALUSrc =

Clk

MemtoReg =

0

32

Data In32

Imm16

WrEn Adr

32

Mux

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

Mux

32

Clk

Zero MemWr =

ALU

busW

Rs Rd

<0:15>

Clk

<11:15>

Rt

<16:20>

RegDst =

Rd

Instruction

Fetch Unit

<21:25>

nPC_sel =

Instruction<31:0>

1

Data

Memory

ExtOp =

CS61C L18 Single Cycle CPU Control (14)

Garcia, Fall 2005 © UCB

The Single Cycle Datapath during Store

31

26

op

21

rs

16

0

rt

immediate

• Data Memory {R[rs] + SignExt[imm16]} = R[rt]

32

0

32

Data In 32

ALUSrc = 1

Rs Rd

Clk

WrEn Adr

Data

Memory

32

Mux

1

<0:15>

16

Extender

imm16

Imm16

MemtoReg = x

Zero MemWr = 1

ALU

busA

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

Rt

<11:15>

ALUctr

= Add

Rs Rt

5

5

Mux

32

Clk

Clk

1 Mux 0

RegWr = 0 5

busW

Rt

<16:20>

RegDst = x

Rd

Instruction

Fetch Unit

<21:25>

nPC_sel= +4

Instruction<31:0>

1

ExtOp = 1

CS61C L18 Single Cycle CPU Control (15)

Garcia, Fall 2005 © UCB

The Single Cycle Datapath during Branch?

31

26

op

21

16

rs

0

rt

immediate

• if (R[rs] - R[rt] == 0) then Zero = 1 ; else Zero = 0

Instruction<31:0>

Data In32

ALUSrc =

0

32

Clk

WrEn Adr

32

Mux

32

Imm16

MemtoReg = x

Zero MemWr =

ALU

16

Extender

imm16

1

Rs Rd

<0:15>

busA

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

<11:15>

5

Rt

ALUctr =

Rs Rt

5

5

Mux

32

Clk

Clk

1 Mux 0

RegWr =

busW

Rt

<16:20>

RegDst =

Rd

Instruction

Fetch Unit

<21:25>

nPC_sel=

1

Data

Memory

ExtOp =

CS61C L18 Single Cycle CPU Control (16)

Garcia, Fall 2005 © UCB

The Single Cycle Datapath during Branch

31

26

op

21

16

rs

0

rt

immediate

• if (R[rs] - R[rt] == 0) then Zero = 1 ; else Zero = 0

Instruction<31:0>

32

0

32

Data In32

ALUSrc = 0

Rs Rd

Clk

WrEn Adr

32

Mux

1

<0:15>

16

Extender

imm16

Imm16

MemtoReg = x

Zero MemWr = 0

ALU

busA

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

<11:15>

5

Rt

ALUctr =Sub

Rs Rt

5

5

Mux

32

Clk

Clk

1 Mux 0

RegWr = 0

busW

Rt

<16:20>

RegDst = x

Rd

Instruction

Fetch Unit

<21:25>

nPC_sel= “Br”

1

Data

Memory

ExtOp = x

CS61C L18 Single Cycle CPU Control (17)

Garcia, Fall 2005 © UCB

Instruction Fetch Unit at the End of Branch

31

26

21

op

rs

16

rt

0

immediate

• if (Zero == 1) then PC = PC + 4 + SignExt[imm16]*4 ;

else PC = PC + 4

Inst

Memory

nPC_sel

Adr

Zero

Instruction<31:0>

• What is encoding of

nPC_sel?

• Direct MUX select?

nPC_MUX_sel

• Branch / not branch

PC

Adder

imm16

Mux

Adder

0

00

4

1

Clk

CS61C L18 Single Cycle CPU Control (18)

• Let’s pick 2nd option

nPC_sel

0

1

1

zero?

x

0

1

MUX

0

0

1

Q: What

logic gate?

Garcia, Fall 2005 © UCB

Administrivia

• Any Administrivia?

CS61C L18 Single Cycle CPU Control (19)

Garcia, Fall 2005 © UCB

Step 4: Given Datapath: RTL Control

Instruction<31:0>

Rd

<0:15>

Rs

<11:15>

Rt

<16:20>

Op Fun

<21:25>

<0:5>

Adr

<26:31>

Inst

Memory

Imm16

Control

nPC_sel RegWr RegDst ExtOp ALUSrc ALUctr MemWr MemtoReg

Zero

DATA PATH

CS61C L18 Single Cycle CPU Control (20)

Garcia, Fall 2005 © UCB

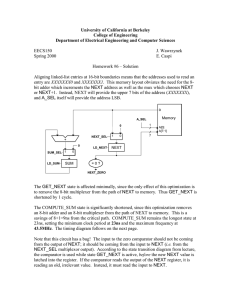

A Summary of the Control Signals (1/2)

inst

Register Transfer

ADD

R[rd] <– R[rs] + R[rt];

PC <– PC + 4

ALUsrc = RegB, ALUctr = “add”, RegDst = rd, RegWr, nPC_sel = “+4”

SUB

R[rd] <– R[rs] – R[rt];

PC <– PC + 4

ALUsrc = RegB, ALUctr = “sub”, RegDst = rd, RegWr, nPC_sel = “+4”

ORi

R[rt] <– R[rs] + zero_ext(Imm16);

PC <– PC + 4

ALUsrc = Im, Extop = “Z”, ALUctr = “or”, RegDst = rt, RegWr, nPC_sel =“+4”

LOAD

R[rt] <– MEM[ R[rs] + sign_ext(Imm16)]; PC <– PC + 4

ALUsrc = Im, Extop = “Sn”, ALUctr = “add”,

MemtoReg, RegDst = rt, RegWr,

nPC_sel = “+4”

STORE MEM[ R[rs] + sign_ext(Imm16)] <– R[rs]; PC <– PC + 4

ALUsrc = Im, Extop = “Sn”, ALUctr = “add”, MemWr, nPC_sel = “+4”

BEQ

if ( R[rs] == R[rt] ) then PC <– PC + sign_ext(Imm16)] || 00 else PC <– PC + 4

nPC_sel = “Br”, ALUctr = “sub”

CS61C L18 Single Cycle CPU Control (21)

Garcia, Fall 2005 © UCB

A Summary of the Control Signals (2/2)

See

Appendix A

func 10 0000 10 0010

We Don’t Care :-)

op 00 0000 00 0000 00 1101 10 0011 10 1011 00 0100 00 0010

add

sub

ori

lw

sw

beq

jump

RegDst

1

1

0

0

x

x

x

ALUSrc

0

0

1

1

1

0

x

MemtoReg

0

0

0

1

x

x

x

RegWrite

1

1

1

1

0

0

0

MemWrite

0

0

0

0

1

0

0

nPCsel

0

0

0

0

0

1

0

Jump

0

0

0

0

0

0

1

ExtOp

x

x

0

1

1

x

x

Add

Subtract

Or

Add

Add

Subtract

x

ALUctr<2:0>

31

26

21

16

R-type

op

rs

rt

I-type

op

rs

rt

J-type

op

CS61C L18 Single Cycle CPU Control (22)

11

rd

6

shamt

immediate

target address

0

funct

add, sub

ori, lw, sw, beq

jump

Garcia, Fall 2005 © UCB

The Single Cycle Datapath during Jump

31

J-type

26 25

0

op

target address

jump

• New PC = { PC[31..28], target address, 00 }

Instruction<31:0>

Jump=

<0:25>

Data In32

ALUSrc =

0

32

Clk

WrEn Adr

32

Mux

32

<0:15>

1

<11:15>

16

Extender

imm16

Rs Rd Imm16 TA26

MemtoReg =

Zero MemWr =

ALU

busA

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

<16:20>

5

Rt

ALUctr =

Rs Rt

5

5

Mux

32

Clk

Clk

1 Mux 0

RegWr =

busW

Rt

<21:25>

RegDst =

Rd

Instruction

Fetch Unit

nPC_sel=

1

Data

Memory

ExtOp =

CS61C L18 Single Cycle CPU Control (23)

Garcia, Fall 2005 © UCB

The Single Cycle Datapath during Jump

31

J-type

26 25

0

op

target address

jump

• New PC = { PC[31..28], target address, 00 }

Instruction<31:0>

Jump=1

<0:25>

Data In32

ALUSrc = x

0

32

Clk

WrEn Adr

32

Mux

32

<0:15>

1

<11:15>

16

Extender

imm16

Rs Rd Imm16 TA26

MemtoReg = x

Zero MemWr = 0

ALU

busA

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

<16:20>

5

Rt

ALUctr =x

Rs Rt

5

5

Mux

32

Clk

Clk

1 Mux 0

RegWr = 0

busW

Rt

<21:25>

RegDst = x

Rd

Instruction

Fetch Unit

nPC_sel=0

1

Data

Memory

ExtOp = x

CS61C L18 Single Cycle CPU Control (24)

Garcia, Fall 2005 © UCB

Instruction Fetch Unit at the End of Jump

31

26 25

J-type

0

op

target address

jump

• New PC = { PC[31..28], target address, 00 }

Jump

Inst

Memory

nPC_sel

Instruction<31:0>

Adr

Zero

nPC_MUX_sel

Adder

0

PC

Mux

Adder

imm16

00

4

How do we modify this

to account for jumps?

1

Clk

CS61C L18 Single Cycle CPU Control (25)

Garcia, Fall 2005 © UCB

Instruction Fetch Unit at the End of Jump

31

26 25

J-type

0

op

target address

jump

• New PC = { PC[31..28], target address, 00 }

Jump

Inst

Memory

nPC_sel

Instruction<31:0>

Adr

Zero

imm16

Mux

Adder

1

CS61C L18 Single Cycle CPU Control (26)

00

TA

4 (MSBs)

1

PC

Adder

0

26

Mux

4

00

nPC_MUX_sel

0

Clk

Query

• Can Zero still

get asserted?

• Does nPC_sel

need to be 0?

• If not, what?

Garcia, Fall 2005 © UCB

Build CL to implement Jump on paper now

Inst31

Inst30

Inst29

Inst28

Inst27

Inst26

Inst25

Jump

Inst01

Inst00

CS61C L18 Single Cycle CPU Control (27)

Garcia, Fall 2005 © UCB

Build CL to implement Jump on paper now

Inst31

Inst30

Inst29

Inst28

Inst27

Inst26

Inst25

Inst01

Inst00

A

0

0

0

0

1

0

2-input

6-bit-wide

XNOR

B

CS61C L18 Single Cycle CPU Control (28)

Ai

0

0

1

1

6-input

AND

Bi XNOR

0

1

1

0

0

0

1

1

Jump

Garcia, Fall 2005 © UCB

Peer Instruction

A. Our ALU is a synchronous device

B. We should use the main ALU to

compute PC=PC+4

C. The ALU is inactive for memory

reads or writes.

CS61C L18 Single Cycle CPU Control (29)

1:

2:

3:

4:

5:

6:

7:

8:

ABC

FFF

FFT

FTF

FTT

TFF

TFT

TTF

TTT

Garcia, Fall 2005 © UCB

Peer Instruction

Instruction<31:0>

RegWr

Rs Rt

5

Extender

16

1

32

Clk

Imm16

MemWr

MemtoReg

0

32

Data In 32

ALUSrc

Rs Rd

WrEn Adr

32

Mux

busA

Rw Ra Rb

32

32 32-bit

Registers busB

0

32

imm16

Rt

Zero

ALUctr

Mux

32

Clk

5

ALU

busW

5

<0:15>

Clk

1 Mux 0

<11:15>

RegDst

Rt

<21:25>

Rd

Instruction

Fetch Unit

<16:20>

nPC_sel

1

Data

Memory

ExtOp

A.

MemToReg=‘x’ & ALUctr=‘sub’. SUB or BEQ?

B.

ALUctr=‘add’. Which 1 signal is different for all 3 of:

ADD, LW, & SW? RegDst or ExtOp?

C.

“Don’t Care” signals are useful because we can

simplify our PLA personality matrix. F / T?

CS61C L18 Single Cycle CPU Control (30)

1:

2:

3:

4:

5:

6:

7:

8:

ABC

SRF

SRT

SEF

SET

BRF

BRT

BEF

BET

Garcia, Fall 2005 © UCB

And in Conclusion… Single cycle control

°5 steps to design a processor

• 1. Analyze instruction set => datapath requirements

• 2. Select set of datapath components & establish clock

methodology

• 3. Assemble datapath meeting the requirements

• 4. Analyze implementation of each instruction to

determine setting of control points that effects the

register transfer.

Processor

• 5. Assemble the control logic

Input

°Control is the hard part

°MIPS makes that easier

Control

Memory

Datapath

• Instructions same size

• Source registers always in same place

• Immediates same size, location

• Operations always on registers/immediates

CS61C L18 Single Cycle CPU Control (31)

Output

Garcia, Fall 2005 © UCB