EECS150 - Digital Design Lecture 15 - Sequential Circuits II

advertisement

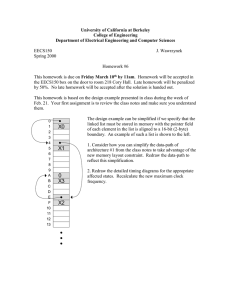

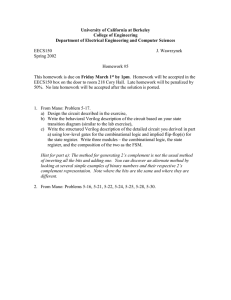

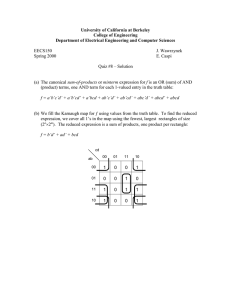

EECS150 - Digital Design Lecture 15 - Sequential Circuits II (Finite State Machines revisited) March 14, 2002 John Wawrzynek Spring 2002 EECS150 - Lec15-seq2 Page 1 Finite State Machines • Example: Edge Detector Bit are received one at a time (one per cycle), such as: 000111010 time CLK Design a circuit that asserts its output for one cycle when the input bit stream changes from 0 to 1. IN FSM OUT Try two different solutions. Spring 2002 EECS150 - Lec15-seq2 Page 2 State Transition Diagram Solution A IN=0 ZERO OUT=0 IN=1 IN=0 CHANGE OUT=1 IN=1 IN=0 IN 0 ZERO 1 0 CHANGE 1 0 ONE 1 PS 00 00 01 01 11 11 NS 00 01 00 11 00 11 OUT 0 0 1 1 0 0 ONE OUT=0 Spring 2002 IN=1 EECS150 - Lec15-seq2 Page 3 Solution A, circuit derivation PS IN 0 ZERO 1 0 CHANGE 1 ONE 0 1 PS 00 00 01 01 11 11 NS1 NS 00 01 00 11 00 11 FF 00 01 11 10 OUT 0 0 1 1 0 0 IN 1 NS0 Spring 2002 FF 0 0 0 0 1 1 - NS 1 = IN PS 0 PS 00 01 11 10 IN 0 1 0 0 0 1 1 1 - NS 0 = IN PS 00 01 11 10 PS1 OUT IN 0 IN 0 1 0 1 0 0 1 0 - OUT= PS 1 PS 0 PS0 EECS150 - Lec15-seq2 Page 4 Solution B Output depends non only on PS but also on input, IN IN=0 OUT=0 Let ZERO=0, ONE=1 ZERO IN=1 OUT=1 NS = IN, OUT = IN PS’ IN=0 OUT=0 ONE IN PS NS OUT 0 0 0 0 0 1 0 0 1 0 1 1 1 1 1 0 IN NS FF PS IN=1 OUT=0 OUT What’s the intuition about this solution? Spring 2002 EECS150 - Lec15-seq2 Page 5 Edge detector timing diagrams CLK IN OUT (solution A) OUT (solution B) • Solution A: output follows the clock • Solution B: output changes with input rising edge and is asynchronous wrt the clock. Spring 2002 EECS150 - Lec15-seq2 Page 6 FSM Comparison Solution A Moore Machine • output function only of PS • maybe more state • synchronous outputs Solution B Mealy Machine • output function of both PS & input • maybe fewer states • asynchronous outputs – no glitching – one cycle “delay” – full cycle of stable output – if input glitches, so does output – output immediately available – output may not be stable long enough to be useful: CLK CLK IN OUT Spring 2002 EECS150 - Lec15-seq2 OUT CL Page 7 FSM Recap Moore Machine input value STATE [output values] Mealy Machine input value/output values STATE Both machine types allow one-hot implementations. Spring 2002 EECS150 - Lec15-seq2 Page 8 FSM Optimization • State Reduction: Motivation: lower cost • fewer flip-flops in one-hot implementations • possibly fewer flip-flops in encoded implementations • more don’t cares in NS logic • fewer gates in NS logic Simpler to design with extra states then reduce later. Spring 2002 • Example: Odd parity checker. Two machines - identical behavior. 0 0 S0 [0] 0 1 S0 [0] S1 [1] 1 EECS150 - Lec15-seq2 1 1 1 S2 [0] S1 [1] 0 0 Page 9 State Reduction • State Reduction is based on: Two states are equivalent if, for each member of the set of inputs, they give exactly the same output and send the circuit either to the same state or to an equivalent state. If two states are equivalent, one can be eliminated without effecting the behavior of the FSM. • Several algorithms exist: – Row matching method. – Implication table method. Spring 2002 • “Row Matching” is based on the state-transition table: If two states have the same output, and both transition to the same next state, or both transition to each other, or both self-loop, then they are equivalent. Combine the equivalent states into a new renamed state. Repeat until no more states are combined. – Note: This algorithm is slightly different than the book. EECS150 - Lec15-seq2 Page 10 Row Matching Example State Transition Table NS output PS x=0 x=1 x=0 x=1 a a b 0 0 b c d 0 0 c a d 0 0 d e f 0 1 e a f 0 1 f g f 0 1 g a f 0 1 Spring 2002 EECS150 - Lec15-seq2 Page 11 Row Matching Example NS PS x=0 x=1 a a b b c d c a d d e f e a f f e f output x=0 x=1 0 0 0 0 0 0 0 1 0 1 0 1 NS PS x=0 x=1 a a b b c d c a d d e d e a d output x=0 x=1 0 0 0 0 0 0 0 1 0 1 Spring 2002 Reduced State Transition Diagram EECS150 - Lec15-seq2 Page 12 State Reduction • The “row matching” method is not guaranteed to result in the optimal solution in all cases, because it only looks at pairs of states. • For example: 0/1 S0 1/0 0/1 S1 1/0 1/0 • Another (more complicated) method guarantees the optimal solution: • “Implication table” method: See Mano, chapter 9. S2 0/1 Spring 2002 EECS150 - Lec15-seq2 Page 13 State Assignment (from Katz) • In encoded (non-one-hot) FSMs, the choice of binary encodings for the states has an influence on the number of logic gates (or LUTs) needed to compute the next state and outputs. • For n states, at least s bits are needed for a binary encoding. Where s log 2 n s • 2 ! different encodings exist. • We will look at several “by-hand” heuristic methods for choosing good assignments. • Some CAD tools will make assignments automatically. Spring 2002 EECS150 - Lec15-seq2 Page 14 State Maps S0 S1 Assignment State q2 q1 q0 S0 0 0 0 S1 0 0 1 S2 0 1 0 S3 0 1 1 S4 1 1 1 Assignment State q2 q1 q0 S0 0 0 0 S1 1 0 1 S2 1 1 1 S3 0 1 0 S4 0 1 1 S2 S3 q1 q0 S4 q1 q0 00 01 11 10 q2 0 1 S0 S4 S3 S1 S2 00 01 11 10 q2 0 1 S0 S1 S3 S2 S4 • “K-maps” are used to help visualize good encodings. • Adjacent states in the STD should be made adjacent in the map. Spring 2002 EECS150 - Lec15-seq2 Page 15 State Assignment Alternative heuristics based on input and output behavior as well as transitions: i/j Adjacent assignments to: i/k states that share a common next state (group 1's in next state map) Highest Priority states that share a common ancestor state (group 1's in next state map) Medium Priority i/j i/j states that have common output behavior (group 1's in output map) Lowest Priority Spring 2002 EECS150 - Lec15-seq2 Page 16 Example Example: 3-bit Sequence Detector Reset S0 Highest Priority: (S3', S4') 0,1/0 Medium Priority: (S3', S4') Lowest Priority: 0/1, 0/0: (S0, S1', S3') 1/0: (S0, S1', S3', S4') 1/0 S1' 0,1/0 1/0 S3' Spring 2002 0/0 S4' EECS150 - Lec15-seq2 Page 17 Example Paper and Pencil Methods Q0 Q1 1 0 0 S0 S1’ 1 S3’ S4’ Reset State = 00 Q0 0 Q1 Highest Priority Adjacency 1 0 S0 S3 1 S1’ S4’ Spring 2002 Not much difference in these two assignments EECS150 - Lec15-seq2 Page 18 State Assignment Example Another Example: 4 bit String Recognizer Highest Priority: 2x(S1, S2) (S3', S4'), (S7', S10') Reset S0 0/0 S1 1/0 0/0 Spring 2002 Lowest Priority: 0/0: (S0, S1, S2, S3', S4', S7') 1/0: (S0, S1, S2, S3', S4', S7') 1/0 S7' 0,1/0 0/0 S4' S3' 0,1/0 Medium Priority: (S1, S2), 2x(S3', S4'), (S7', S10') S2 1/0 0/0 1/0 S10' 0/1 1/0 EECS150 - Lec15-seq2 Page 19 State Assignment State Map Q1 Q0 00 Q2 0 01 11 10 S0 0 1 01 11 S0 1 Q1 Q0 00 Q2 0 00 = Reset = S0 01 11 10 01 11 10 S0 01 S0 1 10 Q1 Q0 00 Q2 S3' 0 S0 S4' 1 S7' Q1 Q0 Q2 00 S10' 11 10 S3' S7' 0 S0 S3' S4' S10' 1 S7' S4' S10' 01 11 10 11 01 11 10 S0 S1 S3' S7' 0 S0 S1 S3' S2 S4' S10' 1 S7' S2 S4' 1 (a) Spring 2002 Q1 Q0 Q2 00 01 Q1 Q0 00 Q2 0 (S1, S2), (S3', S4'), (S7', S10') placed adjacently 1 Q1 Q0 00 Q2 0 Q1 Q0 00 Q2 10 S10' (b ) EECS150 - Lec15-seq2 Page 20 State Assignment Effect of Adjacencies on Next State Map Current State (S0 ) 000 (S1 ) 001 (S2 ) 101 ( S'3 ) 011 (S4' ) 111 ( S'7) 010 (S'10) 110 Next State X = 0 X= 1 001 101 011 111 111 011 010 010 010 110 000 000 000 000 Q2 Q1 00 Q0 X 00 0 01 0 11 0 10 X Q2 Q 1 00 Q0 X 00 0 01 1 0 0 X 01 11 1 0 1 0 10 0 0 0 1 11 0 10 X 0 0 0 X 01 11 1 1 1 1 10 1 1 1 1 P2 Current State ( S0) 000 ( S1) 001 ( S2) 010 ( S3' ) 011 ( S'4 ) 100 ( S'7) 101 (S'10) 110 Next State X = 0 X= 1 001 010 011 100 100 011 101 101 101 110 000 000 000 000 Q2 Q1 00 Q0 X 00 1 01 0 01 0 11 0 10 X 1 0 0 X 11 1 0 0 1 10 1 0 0 1 01 11 10 0 0 1 P1 Q2 Q1 00 Q0 X 00 0 01 11 10 Q2 Q1 00 Q0 X 00 0 1 0 1 01 0 0 0 1 01 11 1 1 X 0 10 0 1 X 0 P0 Q2 Q1 00 Q0 X 00 1 01 11 10 0 0 0 1 1 0 1 01 0 1 0 0 11 0 0 X 0 11 0 1 X 0 10 1 0 X 0 10 1 1 X 0 P2 P1 P0 First encoding exhibits a better clustering of 1's in the next state map Spring 2002 EECS150 - Lec15-seq2 Page 21