EECS150 - Digital Design Lecture 12 - Combinational Logic Circuits Part 3

advertisement

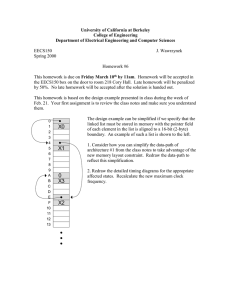

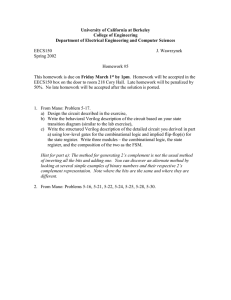

EECS150 - Digital Design Lecture 12 - Combinational Logic Circuits Part 3 March 4, 2002 John Wawrzynek Spring 2002 EECS150 - Lec12-cl3 Page 1 In the News ... Spring 2002 EECS150 - Lec12-cl3 Page 2 Multiplication a3b3 a3b2 a2b3 X a3b1 a2b2 a1b3 a3 b3 a2 b2 a1 b1 a0 b0 a3b0 a2b1 a1b2 a0b3 a2b0 a1b1 a0b2 a1b0 a0b1 a0b0 ... a1b0+a0b1 a0b0 Multiplicand Multiplier Partial products Product Many different circuits exist for multiplication. Each one has a different balance between speed (performance) and amount of logic (cost). Spring 2002 EECS150 - Lec12-cl3 Page 3 “Shift and Add” Multiplier B P n-bit shift registers • Sums each partial product, one at a time. • In binary, each partial product is shifted versions of A or 0. + n-bit adder 0 1 0 A n-bit register • Cost n, = n clock cycles. • What is the critical path for determining the min clock period? Spring 2002 Control Algorithm: 1. P 0, A multiplicand, B multiplier 2. If LSB of B==1 then add A to P else add 0 3. Shift [P][B] right 1 4. Repeat steps 2 and 3 n-1 times. 5. [P][B] has product. EECS150 - Lec12-cl3 Page 4 “Shift and Add” Multiplier Signed Multiplication: Remember for 2’s complement numbers MSB has negative weight: N 2 X xi 2i xn 1 2 n 1 i 0 ex: -6 = 110102 = 0•20 + 1•21 + 0•22 + 1•23 - 1•24 = 0 + 2 + 0 + 8 - 16 = -6 • Therefore for multiplication: a) subtract final partial product b) sign-extend partial products • Modifications to shift & add circuit: a) adder/subtractor b) sign-extender on P shifter register Spring 2002 EECS150 - Lec12-cl3 Page 5 Array Multiplier Generates all partial products simultaneously. b3 0 b2 0 b1 0 b0 0 a0 0 p0 Each row: n-bit adder with AND gates. bj sum in a1 ai 0 p1 a2 FA carry in 0 p2 sum out a3 0 p7 Spring 2002 p6 p5 p4 p3 EECS150 - Lec12-cl3 What is the critical path? Delay ?, cost ? Page 6 Carry-save Addition • Speeding up multiplication is a matter of speeding up the summing of the partial products. • “Carry-save” addition can help. • Carry-save addition passes (saves) the carries to the output, rather than propagating them. carry-save add carry-propagate add • • • • Example: sum three numbers, 310 = 0011, 210 = 0010, 310 = 0011 310 + 210 c s 0011 0010 0100 = 410 0001 = 110 carry-save add 310 0011 c 0010 = 210 s 0110 = 610 1000 = 810 In general, carry-save addition takes in 3 numbers and produces 2. Whereas, carry-propagate takes 2 and produces 1. With this technique, we can avoid carry propagation until final addition Spring 2002 EECS150 - Lec12-cl3 Page 7 Spring 2002 EECS150 - Lec12-cl3 Page 8 Array Multiplier with Carry-Save Spring 2002 EECS150 - Lec12-cl3 Page 9 Spring 2002 EECS150 - Lec12-cl3 Page 10 Spring 2002 EECS150 - Lec12-cl3 Page 11 CL Circuits from Mano • Magnitude Comparator • Multiplexors (revisited) • Decoders – basic – hierarchical • Encoders – standard – Priority Encoder Spring 2002 EECS150 - Lec12-cl3 Page 12 Magnitude Comparator • We studied magnitude comparators in CS61c as part of the MIPS processor design. • What was that method? Why that then and not now? (A>B) = A3B’3 + x3A2B’2 + x3x2A1B’1 + x3x2x1A0B’0 (A>B) = A’3B3 + x3A’2B2 + x3x2A’1B1 + x3x2x1A’0B0 (A=B) = x3x2x1x0 Spring 2002 EECS150 - Lec12-cl3 Page 13 Multiplexors Revisited • • • • • • Basic AND/OR form NAND/NAND tristate buffer based transmission gate based hierarchical decoder based – delay analysis Spring 2002 EECS150 - Lec12-cl3 Page 14 Decoders Spring 2002 EECS150 - Lec12-cl3 Page 15 Hierarchical Decoders Spring 2002 EECS150 - Lec12-cl3 Page 16 Encoders • Generates binary code at output corresponding to input code. • Example: one-hot to binary encoder. (Opposite of decoder) abcd xy 1000 00 0100 01 0010 10 0001 11 • Priority Encoder: – If two or more inputs are equal to 1 at the same time the input with the highest “priority” will take precedence. • Example: abcd 0000 1000 - 100 - - 10 - - - 1 xy V - - 0 00 0 01 1 10 1 11 1 • “V” is the valid signal, “d” has highest priority. Spring 2002 EECS150 - Lec12-cl3 Page 17