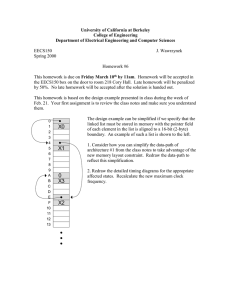

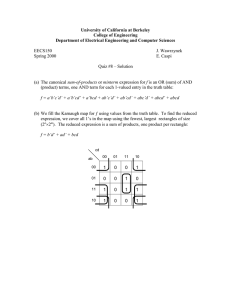

EECS150 - Digital Design Lecture 3 - Timing January 29, 2002 John Wawrzynek

advertisement

EECS150 - Digital Design Lecture 3 - Timing January 29, 2002 John Wawrzynek Spring 2002 EECS150 - Lec03-Timing Page 1 Outline • General Model of Synchronous Systems – Performance Limits • • • • Announcements Delay in logic gates Delay in wires Delay in flip-flops Spring 2002 EECS150 - Lec03-Timing Page 2 General Model of Synchronous Circuit clock input input CL CL reg reg output option feedback output • All wires, except clock, may be • multiple bits wide. • Registers (reg) – collections of flip-flops • • clock • – distributed to all flip-flops Combinational Logic Blocks (CL) – no internal state – output only a function of inputs Particular inputs/outputs are optional Optional Feedback – typical rate? Spring 2002 EECS150 - Lec03-Timing Page 3 Example Circuit • Parallel to Serial Converter • All signal paths single bit wide • Registers are single flip-flops • Combinational Logic blocks are simple multiplexors • No feedback. Spring 2002 EECS150 - Lec03-Timing Page 4 General Model of Synchronous Circuit clock input input CL reg CL reg output option feedback output • How do we measure performance? – operations/sec? – cycles/sec? • What limits the clock rate? • What happens as we increase the clock rate? Spring 2002 EECS150 - Lec03-Timing Page 5 Limitations on Clock Rate • Logic Gate Delay • Delays in flip-flops D input clk output Q t • What are typical delay values? setup time clock to Q delay • Both times contribute to limiting the clock period. • What must happen in one clock cycle for correct operation? • Assuming perfect clock distribution (all flip-flops see the clock at the same time): – All signals must be ready and “setup” before rising edge of clock. Spring 2002 EECS150 - Lec03-Timing Page 6 Example • Parallel to serial converter: T > time(clk->Q) + time(mux) + time(setup) a b Spring 2002 EECS150 - Lec03-Timing Page 7 Announcements • Lectures now being web-cast and recorded online. URL: • Look at notes online before class. – Suggestion: print out bring copy to class and annotate when necessary. My notes are intentionally incomplete. • Homework #1 online. Turn in before 12 noon Friday. • Discussions, TA office hours, and labs this week. • Quiz Friday at lab lecture. Spring 2002 EECS150 - Lec03-Timing Page 8 Qualitative Analysis of Logic Delay • Improved Transistor Model: nFET • • We refer to transistor "strength" as the amount of current that flows for a given Vds and Vgs. The strength is linearly proportional to the ratio of W/L. pFET Spring 2002 EECS150 - Lec03-Timing Page 9 Gate Switching Behavior • Inverter: • NAND gate: Spring 2002 EECS150 - Lec03-Timing Page 10 Gate Delay • Cascaded gates: Vout Vin Spring 2002 EECS150 - Lec03-Timing Page 11 Gate Delay • Fan-out: • “Fan-in” • What is the delay in this circuit? • Critical Delay Spring 2002 EECS150 - Lec03-Timing Page 12 Wire Delay • In general wire behave as “transmission lines”: – signal wave-front moves close to the speed of light • ~1ft/ns – In ICs most wires are short, therefore the transit times are relatively short compared to the clock period and can be ignored. – Not so on PC boards. t x Spring 2002 EECS150 - Lec03-Timing Page 13 Wire Delay • Even in those cases where the transmission line effect is negligible: – Wires posses distributed resistance and capacitance • For long wires on ICs: – busses, clock lines, global control signal, etc. – distributed RC (and therefore long delay) significant – signals are “rebuffered” to reduce delay: – Time constant associated with distributed RC is proportional to the square of the length – For short wires on ICs, resistance is insignificant (relative to effective R of transistors), but C is important. – Typically around half of C of gate load is in the wires. Spring 2002 EECS150 - Lec03-Timing Page 14 Delay in Flip-flops • Setup time results delay through first latch. • Clock to Q delay results from delay through second latch. Spring 2002 EECS150 - Lec03-Timing Page 15