Submicron Scaling of III-V HBTs for Mark Rodwell

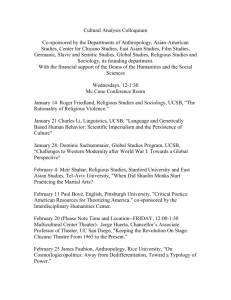

advertisement

Submicron Scaling of III-V HBTs for 40-200 GHz Analog & Digital ICs Mark Rodwell University of California, Santa Barbara rodwell@ece.ucsb.edu 805-893-3244, 805-893-3262 fax Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September State-of-art in HBTs, 2000: cutoff frequencies f SiGe ~0.1 um emitters t f max f t ~1 um emitters (0.4 um) InP f f t AlGaAs/GaAs & GaInP/GaAs 0 50 100 150 max 200 f 250 ~1 um emitters max 300 350 Frequency, GHz Si / SiGe have significantly poorer material parameters …but are much better scaled in size and current density Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September State-of-Art in HBTs, 2000: small-scale circuits amplifiers SiGe logic amplifiers InP logic 0 20 40 60 80 100 Frequency, GHz Si / SiGe has rough parity in logic with InP despite lower ft, fmax due to higher current density, better emitter contacts Si/SiGe has significantly slower amplifiers due to lower ft, fmax Si/SiGe has much better scales of integration, etc Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September 160 Gb/s is more than possible ! Agilent Conexant UCSB Zach Griffith 160 Gb/s LIA simulations using UCSB HBT model 0.22 0.22 0.20 0.20 0.18 0.18 0.16 0.16 0.14 0.14 0.12 0.12 0.10 0.10 0.08 0.08 0.06 0.06 0.04 out_diff out_diff 0.04 0.02 0.00 -0.02 0.02 0.00 -0.02 -0.04 -0.04 -0.06 -0.06 -0.08 -0.08 -0.10 -0.10 -0.12 -0.12 -0.14 -0.14 -0.16 -0.16 -0.18 -0.18 -0.20 -0.20 -0.22 0 1 2 3 4 5 6 7 time, psec 8 9 10 11 12 13 -0.22 0 1 2 3 4 5 6 7 8 9 10 11 12 13 time, psec Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September base contact pad Scaling Laws for fast HBTs transferred-substrate for x 2 improvement of all parasitics: ft, fmax, logic speed… base 2: 1 thinner collector 2:1 thinner emitter, collector junctions 4:1 narrower current density 4:1 higher emitter Ohmic 4:1 less resistive undercut-collector emitter Challenges with Scaling: Collector mesa HBT: collector under base Ohmics. Base Ohmics must be one transfer length sets minimum size for collector Emitter Ohmic: hard to improve…how ? Current Density: dissipation, reliability Loss of breakdown avalanche Vbr never less than collector Egap (1.12 V for Si, 1.4 V for InP) ….sufficient for logic, insufficient for power base contact InGaAs collector undercut collector junction collector -base junction InGaAs base InP collector collector contact InGaAs subcollector InP subcollector SI substrate collector contact Narrow-mesa with 1E20 carbon-doped base emitter base contact base contact base polymer polymer sub collector SI substrate Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September Submicron Transferred-Substrate HBT UCSB Michelle Lee 3000 Å collector 400 Å base with 52 meV grading AlInAs / GaInAs 30 / GaInAs HBT Mason's gain, U Gains, dB 25 20 MSG 15 H 10 emitter, 0.4 x 6 mm 2 5 21 f = 204 GHz t collector, 0.4 x 6 mm I = 6 mA, V = 1.2 V 2 c f max = 1.1 THz (?) ce 0 10 100 1000 Frequency, GHz Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September Record ft HBT UCSB Yoram Betser 2000 Å collector 300 Å base with 52 meV grading AlInAs / GaInAs / GaInAs HBT 50 h 21 Gains (dB) 40 30 U 20 V 10 f 2 CE = 1 V, J = 1.5 mA/um t = 295 GHz C f MAX = 295 GHz Emitter 1 x 8 mm2, Collector 2 x 8.5 mm2. 0 1 10 Frequency (GHz) 10 2 Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September UCSB pk Sundararajan M Dahlstrom High Speed, High Breakdown DHBTs 1x 8 micron emitter, 2x 10 micron collector 2 10 4 1.5 10 4 20 15 m2 freq=165.0GHz dB(short..S(2,1))=0.000 5 2 J (A/cm ) m2 m1 0 1 10 4 BVCEO>9 V c dB(short..S(2,1)) U dB(h21) 10 -5 m1 freq=303.0GHz dB(short..S(2,1))=0.000 -10 5000 ft = 165 GHz; fmax = 303 GHz -15 0 0 2 1E9 1E10 1E11 4 c 1E12 freq, Hz 6 I - V characteristics V (volts) ce -20 8 10 ce 8 I in steps B 7 of 20 uA 105 A/cm2 5 4 c I (mA) 6 3 2 5 V breakdown at 105 A/cm2 1 0 0 1 2 3 V (volts) 4 5 6 ce Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September High Speed Amplifiers UCSB Dino Mensa PK Sundararajan 18 dB, DC-50 GHz 20 S21 15 397 GHz gain x bandwidth from 2 HBTs 10 5 0 S11 -5 -10 S22 -15 -20 0 10 20 30 40 50 8.2 dB, DC-80 GHz 10 Gains, dB S 21 5 0 S -5 11 -10 S 22 -15 0 10 20 30 40 50 60 70 80 Frequency, GHz Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September HBT distributed amplifier AFOSR 11 dB, DC-87 GHz UCSB PK Sundararajan 15 S 10 21 Gains, dB 5 0 -5 S -10 22 S 11 -15 -20 0 20 40 60 Frequency, GHz 80 TWA with internal ft-doubler cells Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September UCSB James Guthrie InP-HBT W-band Amplifiers Balanced Amplifier: 10.7dBm at 78GHz ARO Caltech Common-Base Amplifier: 9.7dBm at 82.5 GHz (transferred-substrate HBT) InGaAs-collector: Vbr=1.5 V low power InP-collector: Vbr~5 V higher powers expected Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September 66 GHz HBT master-slave flip-flop UCSB Michelle Lee Objectives: 100 + GHz logic Approach: transferred-substrate HBTs, microwave / digital design Simulations: 95 GHz clock rate in SPICE Accomplishments: operation to 66 GHz 33.0 GHz static divider output at 66.0 GHz input divider output, mV 0 -20 -40 -60 -80 -100 0 50 100 time, ps 150 200 Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September 3500-HBT 20 GHz Sine ROM WOM receivers & drivers decoder core UCSB Yoram Betser ROM core output latches input latches selectors t C V I Digital Signal receivers Low Voltage Swing Ik Iref Io V kT I 0 I k ln q Io (it is hard to build large ICs in a university cleanroom) Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September UCSB Shrinivasan Jaganathan Delta-Sigma ADC 18 GHz clock rate 150 HBTs Power Spectrum (dB below full scale) 6.2 ENOB for a 1 GHz signal ( 2 GS/s equivalent Nyquist) 0 Matlab Simulation -20 Input Output -40 <-signal OSR = 128 F = 20 GHz -60 ADC noise clock SNR = 90 dB in 1 MHz -80 = 150 dB in 1 Hz -100 -120 1 10 100 1000 Frequency (MHz) 10000 (off-wafer op-amps sets common-mode bias) master 6.6K 6.6K Integrator Integrator (bias) M/S latched comparator (off-wafer op-amps sets common-mode bias) 1.25K 1.25K input 1.25K 1.25K 6.6K 5 5 slave 6.6K 5 5 (bias) 50 50 250 250 Input gm gm M/S Flip flop integrator 1 output -4v integrator 2 clock clock 1 bit DAC 1 bit DAC Delayed Clock clock buffers delayed clock ADC Block Diagram (transmission line delay to set DAC gatiing clock towards later half of the eye ) RTZ DAC clock Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September 185 GHz HBT Amplifier AFOSR UCSB Miguel Urteaga 0 -2 S22 S11, S22, dB -4 -6 -8 S11 -10 -12 -14 -16 -18 140 150 160 170 180 190 200 210 220 Frequency, GHz 4 3 50 0.2pF 80 1.2ps OUT 80 1.2ps 50 30 1.2ps S21, dB 1 30 0.2ps IN 2 50 0 -1 -2 -3 -4 0.6ps -5 140 150 160 170 180 190 200 210 220 Frequency, GHz Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September 19 GHz 2-bit adder UCSB Thomas Mathew 0 C 2out = A 1B 1 + B1C1 + A1C1 C 1out = A 0B 0 + B0C0 + A0C0 f C 2out = A 1B 1 + B1C1 + A1C1 max ck C 1out = A 0B 0 + B0C0 + A0C0 C0 C1 B0 B0 B0 A0 C0 C1 C1 C1 C1 C0 LOGIC STAGE CK C1 C1 B1 B1 A0 C1 CK B1 B1 A1 C1 A1 CK out = 9 .5GHz -0.1 C1 B0 Vout(Volts) C0 = 19GHz, f -0.05 LATCH STAGE -0.15 -0.2 CK DIODE LEVEL SHIFTER -0.25 B 0 = B1 = High (0.0V), A0 = A1 = Low (-0.3V), C0 = C2out for testing -0.3 0 100 200 300 Time(ps) 400 500 LATCH FOR PIPELINE DELAY LATCH STAGE S0 = A0 + B0 + C0 C0 S0 = A0 + B0 + C0 C0 C0 B0 B0 A0 B0 3 INPUT XOR CK A0 CK CK CK C0 = High (0.0V), A 0 = Low (-0.3V), B0 = S0 for testing Rodwell et al, UCSB: Keynote talk, 2000 IEEE Bipolar/BICMOS Circuits and Technology Meeting, Minneapolis, September