2004 CAPSTONE CDR Team SAFE Members Anders Fornberg Alejandro Henriquez

advertisement

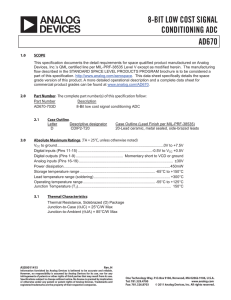

2004 CAPSTONE CDR Team SAFE Members Anders Fornberg Alejandro Henriquez Shannon Lahr Aaron Lyons Sean Groves Shannon Presentation Overview Project Overview System Specification Subsystem Design Processor & FPGA Power & Structures Sensors & Motors Current Status and Project Goals Shannon Project Description • Modified RC car that can sense an accident threat and take corrective action • Detects and Prevents multiple accidents • Head on Collisions • Merging into blind spots • Backing into Stationary Objects Shannon Modes of Operation 3 Modes of operation 1) User has complete control of the RC car. 2) Primary: SAFE System provides audible warning when an accident is immanent. If corrective action is not taken than Safe System takes control. 3) When accident is immanent, SAFE System takes immediate action and assumes control from the user. Shannon System Overview Aaron Interface Specification Aaron Interrupt Type Aaron Current Speed Aaron Speed Action Aaron Turn Action Aaron Core Microprocessor U1 34 33 32 43 45 47 49 44 46 48 50 8 7 17 51 52 26 19 18 3 2 PA0 PA1 PA2 PE0 PE1 PE2 PE3 PE4 PE5 PE6 PE7 XT EX RST VRL VRH VDD IRQ XIRQ MODA MODB MC68HC11E0 Alex PA3 PA4 PA5 PA6 PA7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7 PD0 PD1 PD2 PD3 PD4 PD5 AS R/W E 31 30 29 28 27 42 41 40 39 38 37 36 35 MC68HC11E0 Basic Functionality 9 10 11 12 13 14 15 16 20 21 22 23 24 25 4 6 5 Manager Memory access Data execution FPGA IRQ requests LCD control Sensors 20x4 DMC-20434N RS232 Communication Downloading Data FPGA U31 18 19 20 23 24 25 26 27 28 38 39 40 44 45 46 47 48 49 50 62 68 70 15 17 16 75 71 29 51 72 73 35 57 32 30 34 I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O TDI( I/O) TMS(I/O) TCK(I/O) TDO(I/O) SGCK2(I/O) SGCK3(I/O) SGCK4(I/O)DOUT 56 58 59 61 65 67 69 DONE INIT(I/O) PROGRAM 77 78 79 80 81 82 83 84 3 4 5 6 7 8 9 10 13 14 MODE NC NC Basic Functionality Work Horse Read Sensors Chip Select I/O I/O 36 37 60 66 Interrupt reg. Speed reg. Distance reg. Receive Data from HC11 HDC LDC(I/O) Send Interrupts (XIRQ) Provide HC11 with: 53 41 55 CCLK PGCK2(I/O) PGCK3(I/O) XCS10 (I/O) WS/AO PGCK4(I/O)A1 (I/O) CS1/A2 (I/O) A3 (I/O) A4 (I/O) A5 (I/O) A6 (I/O) A7 (I/O) A8 (I/O) A9 (I/O) A10 (I/O) A11 (I/O) A12 (I/O) A13 (I/O) A14 SGCK1(I/O)A15 PGCK1(I/O)A16 (I/O) A17 DIN( I/O) XCS10/LCC Alex I/O I/O I/O I/O I/O I/O I/O Speed Action reg. Turn Action reg. Interrupt car control Speed Controller Steering Controller Alex Memory Map Alex Power Shannon Power Continued 20ft tether to power car during testing 3 9V batteries in parallel for expo 150mAh/battery = 450mAh Expected mAh of project: Shannon Board = 100mA 6 Sensors = 180 mA LCD Screen = 4.5mA Total = Approximately 300mA Structures Shannon Structures Continued Shannon Structures Continued Shannon Structures Continued Shannon Drive/Steering Motor Control Anders Steering Motor Waveform Amplitude [V] Pulse Steering Motor Control 4.5 4 3.5 3 2.5 2 1.5 1 0.5 0 Straight Full Left Full Right Slow Right Slow Left 0 0.5 1 1.5 2 Time [ms] Pulse Steering Motor Motor Anders Burst Rate 20ms Forward Pulse Width 1.5ms Max Left 1ms Max Right 2ms Slight Left 1.4ms Slight Right 1.6ms 2.5 3 3.5 Drive Motor Waveform Amplitude [V] Pulse Drive Motor Control 4.5 4 3.5 3 2.5 2 1.5 1 0.5 0 Neutral Max Forward Max Reverse Pulse Drive Motor 0 1 2 Time [ms] Anders 3 4 Burst Rate 20ms Neutral PW 1.5ms Max Forward PW 1ms Max Reverse PW 2ms Vmax 4.125 Sensor Package 9 V Sensors 700 Output [mV] 600 500 400 300 200 100 0 0 10 20 30 40 50 60 70 Distance [inches] Problems Encountered •Voltage level would drift for various reason •Highly Dependent on surface tilt and material •Non linear output at large distances •“Sort of” reliable at < 40 inches •Needed use of op-amp, AC to DC, and A-D converter Anders Sensor Package SRF04 Voltage 5v Current 30mA Typ. 50mA Max Maximum Range 3m Minimum Range 3 cm Densitivity Detect a 3cm diameter stick at >2 m Size 1.75”w x .625”h x .5” d Anders Sensor Data Sensor SRF04 at 14 in high Pulse Width (mSec) 14 12 10 8 6 4 2 0 0 20 40 60 Distance (inches) Equation For Linear Section t=.1461*d+.0144 Anders 80 100 120 Sensor Field Anders Current Status Processor and Memory ADDR[0:15] U27 A8 A9 A10 A11 A12 A13 A14 A15 U1 34 33 32 Y1 OSC8 OUT 5 43 45 47 49 44 46 48 50 8Mhz SW2 1 R1 VCC D1 8 7 U24C U24B RESET SWITCH PA0 PA1 PA2 PE0 PE1 PE2 PE3 PE4 PE5 PE6 PE7 XT EX PA3 PA4 PA5 PA6 PA7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 31 30 29 28 27 2 3 4 5 6 7 8 9 A1 A2 A3 A4 A5 A6 A7 A8 1 19 VCC ADDR8 ADDR9 ADDR10 ADDR11 ADDR12 ADDR13 ADDR14 ADDR15 18 17 16 15 14 13 12 11 B1 B2 B3 B4 B5 B6 B7 B8 DIR G MM74HC245A VCC 20 42 41 40 39 38 37 36 35 U26 U11B 5 2 6 From Xilinx Page 4 4 6 74HC14 SW TACT-SPST-2 3 74HC14 17 51 52 5 C1 74HC08 26 VCC DONE RST VRL VRH VDD Decoupleing Caps needed VCC 1K 19 18 3 2 1uF IRQ XIRQ MODA MODB PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7 PD0 PD1 PD2 PD3 PD4 PD5 AS R/W E 9 10 11 12 13 14 15 16 D0 D1 D2 D3 D4 D5 D6 D7 D0 D1 D2 D3 D4 D5 D6 D7 20 21 22 23 24 25 3 4 7 8 13 14 17 18 11 1 D0 D1 D2 D3 D4 D5 D6 D7 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 21 23 24 25 26 1 2 3 4 5 6 7 8 9 10 22 27 20 28 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 D0 D1 D2 D3 D4 D5 D6 D7 11 12 13 15 16 17 18 19 OE WE CE VCC CY62256 VCC LE OE CD74HC373 U23 4 6 5 D0 D1 D2 D3 D4 D5 D6 D7 MC68HC11E0 2 3 4 5 6 7 8 9 1 19 4.7K SIP 20 VCC ADDR0 ADDR1 ADDR2 ADDR3 ADDR4 ADDR5 ADDR6 ADDR7 2 5 6 9 12 15 16 19 U34 ADDR0 ADDR1 ADDR2 ADDR3 ADDR4 ADDR5 ADDR6 ADDR7 ADDR8 ADDR9 ADDR10 ADDR11 ADDR12 ADDR13 ADDR14 ADDR15 11 A1 A2 A3 A4 A5 A6 A7 A8 B1 B2 B3 B4 B5 B6 B7 B8 18 17 16 15 14 13 12 11 DATA0 DATA1 DATA2 DATA3 DATA4 DATA5 DATA6 DATA7 DIR G MM74HC245A VCC 10 VCC 74HC14 11 /E 10 74HC14 U37 R15 RES 10 74HC14 VCC Sean 22 1 20 28 OE WE CE VCC AT28LV256 I/O0 I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7 G ND 11 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 14 10 9 8 7 6 5 4 3 25 24 21 23 2 26 27 11 12 13 15 16 17 18 19 Processor and Memory Wired and tested Serial Port Construction Sean Runs Code from EPROM Fully functional RAM New clock Current Status FPGA and EPROM U31 18 19 20 23 24 25 26 27 28 38 39 40 44 45 46 47 48 49 50 62 68 70 1 2 3 4 5 6 4 5 6 7 8 VCC 9 10 11 12 13 JTAG Conn. TDI TMS TCK D4/CFbar OE/RESETbar VCC TD0 D1 D3 D5 18 17 16 15 14 15 17 16 75 D6 CEba r G ND D7 CEO bar TDI TMS TCK TDO VCC GND CLK D2 Data (DO ) V CCO V CC U29 3 2 1 19 20 VCC33 VCC VCC 71 XC18V256 29 51 72 300 ohm 4.7K 73 35 57 32 30 34 I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O TDI(I/O) TMS( I/O) TCK( I/O) TDO( I/O) (I/O)WS/AO PGCK4(I/O)A1 (I/O)CS1/A2 (I/O)A3 (I/O)A4 (I/O)A5 (I/O)A6 (I/O)A7 (I/O)A8 (I/O)A9 (I/O)A10 (I/O)A11 (I/O)A12 (I/O)A13 (I/O)A14 SGCK1(I/O)A15 PGCK1(I/O)A16 (I/O)A17 DIN(I/O) SGCK2(I/O) SGCK3(I/O) SGCK4(I/O)DOUT DONE INIT(I/O) PROGRAM 56 58 59 61 65 67 69 77 78 79 80 81 82 83 84 3 4 5 6 7 8 9 10 13 14 53 41 55 CCLK PGCK2(I/O) PGCK3(I/O) MODE NC NC XCS10/LCC Sean I/O I/O I/O I/O I/O I/O I/O HDC LDC( I/O) I/O I/O 36 37 60 66 DONE To processor and memory page FPGA and EPROM Sean 1 1 1 0 1 0 Problems Encountered Sean Learning Curve Wire-wrap Issues B-scan for FPGA Xilinx project navigator link to Impact Power-Ground Short Inaccurate Part Specifications Labeling Division of Labor •Aaron Lyons •Software Development •Core Microprocessor •RC Car Test & Modification •Alex Henriquez •Core Microprocessor •Software Development •Sensors •Anders Fornberg •Sensors •RC Car Test Sean •Motor Control • Sean Groves • Power • Core Microprocessor • Motor Control • Shannon Lahr • Motor Control • Power • RC Car Test • Everyone • Documentation • Project/Deadline Management Lead for the task Milestone 1 Sean FPGA control of drive/steering and Chip Select Sampling from Sensors Interrupt Controller Dip Switches RS232 Communication Milestone 2 Sean Boot Monitor LCD Implementation Mounting Specifications LED/Audio Integration Subsystem Integration Multiple Mode Operation Future Concerns Sean Physical limitations that software can not cope with Tracking Speed of Sensors Board integrity during testing Low Speed Response Project Schedule Scheduale Sean Parts List/Cost Estimate Main Board Description Price Quantity Total -Processor MC68HC11 $0 1 $0 -EPROM -FPGA Fairchild 27C512 Spartan XCS10 $0 $0 1 2 $0 $0 $0 $25 $0.20 1 1 10 $0 $25 $2 $35 6 $210 -RAM Cypress 62258 -Board -Plastic Standoffs Sensors Front, Back, Side, Angle Devantech SRF04 Ranger Other Parts -RC Car Rustler by Traxxas $165 1 $165 -Battery Charger AC/DC Charger $40 1 $40 -Battery 7.2V Battery $15 2 $30 -Battery 9 V Battery $3 8 $24 -Plexi Glass $5 10 x 12 $5 -Metal $10 10 x 12 $10 -Metal Standoffs -Tether $1.70 ~$.10/ft 20 40ft $34.00 $4 Total Sean $548.60 QUESTIONS???