Solution Set 8 (Word format)

advertisement

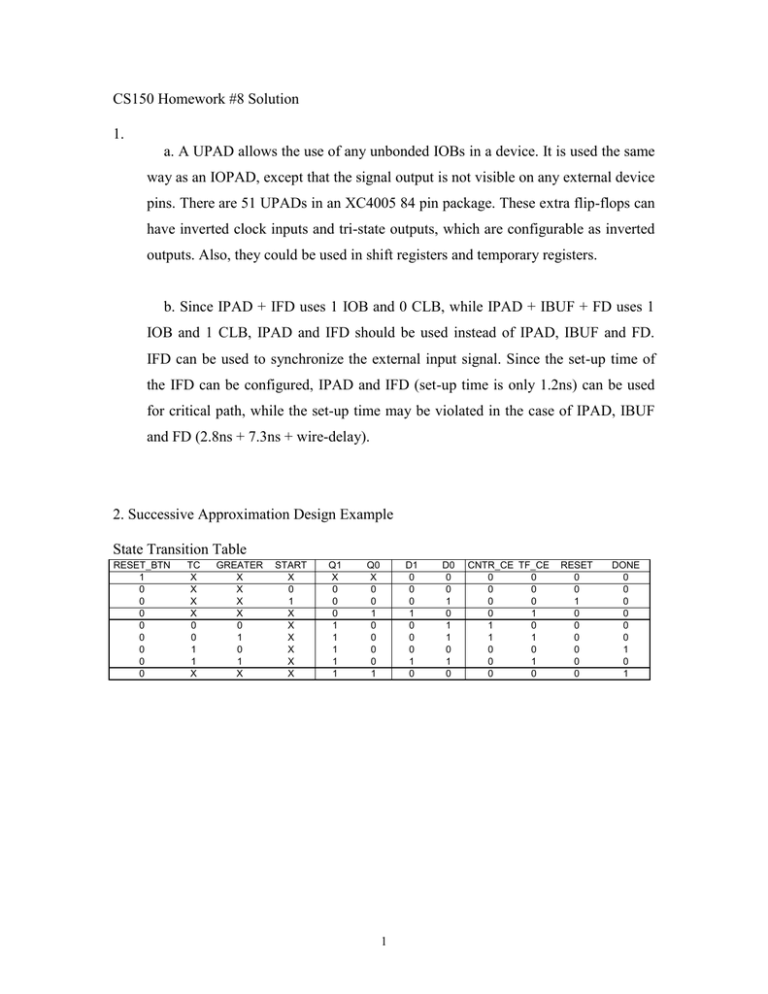

CS150 Homework #8 Solution 1. a. A UPAD allows the use of any unbonded IOBs in a device. It is used the same way as an IOPAD, except that the signal output is not visible on any external device pins. There are 51 UPADs in an XC4005 84 pin package. These extra flip-flops can have inverted clock inputs and tri-state outputs, which are configurable as inverted outputs. Also, they could be used in shift registers and temporary registers. b. Since IPAD + IFD uses 1 IOB and 0 CLB, while IPAD + IBUF + FD uses 1 IOB and 1 CLB, IPAD and IFD should be used instead of IPAD, IBUF and FD. IFD can be used to synchronize the external input signal. Since the set-up time of the IFD can be configured, IPAD and IFD (set-up time is only 1.2ns) can be used for critical path, while the set-up time may be violated in the case of IPAD, IBUF and FD (2.8ns + 7.3ns + wire-delay). 2. Successive Approximation Design Example State Transition Table RESET_BTN 1 0 0 0 0 0 0 0 0 TC X X X X 0 0 1 1 X GREATER X X X X 0 1 0 1 X START X 0 1 X X X X X X Q1 X 0 0 0 1 1 1 1 1 Q0 X 0 0 1 0 0 0 0 1 D1 0 0 0 1 0 0 0 1 0 1 D0 0 0 1 0 1 1 0 1 0 CNTR_CE TF_CE 0 0 0 0 0 0 0 1 1 0 1 1 0 0 0 1 0 0 RESET 0 0 1 0 0 0 0 0 0 DONE 0 0 0 0 0 0 1 0 1 2 Control FSM State Diagram RESET_BTN / START / / DONE IDLE S0 S3 GREATER TC / DONE START / RESET GREATER TC / TF_CE GREATER TC / CNTR_CE S1 / TF_CE S2 GREATER TC / TF_CE, CNTR_CE 3 4 5 3. ROM Based FSM ROM CONTENTS Addr 0 1 2 3 4 5 6 7 8 9 A B C D E F 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F INY.H 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 INX.H 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Q2.H 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Q1.H 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Q0.H 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 6 OUT 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 D2 0 0 0 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 D1 0 1 1 0 0 1 1 1 0 0 0 0 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 D0 1 0 1 0 1 0 1 1 0 0 0 1 0 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 State Diagram for ROM-based FSM INY INX/OUT INY INX/OUT S0 INY INX/OUT S1 INY INX/OUT INY INX/OUT S2 INY INX/OUT INY INX/OUT S3 INY INX/OUT INY INX/OUT INY INX/OUT S4 INY INX/OUT INY INX/OUT S5 INY INX/OUT INY INX/OUT INY/ OUT INY INX/OUT S6 INY INX/OUT 7 S7 This is a Mealey machine since both inputs and the present states determine the outputs. Timing Diagram CLOCK.H S7 S6 S4 S2 S3 S4 INY.H INX.H OUT.H 8 S2 S0 S1 S2 S0 S1