CALIFORNIA STATE UNIVERSITY, NORTHRIDGE Digital Datapath for an Image Acquisition System

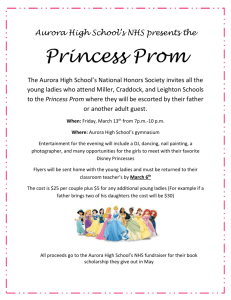

advertisement