ii iii iv

TABLE OF CONTENTS

CHAPTER

1

2

TITLE

DECLARATION

DEDICATION

ACKNOWLEDGEMENTS

ABSTRACT

ABSTRAK

TABLE OF CONTENTS

LIST OF TABLES

LIST OF FIGURES

LIST OF SYMBOLS

LIST OF ABBREVIATIONS

LIST OF APPENDICES

INTRODUCTION

1.1

Background

1.2

Problem Statement

1.3

Objective of Research

1.4

Scope of Study

1.5

Thesis Organization

1.6

Contribution of the thesis

LITRATURE REVIEW

2.1

Introduction

2.2

Active Inductor Circuit Topologies

2.3

Summary and Comparison

PAGE ii iii iv v vi vii x xi xvii xx xxii

1

1

2

4

5

6

7

10

10

14

36 vii

3

4 viii

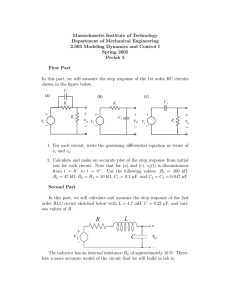

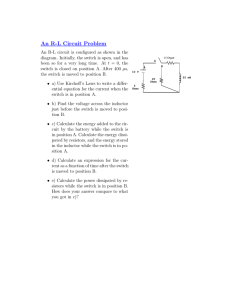

PROPOSED AI CIRCUIT

3.1

Research Methodology

3.2

Proposed First Active Inductor Circuit (AI1)

3.2.1 Introduction

3.2.2 Small signal Analysis of The Proposed

37

37

39

39

First Active Inductor

3.2.3 Quality Factor

40

46

3.2.4 Simulation Results 47

3.3

Proposed Second Active Inductor Circuit (AI2) 56

3.3.1 Small signal Analysis of the Proposed AI2 56

3.3.2 Simulation Results of the AI2

3.4

Proposed Third Active Inductor Circuit (AI3)

61

68

3.4.1 Small signal Analysis of the Proposed AI3 68

3.4.2 Simulation Results of the AI3 (DAI)

3.5

Summary

72

75

LNA DESIGN USING THE PEOPOSED

ACTIVE INDUCTORS 76

4.1

Reconfigurable LNA Design Based On First

Active Inductor (AI1) 76

4.1.1 Introduction

4.1.2 LNA Theories

76

78

4.1.2.1 Impedance matching

4.1.2.2 Thermal Noise

4.1.2.3 Noise Factor

4.1.2.4 Noise Factor in cascade system

4.1.2.5 S-parameters

4.1.3 Resistive Feedback LNA analysis

4.1.3.1 Gain Analysis

4.1.3.2 Noise Analysis

84

84

86

4.1.3.2.1 Thermal Noise due to the 86

4.1.3.2.2 Thermal Noise due to the 87

79

80

82

83

83

4.1.3.2.3 Thermal Noise due to the 88

4.1.3.2.4 Thermal Noise due to the 89

4.1.4 LNA Design Using the Proposed First

Active Inductor 90

4.1.5 Simulation Result of the LNA Using

the First Active Inductor

4.2

LNA Design Using the Second Active

Inductor(AI2)

4.2.1

Analysis of the Second LNA Using

93

102

the Second Active Inductor 102

4.2.2

Simulation Results of the Second LNA 105

4.3

Single-to-Differential-LNA Using the

108 Differential Active Inductor

4.3.1

Single-to-Differential LNA Analysis

4.3.2

S-to-D-LNA Simulation Results

4.4

Summary and Comparison

108

115

118

5 VCO DESIGN USING THE PROPOSED FIRST

ACTIVE INDUCTOR CIRCUIT 120

5.1

Introduction

5.2

Passive VCO

5.3

Active Inductor based VCO

5.4

Proposed Active Inductor based VCO

5.5

Simulation Results

5.6

Summary

120

120

122

124

125

133

6 CONCLUSION AND FUTURE WORK

6.1

Conclusion

6.2

Future Work

REFERENCES

Appendices A-B

135

135

137

139

147-148 ix

LIST OF TABLES

TABLE NO. TITLE

2.1 The summary of the AIs performances

3.1 AI circuit performance

3.2 Comparing the performance of proposed AI

with previously published AI

3.3 AI circuit performance

PAGE

36

56

56

68

Comparison of published AI circuit 3.4

3.5

3.6

AI circuit performance

Comparing the performance of the proposed

68

73

4.1

4.2

4.3

4.4

4.5

5.1

5.2

DAI with the recently published DAI

The summarized performance of the LNA

Comparison of published LNAs

Performance summary of the proposed LNA

Comparison of published CMOS LNAs

Comparison of published CMOS LNAs

Performance Summary of Wide-Tuning-Range

VCO

Comparison of published CMOS VCOs

74

101

102

107

107

118

133

133 x

2.9

2.10

2.11

2.12

2.13

2.14

2.15

2.16

2.17

2.18

2.19

2.20

LIST OF FIGURES

FIGURE NO. TITLE

2.1 Two port gyrator network

2.2

2.3

2.4

The gyrator network loaded with

Active inductor circuit using Op-Amp [1]

(a) Differential AI circuit reported in [14]

2.5

2.6

2.7

2.8

(b) RLC equivalent

Q factor plot[15]

Proposed DAI reported in [17]

The inductance and Q factor plot that is reported

in [14]

Improved AI circuit reported in [15]

Measured Q factor plot[17]

Proposed DAI circuit that is reported in [18]

Q factor and inductance plot[18]

AI circuit that is proposed in [19]

The inductance plot[19]

(a) Proposed AI that is reported in [20],

(b) RLC equivalent

(a) The Q factor (b) The inductance plot[20]

(a) AI circuit reported in [3, 4]

(b) Proposed AI circuit[21]

The inductance plot[21]

(a) proposed AI circuit with RLC equivalent

(b) Q factor and input impedance plot[22]

Proposed AI circuit reported in [23]

Proposed AI circuit reported in [25]

PAGE

11

12

13

14

23

23

24

25

26

27

28

19

20

20

22

22

16

17

17

18 xi

3.9

3.10

3.11

3.12

3.13

3.14

3.15

2.21

2.22

2.23

2.24

2.25

2.26

2.27

2.28

2.29

3.1

3.2

3.3

3.4

3.5

3.6

3.7

3.8

Proposed AI circuit reported in [26]

Input impedance plot for the proposed AI circuit[26]

Proposed AI circuit reported in [27]

The inductance and Q factor plot[27]

Proposed AI circuit reported in [28]

Inductance plot in strong inversion[28]

Inductance plot in weak inversion[28]

Proposed DAI reported in [29]

Proposed DAI's inductance plot[29]

Active inductor circuit design Flow Chart

Proposed Active Inductor Circuit

Small Signal equivalent circuit

RLC equivalent circuit

Simulated inductance plot

Q factor plot

The simulated inductance plot for = 1

The simulated Q factor Plot for different

configuration ( =13.5k

Ω )

The variation of real of input impedance (Z11)

versus R f

(from 2 k Ω to 12 k Ω )

The variation of imaginary of input impedance

versus R f

(from 2 k Ω to 12 k Ω )

The variation of real of input impedance (Z11) versus

R f

for =1.5 k Ω and R f

from 1 k Ω to 10 k Ω

The variation of imaginary of input impedance(Z11) versus R f

for =1.5 k Ω and R f

from 1 k Ω to 10 k Ω

Inductance plot for =1.5 k Ω and =13 k Ω

Q factor plot for =1.5 k Ω and =13 k Ω

Layout of the Active Inductor (a) With GSG Pad

(b) Without GSG Pad

33

33

35

35

39

41

29

30

31

31

32

41

45

48

48

50

50

51

52

53

53

54

54

55 xii

3.16

3.17

3.18

3.19

3.20

3.21

3.22

3.23

3.24

3.25

3.26

3.27

3.28

4.3

4.4

4.5

4.6

4.7

4.8

4.9

4.10

3.29

3.30

3.31

3.32

3.33

4.1

4.2

Active Inductor circuit

Small signal equivalent

RLC equivalent of AI

The simulated inductance of AI

Quality factor for the AI

Variation of input impedance ( ) by variation

of feedback resistor ( )

Active Inductor simulated inductance

The highest value of Quality factor plot

Variation of input impedance ( ) by varying the

feedback resistor ( ) at different DC biasing

Inductance plot for another configuration

( = 3.3 k Ω )

Q factor plot for another configuration( = 3.3 k Ω )

Variation of input impedance ( ) by variation of

feedback resistor ( ) for another configuration layout of the Proposed Active Inductor (a) With GSG

Pad (b) Without GSG Pad

Reconfigurable receiver architecture

Differential Active Inductor circuit

(a) Small signal equivalent (b) RLC Equivalent

Differential inductance plot

Quality factor plot

Reconfigurable LNA architecture

Dual standard LNA

Impedance matching condition

Inductive source degeneration LNA

Thermal noise model for resistor

Thermal noise model for MOSFET

Two- port network

Resistive feedback LNA

Small signal equivalent

Resistive feedback LNA with noise sources

57

57

60

61

62

62

63

64

64

65

65

66

67

79

80

81

82

82

84

85

86

69

70

70

73

74

77

78 xiii

4.18

4.19

4.20

4.21

4.22

4.23

4.24

4.11

4.12

4.13

4.14

4.15

4.16

4.17

4.32

4.33

4.34

4.35

4.36

4.25

4.26

4.27

4.28

4.29

4.30

4.31

LNA circuit

LNA circuit topology based on AI

Proposed complete LNA circuit

Variation of selected frequency band and S21

(Gain) versus

(b) Selecting frequency band by tuning

Variation of S21 versus (in simulation rfa1)

Variation of S11 versus

S12 of LNA versus

S22 of LNA versus

NF of LNA versus

NFmin of LNA versus

(a) Tunable PMOS resistance

Variation of S21 versus

Variation of S11 versus

S22 of LNA versus

NF of LNA versus

NFmin of LNA versus

LNA circuit layout

Cascode amplifier with input and output stage

impedance matching

LNA circuit

, , and of LNA

Noise Figure and Minimum Noise Figure of LNA

A Summary of published topologies of S-to-D-LNA:

(a) Common Source Common Gate (CSCG)

configuration; (b) CS amplifier with CSCG

balun;(c) differential with ac-grounded second

input terminals

S-to-D-LNA architecture

The proposed S-to-D-LNA circuit

-boosting technique with RC network

Schematic of the S-to-D-LNA circuit with the

103

104

106

106

109

110

112

114

98

99

99

100

100

101

96

97

97

98

94

94

95

95

90

91

93 xiv

4.37

4.38

4.39

4.40

5.1

5.2

5.3

5.4

5.5

5.6

5.7

5.8

5.9

5.10

5.11

5.12

5.13

5.14

5.15

external capacitor

S21 and S11 plot at 1.57 GHz

NFmin plot at 1.53 GHz

Variation of S21 with variation of from 1 fF

to 250 fF

S21, S11 and NFmin for =121 fF

Passive VCO

Active Inductor based VCO

Schematic of proposed LC-tank VCO based on AIs

VCO output frequency tuning with

VCO Output Power at 1.4 GHZ for =5 k Ω

Phase noise at 1.4 GHz for R f

= 5 k Ω

Output transient signal at 1.4 GHz (mV) for

R f

= 5 k Ω

Output power, phase noise and output transient

signal of the VCO at R f

=200k Ω (f=300 MHz)

Output power, phase noise and output transient

signal of the VCO at R f

=0.5k

Ω (f=2.37 GHZ)

VCO Output Power Variations according to R f variations

Phase noise Variations according to R f

variations

at 1 MHz offset

(a) Tunable PMOS resistance (b) Variation of

VCO output frequency by tuning V t

Output power, phase noise and output transient signal of the VCO at V t

=0.35 V (f=2.05 GHz)

Output power, phase noise and output transient signal of the VCO at V t

=1.25 V (f=0.275 GHz)

Variation of VCO output power for different

tuning voltage ( )

127

128

128

129

129

130

130

131

131

117

117

121

123

124

126

126

127

115

116

116 xv

5.16

5.17

Variation of Phase Noise for different tuning voltage ( ) at 1 MHz offset frequency

VCO circuit Layout

132

132 xvi

C

!

" dB dBc/Hz dBm f

#

$ fF

F g

% &

%

Hz

I

)

*

,,

-

*

,.

/

GHz

K

K

123 k Ω

LIST OF SYMBOLS

- Ampere

- Voltage Gain

- Capacitor

- Parallel Capacitance

- Transistor gate-source capacitance

- Decibel

- Phase noise unit

- Decibel of power referenced to one milliwatt

- Frequency

- Resonance frequency

- Femto Farad

- Noise factor

- Conductance

-

%

at

'(

=0V

- Output conductance

- Transconductance

- Hertz

- Current

- Input AC current

- Thermal noise of Load resistor

- Thermal noise of transistor

- Giga Hertz

- Boltzmans's constant

- gain of the VCO

- Kilo Ohm xvii

4

5

T t

V

V

77 v

9:

V

;

V

<9

V

9

V

=,:

>>>>

W nm pF

Q

R t

R s

!

L

MHz mV mW

M Ω nH nF

- Inductance

- Mega Hertz

- Milli volt

- Milli watt

- Mega Ohm

- Transistor Number i

- Nano-Henry

- Nano-Farad

- Nano-meter

- Pico-Farad

- Quality Factor

- Resistance

- Tuning Resistor

- Serial resistance

- Parallel resistance

- Feedback resistance

- Output resistance of transistor

- Scattering Parameters or S-parameters

- Output return loss

- power gain

- reverse isolation

- input return loss

- Temperature (Kelvin)

- Time

- Volt

- Voltage Supply

- Input AC voltage

- Tuning Voltage

- Bias voltage at node i

- Voltage at node i

- Output referred noise voltage

- Voltage noise

- Watt xviii

Γ

Ω

C

µm

µ A

∆ f

[Z]

W

;

/L

;

Y

Y in

Z in

B

B

&

γ

- Transistor width and length

- Admittance

- Input Admittance

- Input Impedance

- Angular frequency

- Resonance angular frequency

- Fitting parameter for the noise model

- Reflection Coefficient

- Ohm

- Pi

- Micro Meter

- Micro Ampere

- Noise bandwidth

- Impedance Matrix xix

NFmin

NMOS

NR

OTAs

PLL

PMOS

RF

AC

AI

BiCMOS

CD

CMOS

CS

DAI

DC

FFT

GPS

GSG

GSM

KCL

KVL

LAN

LNA

LO -

MOSFET -

NF -

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

LIST OF ABREVIATIONS

Alternative current

Active Inductor

Bipolar CMOS

Common Drain

Complementary Metal-Oxide-Semiconductor

Common Gate

Differential Active Inductor

Direct Current

Fast Fourier Transform

Global Positioning System

Ground-Signal-Ground

Global System for Mobile communications

Kirchhoff's Current Low

Kirchhoff's Voltage Low

Local Area Network

Low Noise Amplifier

Local Oscillator

Metal-Oxide-Semiconductor Field-Effect-Transistor

Noise Figure

Minimum Noise Figure

N-channel MOSFET

Negative Resistance

Operational Transconductance Amplifiers

Phase Locked Loop

P-channel MOSFET

Radio Frequency xx

RFIC

SiGe

SOC

VCO

WCDMA -

-

-

-

-

- WLAN

Radio Frequency Integrated Circuit

Silicon Germanium

System-On-a- Chip

Voltage-Controlled Oscillator

Wideband Code Division Multiple Access

Wireless Local Area Network xxi

xxii

B

LIST OF APPENDICES

TITLE APPENDIX

A Publications

Patents

PAGE

147

148