Pertemuan 12 Input/Output Matakuliah : H0344/Organisasi dan Arsitektur Komputer

advertisement

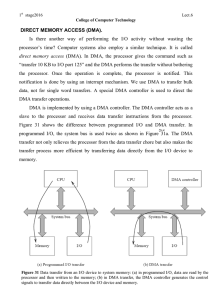

Matakuliah Tahun Versi : H0344/Organisasi dan Arsitektur Komputer : 2005 : 1/1 Pertemuan 12 Input/Output 1 Learning Outcomes Pada akhir pertemuan ini, diharapkan mahasiswa akan mampu : • Menjelaskan konsep dasar Input/Output 2 Outline Materi • • • • • • • External Devices I/O Modules Programmed I/O Interupt-Driven I/O Direct Memory Access I/O Channel and Processor The External Interface 3 Overview I/O module contains logic for performing a communication between the peripherals and the systems bus. The reasons why one does not connect peripherals directly to the system bus are as follows: 1. There is wide variety of peripherals with various methods of operation. 2. There is a difference between the data transfer rate of peripherals and that of the memory or processor. 3. Peripherals often use different data format and word lengths than the computer. 4 Overview Address lines Data lines System bus Control lines I/O module Links to peripheral devices 5 Overview I/O module has two major functions: 1. Interface to the processor and memory via the system bus or central switch . 2. Interface to one or more peripheral devices by tailored data links. 6 External devices We can classify external devices into three categories: 1. Human readable 2. Machine readable 3. Communication 7 External devices Block diagram of an external device Status signals to I/O module Data bits to and from I/O module Buffer Control logic Transducer Data (device-unique) to and from environment 8 I/O modules Module function The major functions or requirements for an I/O module fall into the following categories: 1. Control and timing 2. Processor communication 3. Device communication 4. Data buffering 5. Error detection 9 I/O modules Module structure Interface to system bus Interface to external devices Data registers Data lines Status/control registers Address lines Control lines I/O logic External device interface logic Data Status Control External device interface logic Data Status Control 10 Programmed I/O I/O to memory transfer through processor I/O to memory transfer No interrupts Use of interrupts Programmed I/O Interrupt driven I/O Direct memory access (DMA) 11 Programmed I/O Not ready Issue read command to I/O module Issue read command to I/O module Read status of I/O module Read status of I/O module Check status Error condition Check status Ready No Read word from I/O module Write word into memory Write word into memory Yes Do something else Interrupt I/O -> CPU No Issue read command to I/O module Read status of I/O module CPU -> DMA Do something else Interrupt DMA -> CPU Error condition Next instruction (c) Direct memory access Ready Read word from I/O module Done? CPU -> I/O I/O -> CPU CPU -> Memory Done? Yes Next instruction Next instruction (a) Programmed I/O (b) Interrupt driven I/O 12 Programmed I/O I/O Commands There are four types of I/O commands: 1. Control 2. Test 3. Read 4. Write 13 Programmed I/O I/O Instructions 7 I/O 6 5 Memory mapped 4 3 2 1 0 Keyboard input data register 516 7 6 5 4 3 2 1 0 Keyboard input status and control register 517 1 = ready 0 = busy Address 200 202 Instruction Set to 1 to start read Operan d Comment Load AC “1” Load accumulator Stored AC 517 Initiate keyboard read Load AC 571 Get status byte Branch if Sign = 0 202 Loop until ready Load AC 516 Load data byte 14 Programmed I/O I/O Instructions Isolated I/O Address Instruction Operand Comment 200 Load I/O 5 Initiate keyboard read 201 Test I/O 5 Check for completion Branch Not Ready In 201 5 Loop until complete Load data byte 15 Interrupt driven I/O Hardware Software Interrupt processing Device controller or other system hardware issue an interrupt Save remainder of process state information Processor finishes execution of current instruction Process interrupt Processor signals acknowledgment of interrupt Restore process state information Processor push PSW and PC onto control stack Restore old PSW and PC Processor loads new PC value based on interrupt 16 Interrupt driven I/O Interrupt processing T-M Y Control Stack Y N+1 Start Y+L Return Program counter T General register Interrupt service routine Y N+1 Control Stack Program counter T T-M T Y Y+L Start General register Interrupt service routine Y+L Return T-M Stack pointer User’s program Stack pointer Processor T-M N N+1 Main memory (a) Interrupt occurs after instruction at location N User’s program Processor T N N+1 Main memory (b) Return from interrupt 17 Interrupt driven I/O Design issue 1. Because there will almost invariably be multiple I/O module, how does the processor determine which device issued the interrupt? 2. If multiple interrupt have occurred, how does the processor decide which one to process? Four general categories of technique are in common use: 1. Multiple interrupt lines 2. Software poll 3. Daisy chain (hardware poll, vectored) 4. Bus arbitration (vectored) 18 Intel 82C59A Interrupt Controller Slave 8259A interrupt controller External device 00 External device 01 External device 07 IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7 INT Slave 8259A interrupt controller External device 08 External device 09 External device 15 IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7 Master 8259A interrupt controller INT Slave 8259A interrupt controller External device 56 External device 57 External device 63 IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7 IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7 INT 8086 processor INT INT 19 Intel 82C55A Programmable Peripheral Interface data buffer 8086 data bus power supply 8 8 bit internal bus 8 8 A 4 +5 volt ground CA 4 address A0 lines A1 read write reset chip select CB 8 8 Control logic control register B data buffers 20 Direct Memory Access Drawbacks of programmed and interrupt driven I/O 1. The I/O transfer rate is limited by the speed with which the processor can test and service a device. 2. The processor is tied up in managing an I/O transfer; a number of instructions must be executed for each I/O transfer. 21 Direct Memory Access Block diagram Data count Data lines Address lines DMA request DMA acknowledge Interrupt Read Write Data register Address register Control logic 22 Direct Memory Access DMA and interrupt breakpoints during an instruction cycle Instruction cycle Processor cycle Processor cycle Processor cycle Processor cycle Processor cycle Processor cycle Fetch instruction Decode instruction Fetch operand Execute instruction Store result Process interrupt DMA breakpoints DMA breakpoints 23 Direct Memory Access Alternative DMA configuration Processor DMA I/O I/O Memory (a) Single-bus, detached DMA Processor DMA DMA Memory I/O I/O I/O (b) Single-bus, integrated DMA-I/O System bus Processor DMA Memory I/O bus I/O I/O (c) I/O bus I/O 24 Direct Memory Access The evolution of the I/O function 1. The CPU directly controls a peripheral device. 2. A controller or I/O module is added. The CPU uses programmed I/O without interrupts. 3. The same configuration as in step 2 is used, but now interrupts are employed. 4. The I/O module is given direct access to memory via DMA. 5. The I/O module is enhanced to become a processor in its own right, with a specialized instruction set tailored for I/O. 6. The I/O module has a local memory of its own and is, in fact, a computer in its own right. 25 Direct Memory Access Data and address channel to main memory n Selector channel Control signal path to CPU I/O controller I/O controller (a) Selector Data and address channel to main memory n Multiplexor channel Control signal path to CPU I/O controller I/O channel architecture I/O controller I/O controller I/O controller (b) Multiplexor 26 The external interface Type of interface One major characteristic of the interface is whether it is serial or parallel. The I/O module must engage in a dialogue with the peripheral. In general, the dialogue for a write operation is as follows: 1. The I/O module sends a control signal requesting permission to send data. 2. The peripheral acknowledges the request. 3. The I/O module transfers data. 4. The peripheral acknowledges receipt of the data. Key to the operation of an I/O module is an internal buffer that can store data being passed between the peripheral and the rest of the system. This buffer allows the I/O module to compensate for the differences in speed between the system bus and its external lines. 27 The external interface Point to point and multipoint configuration The connection between an I/O module in a computer system and external devices can be either point to point or multipoint. 28