Generating Deliverables

for HardCopy Devices

October 2002, ver. 1.0

Introduction

Application Note 276

HardCopy™ device implementation hinges on the delivery of a

comprehensive set of FPGA design files to Altera. This application note

describes the process to generate and check these deliverables before your

design is submitted to Altera for migration. This process uses the

Quartus® II software version 2.1 and the HardCopy Passport version 2.0

utility software.

Generating deliverables for Altera® HardCopy devices includes the

following simple steps, all of which will be discussed in this document:

f

Software

Requirements

1.

Run the Design Assistant tool

2.

Ensure that the device’s timing constraints are complete

3.

Run the HardCopy Passport utility software

4.

Archive project files for delivery to Altera

For more information on HardCopy devices, refer to the HardCopy Devices

for APEX 20K Conversion Data Sheet on the Altera web site

(www.altera.com).

To generate the required output files correctly, you must use the

Quartus II software version 2.1. Additionally, you must run the

HardCopy Passport stand-alone utility prior to submitting your FPGA

design to Altera for migration. The HardCopy Passport utility (which

replaces the paper format design questionnaire) outputs the needed

information about the characteristics and design methodology used in

creating your FPGA design.

1

Altera Corporation

A-AN-276-1.0

The HardCopy Passport utility is a Windows executable file that

is available from the Altera web site at:

www.altera.com/products/devices/hardcopy/utilities/hrddesign_utilities.html.

1

AN 276: Generating Deliverables for HardCopy Devices

List of

Deliverables

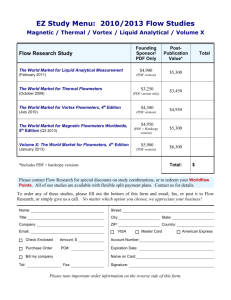

Table 1 shows the complete list of deliverables needed for a HardCopy

device implementation.

Table 1. Files Needed for HardCopy Implementation

File

Description

From <Quartus II Project Directory>\

<project_name>.sof

SRAM object file

<project_name>.csf.rpt

Compilation report file

<project_name>.pin

Pin list for the design

<project_name>.esf

Entity settings file

<project_name>.psf

Project settings file

*.qar

Quartus archive file

From <Quartus II Project Directory>\HardCopy\

<project_name>_hcpy.vo

Verilog ATOM netlist for use with PrimeTime

<project_name>_hcpy_v.sdo

Post-layout FPGA timing data

<project_name>_cpld.datasheet

Summary of FPGA I/O performance

<project_name>_target.datasheet

Summary of target I/O performance

<project_name>_pt_hcpy_v.tcl

Timing constraints with logical port names

<project_name>rba_pt_hcpy_v.tcl

Timing constraints with physical port names

From <HardCopy Passport Output Files Directory>\

*.txt

Generating

Design files

Text output file generated by Passport

All the required design information files are generated automatically as a

part of the normal Quartus II compilation process. There are additional

HardCopy-specific files that need to be generated through the Quartus II

software. Assuming a full compile has already been completed, you can

run Start Design Assistant (Processing menu).

1

For more information on the Quartus II Design Assistant tool,

refer to the Quartus II Software Overview page on the Altera

web site (www.altera.com).

Carefully check the Design Assistant results; any critical rules that are

violated will probably need to be fixed. High and medium severity

violations will need to be reviewed by the Altera HardCopy Design

Center. Figure 1 shows a typical set of results generated by the Design

Assistant.

2

Altera Corporation

AN 276: Generating Deliverables for HardCopy Devices

Figure 1. Results Generated from HardCopy Design Assistant

It is also possible to run the Design Assistant during the compile process

(see Figure 2). In the Compiler Settings dialog box (Tools menu), select

the Design Assistant tab, and then alter the fields according to your

specifications. Check “Run Design Assistant during compilation” if

required.

Altera Corporation

3

AN 276: Generating Deliverables for HardCopy Devices

Figure 2. Compiler Settings Dialog Box

After ensuring that the Design Assistant results are satisfactory, generate

the HardCopy timing constraint files. This is done through the

Assignment Organizer (Tools menu), and by setting global project timing

requirements (Project menu), as described below.

Global Project Settings

For FPGA designs, global timing requirements such as tSU, tCO, tH, and

tPD should be set for all I/O pins in the design through Timing Settings

(Project menu). The clock settings should also be specified here. Figure 3

shows the Timing Settings dialog boxes.

4

Altera Corporation

AN 276: Generating Deliverables for HardCopy Devices

Figure 3. Timing Settings

Once you have defined all the clocks in the design, specify the node in the

design that the clock definition points to. Use the Assignment Organizer

(Tools menu). The clock node will be either a primary input pin, a PLL

output pin, or an internal signal (e.g., register output pin).

In the Quartus II software, use the HardCopy Settings (Project menu) to

specify project-wide minimum timing requirements for outputs that are

driven by on-chip registers (tCO) in addition to minimum combinatorial

timing from primary input pins to primary output pins (tPD). Figure 4

shows the HardCopy Settings dialog box. The clock jitter of the external

clock source can also be specified here.

1

Altera Corporation

These settings will have no effect on the FPGA compile results

but are needed to ensure the HardCopy implementation meets

the system timing performance requirements.

5

AN 276: Generating Deliverables for HardCopy Devices

Figure 4. HardCopy Setting Dialog Box

Pin-Specific Timing Assignments

You can use the Assignment Organizer (Tools menu), shown in Figure 5,

to override the project-wide settings for specific I/O pins or clocks. Apply

any timing constraints that are necessary, (e.g., tSU, external input delay,

etc.). You can also specify pin-specific minimum tCO assignments for

HardCopy devices.

Figure 5. Assignment Organizer

6

Altera Corporation

AN 276: Generating Deliverables for HardCopy Devices

HardCopy timing constraints should meet the following requirements:

■

■

■

■

They should be a superset of the FPGA timing constraints, so any

timing constraints missed in the FPGA design must be added. If they

are unimportant (e.g., a pin that is static because it is tied off outside

the device), then a default timing constraint will be applied on the

pin, and a warning will be generated. Any minimum timing

requirements that were not specified for the FPGA must be specified

before HardCopy implementation. This is particularly important,

because signals typically are much faster in HardCopy devices

compared to FPGAs.

They should be consistent with FPGA timing constraints.

They should be achievable in the FPGA. Altera expects the FPGA to

meet the timing constraints before the HardCopy device

implementation commences. If the constraints are too stringent for

HardCopy devices, then the implementation may not be possible, or,

it may take longer to complete.

They should be complete; there should be no unconstrained pins or

unspecified clock domains.

Once you are satisfied that all the timing constraints have been applied,

run the Quartus Timing Analyzer by selecting Start Timing Analysis

(Processing menu). Do not re-compile the design when the Quartus II

software tells you that source or design files have changed. (Click No

when asked “Do you want to recompile before starting the timing

analysis?”)

Running the timing analysis ensures that all of the newly added timing

constraints are propagated into the Quartus II database. Once the timing

analysis is completed, generate the timing files required for HardCopy

implementation by selecting Generate HardCopy Files (Processing

menu).

All of the timing constraint files that are needed for HardCopy

implementation will be placed in a new sub-directory in the Quartus II

project directory called hardcopy. Figure 6 shows the timing constraint

files that should appear in the hardcopy directory.

Altera Corporation

7

AN 276: Generating Deliverables for HardCopy Devices

Figure 6. Timing Constraints Output Files

File Warnings or Errors

One way to check the timing constraints is to look at the file

<design_name>_target.datasheet. This is a text file that contains a list of

required I/O timing for the design. Any errors in this file will need to be

fixed. Any I/O pin that was not constrained will be flagged with a

warning message, as shown in Figure 7.

8

Altera Corporation

AN 276: Generating Deliverables for HardCopy Devices

Figure 7. Required I/O Timing List

Arc type

From

To

Value

SETUP

clk5

b1

4.00

SETUP

clk5

b3

3.00

SETUP

clk5

a7

7.50

# WARNING : The required setup time from a6 to clk5 is not set. The default value

(99.99) is used.

SETUP

clk5

a6

99.99

SETUP

clk5

b5

4.00

SETUP

clk5

b7

4.00

SETUP

clk5

b6

4.00

HOLD

clk5

b1

1.00

HOLD

clk5

b3

0.00

HOLD

clk5

a7

-1.00

# WARNING : The required hold time from a6 to clk5 is not set. The default value

(0.00) is used.

HOLD

clk5

a6

0.00

HOLD

clk5

b5

0.00

HOLD

clk5

b7

0.00

HOLD

clk5

b6

0.00

DELAY

clk5

out8

11.00

DELAY

clk5

out9

11.00

DELAY

clk5

out10

11.00

# WARNING : The required clock-to-output time from clk5 to out15 is not set. The

default value (99.99) is used.

DELAY

clk5

out15

99.99

DELAY

clk5

out11

8.00

DELAY

clk5

out12

11.00

Also, review the SETUP, HOLD, and DELAY values in this file to check if

they meet the design requirements.

Once you are satisfied with the target datasheet file, check the

<design_name>_pt_hcpy_v.tcl file for errors or warnings and fix as noted

above. This file describes the same information, but in a different format.

In particular, check that the clock definitions and timing exceptions, such

as false-paths and multi-cycle paths, are as expected.

You can also ensure the constraints are complete by reading the design

and the constraint file into Synopsys’ PrimeTime static timing analysis

tool and check using the check_timing command. This can be done as

follows: pt_shell> read <design_name>_ pt_hcpy_v.tcl.

Altera Corporation

9

AN 276: Generating Deliverables for HardCopy Devices

In PrimeTime, the check_timing command will generate a report detailing

if any parts of the design are not constrained. For example, if some output

pins in a design are not constrained, the tool provides a warning message

giving the number of output pins that are not constrained for maximum

delay. Then a list of those output pins is given.

Editing the Constraint Files

The contents of timing constraint files should not be changed manually

because a hand edit may cause the files to become inconsistent with each

other. Instead, the changes should be made through the Assignment

Organizer (Tools menu) and the Timing Settings (Project menu) tools.

The files should be regenerated using the method described in

“Generating Design files” on page 2.

After reviewing all of the HardCopy timing files, you are ready to use the

HardCopy Passport utility.

Running

HardCopy

Passport

Once launched, the Passport utility launches a wizard that asks a series of

questions corresponding to the design. Choose to save the results as an

ASCII text file. This text file should be provided as one of the deliverables

for HardCopy implementation.

Figure 8 shows one of the panes of HardCopy Passport wizard.

10

Altera Corporation

AN 276: Generating Deliverables for HardCopy Devices

Figure 8. HardCopy Passport

Archive HardCopy Files

Once finished with the HardCopy Passport utility, archive the design files

that are required for the HardCopy implementation by selecting Archive

Project (Project menu). Check the “Include files for HardCopy

conversion,” then click Add/Remove Files. Ensure that the output text file

from Passport is included in the archive, in addition to all the files listed

in Table 1 on page 2.

Figure 9. Archive Project

Altera Corporation

11

AN 276: Generating Deliverables for HardCopy Devices

When finished, click OK and a Quartus Archived File (.qar) will be

generated. By default this file is located in the Quartus II project directory;

however, you can direct the software to a specific location by pressing the

browse button (...) on the right side of this window to bring up a standard

file dialog box. This QAR file should be sent to Altera for the HardCopy

implementation to commence.

Conclusion

101 Innovation Drive

San Jose, CA 95134

(408) 544-7000

http://www.altera.com

Applications Hotline:

(800) 800-EPLD

Literature Services:

lit_req@altera.com

12

HardCopy devices provide the fastest way to convert high-density FPGA

designs to a no-risk, low-cost device. The migration process is fully

automated, and customer involvement is limited, requiring only

generating a few Quartus II software-based output files. After delivery of

these output files, apart from approval of the prototype, Altera carries out

all of the steps in the migration process.

Copyright © 2002 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the

stylized Altera logo, specific device designations, and all other words and logos that are identified as

trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera

Corporation in the U.S. and other countries. All other product or service names are the property of their

respective holders. Altera products are protected under numerous U.S. and foreign patents and pending

applications, maskwork rights, and copyrights. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard

warranty, but reserves the right to make changes to any products and services at any time

without notice. Altera assumes no responsibility or liability arising out of the application

or use of any information, product, or service described herein except as expressly agreed

to in writing by Altera Corporation. Altera customers are advised to obtain the latest

version of device specifications before relying on any published information and before

placing orders for products or services

Altera Corporation