A Laboratory Manual for the SPARC

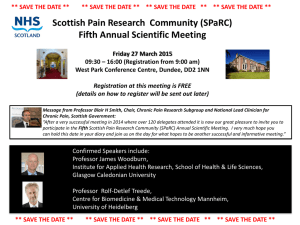

advertisement