Improving Effective Bandwidth through Compiler Enhancement of Global and Dynamic Cache Reuse

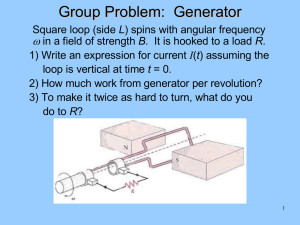

advertisement

RICE UNIVERSITY

Improving Effective Bandwidth through

Compiler Enhancement of

Global and Dynamic Cache Reuse

by

Chen Ding

A Thesis Submitted

in Partial Fulfillment of the

Requirements for the Degree

Doctor of Philosophy

Approved, Thesis Committee:

Ken Kennedy

Ann and John Doerr Professor, Chair

Computer Science

Keith Cooper

Associate Professor

Computer Science

Danny C. Sorensen

Professor

Computational and Applied Mathematics

Alan Cox

Associate Professor

Computer Science

John Mellor-Crummey

Senior Faculty Fellow

Computer Science

Houston, Texas

January 14, 2000

Improving Effective Bandwidth through

Compiler Enhancement of

Global and Dynamic Cache Reuse

Chen Ding

Abstract

While CPU speed has been improved by a factor of 6400 over the past twenty years,

memory bandwidth has increased by a factor of only 139 during the same period.

Consequently, on modern machines the limited data supply simply cannot keep a

CPU busy, and applications often utilize only a few percent of peak CPU performance.

The hardware solution, which provides layers of high-bandwidth data cache, is not

effective for large and complex applications primarily for two reasons: far-separated

data reuse and large-stride data access. The first repeats unnecessary transfer and

the second communicates useless data. Both waste memory bandwidth.

This dissertation pursues a software remedy. It investigates the potential for

compiler optimizations to alter program behavior and reduce its memory bandwidth

consumption. To this end, this research has studied a two-step transformation strategy: first fuse computations on the same data and then group data used by the same

computation. Existing techniques such as loop blocking can be viewed as an application of this strategy within a single loop nest. In order to carry out this strategy

to its full extent, this research has developed a set of compiler transformations that

perform computation fusion and data grouping over the whole program and during

the entire execution. The major new techniques and their unique contributions are

Maximal loop fusion: an algorithm that achieves maximal fusion among all

program statements and bounded reuse distance within a fused loop.

Inter-array data regrouping: the first to selectively group global data structures and to do so with guaranteed profitability and compile-time optimality.

Locality grouping and dynamic packing: the first set of compiler-inserted

and compiler-optimized computation and data transformations at run time.

These optimizations have been implemented in a research compiler and evaluated

on real-world applications on SGI Origin2000. The result shows that, on average,

the new strategy eliminates 41% of memory loads in regular applications and 63% in

irregular and dynamic programs. As a result, the overall execution time is shortened

by 12% to 77%.

In addition to compiler optimizations, this research has developed a performance

model and designed a performance tool. The former allows precise measurement

of the memory bandwidth bottleneck; the latter enables effective user tuning and

accurate performance prediction for large applications: neither goal was achieved

before this thesis.

Acknowledgments

I wish to thank my advisor, Ken Kennedy, for his inspiration, technical direction and

material support. Without him this dissertation would not be possible. I want to

thank my other committee members, Keith Cooper, John Mellor-Crummey, Alan Cox,

and Danny Sorensen, for their interest and help. Sarita Adve helped with my proposal.

I also thank Ellen Butler for always reserving me a slot in Ken’s busy schedule. The

implementation of my work was based on the D System, an infrastructure project led

by John Mellor-Curmmey (and in part by Vikram Adve before his leave). I heavily

used the scalar compiler framework put together by Nat Macintosh. The D System

also contains components from previous compilers built by generations of graduate

students.

I am very fortunate to study in a small department with leading researchers working in a close environment and in the same wonderful building. The professors and

students of other groups not only give superb teaching but also are always ready to

help. I thank in particular the language, scalar compiler, architecture and system

group. My work was also helped by Nathaniel Dean and William Cook of computational mathematics department. My writing was significantly improved by a seminar

taught by Jan Hewitt. In addition, I thank Ron Goldman for his valuable lunch-time

advice and my officemate Dejan Mircevski for helping me on everything I asked. The

financial support for my study came from Rice University, DARPA, and Compaq

Corporation.

I received my M.S. degree from Michigan Tech., where my former advisors Phil

Sweany and Steve Carr helped me to build a solid foundation for my research career. I

thank also other outside researchers for their help especially Kathryn Knobe, Kathryn

McKinley, Wei Li, and Chau-Wen Tseng.

This dissertation is dedicated to my family: my dear wife Linlin, my parents

Shengyao Ding and Ruizhe Liu, and my brother Rui, for the never-ending love, support, and encouragement. I always remember what my father told me: “There are

mountains after mountains and sky outside sky.”

v

Contents

Abstract

Acknowledgments

List of Illustrations

ii

iv

viii

1 Introduction

1.0

1.1

1.2

1.3

1.4

1

Thesis . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Problem of Memory Performance . . . . . . . . . . . . . .

1.1.0 Definitions . . . . . . . . . . . . . . . . . . . . . . .

1.1.1 Conflicting Trends of Software and Hardware . . .

1.1.2 Memory Bandwidth Bottleneck . . . . . . . . . . .

Solution through Cache Reuse . . . . . . . . . . . . . . . .

1.2.1 Two-Step Strategy of Cache Reuse . . . . . . . . .

1.2.2 The Need for Compiler Automation . . . . . . . . .

1.2.3 A Unified Compiler Strategy . . . . . . . . . . . . .

Related Work . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.1 Complementary Techniques . . . . . . . . . . . . .

1.3.2 Global and Dynamic Optimizations . . . . . . . . .

1.3.3 Performance Model and Tool for Memory Hierarchy

1.3.4 Summary of Limitations . . . . . . . . . . . . . . .

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

2 Global Computation Fusion

2.1

2.2

2.3

Introduction . . . . . . . . . . . . . . . .

Analysis of Data Reuse . . . . . . . . . .

2.2.1 Reuse Distance . . . . . . . . . .

2.2.2 Reuse-Driven Execution . . . . .

An Algorithm for Maximal Loop Fusion

2.3.1 Single-Level Fusion . . . . . . . .

2.3.2 Properties . . . . . . . . . . . . .

1

2

2

3

5

8

9

12

14

15

16

17

23

24

25

26

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

26

27

27

27

30

33

35

vi

2.4

2.5

2.6

2.3.3 Multi-level Fusion . . . . . . . . . . . . . .

Optimal Loop Fusion . . . . . . . . . . . . . . . .

2.4.1 Loop Fusion for Minimal Reuse Distance .

2.4.2 Loop Fusion for Minimal Data Sharing . .

2.4.3 An Open Question . . . . . . . . . . . . .

Advanced Optimizations Enabled by Loop Fusion

2.5.1 Storage Reduction . . . . . . . . . . . . .

2.5.2 Store Elimination . . . . . . . . . . . . . .

Summary . . . . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

3 Global Data Regrouping

3.1

3.2

3.3

3.4

3.5

Introduction . . . . . . . . . . . . . . . . . .

Program Analysis . . . . . . . . . . . . . . .

Regrouping Algorithm . . . . . . . . . . . .

3.3.1 One-Level Regrouping . . . . . . . .

3.3.2 Optimality . . . . . . . . . . . . . . .

3.3.3 Multi-level Regrouping . . . . . . . .

Extensions . . . . . . . . . . . . . . . . . . .

3.4.1 Allowing Useless Data . . . . . . . .

3.4.2 Allowing Dynamic Data Regrouping

3.4.3 Minimizing Data Writebacks . . . . .

Summary . . . . . . . . . . . . . . . . . . .

53

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

4 Run-time Cache-reuse Optimizations

4.1

4.2

4.3

4.4

37

38

38

41

47

48

48

50

51

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . .

Locality Grouping and Data Packing . . . . . . . . . . . .

4.2.1 Locality Grouping . . . . . . . . . . . . . . . . . .

4.2.2 Dynamic Data Packing . . . . . . . . . . . . . . . .

4.2.3 Combining Computation and Data Transformation

Compiler Support for Dynamic Data Packing . . . . . . .

4.3.1 Packing and Packing Optimizations . . . . . . . . .

4.3.2 Compiler Analysis and Instrumentation . . . . . . .

4.3.3 Extensions to Fully Automatic Packing . . . . . . .

Summary . . . . . . . . . . . . . . . . . . . . . . . . . . .

53

54

56

56

58

60

61

63

64

64

65

67

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

67

68

68

70

74

75

75

78

81

81

vii

5 Performance Tuning and Prediction

5.1

5.2

5.3

5.4

5.5

Introduction . . . . . . . . . . . . . . . .

Bandwidth-based Performance Tool . . .

5.2.1 Data Analysis . . . . . . . . . . .

5.2.2 Integration with Compiler . . . .

Performance Tuning and Prediction . . .

Extensions to More Accurate Estimation

Summary . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

83

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

6 Evaluation

6.1

6.2

6.3

6.4

6.5

6.6

Implementation . . . . . . . . . . . . . . . . .

6.1.1 Maximal Loop Fusion . . . . . . . . .

6.1.2 Inter-array Data Regrouping . . . . . .

6.1.3 Data Packing and Its Optimizations . .

Experimental Design . . . . . . . . . . . . . .

Effect on Regular Applications . . . . . . . . .

6.3.1 Applications . . . . . . . . . . . . . . .

6.3.2 Transformations Applied . . . . . . . .

6.3.3 Effect of Transformations . . . . . . .

Effect on Irregular and Dynamic Applications

6.4.1 Applications . . . . . . . . . . . . . . .

6.4.2 Transformations Applied . . . . . . . .

6.4.3 Effect of Transformations . . . . . . .

Effect of Performance Tuning and Predication

Summary . . . . . . . . . . . . . . . . . . . .

7 Conclusions

7.1

7.2

7.3

83

84

84

85

86

87

88

90

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

90

90

91

92

92

93

94

94

94

99

99

100

102

105

109

112

Compiler Optimizations for Cache Reuse . . . . . . . . . . . . . . . . 112

Future Work . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Final Remarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Bibliography

118

viii

Illustrations

1.1

1.2

1.3

1.4

1.5

1.6

Comparison between program and machine balance . . . . . . . . .

Ratios of bandwidth demand to its supply . . . . . . . . . . . . . .

Example of global cache reuse . . . . . . . . . . . . . . . . . . . . .

Example of dynamic cache reuse . . . . . . . . . . . . . . . . . . . .

Comparison among hardware/OS, programmers and compilers . . .

The overall compiler strategy for maximizing memory performance .

.

.

.

.

.

.

6

7

10

12

13

14

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.9

2.10

2.11

2.12

2.13

Example reuse distances . . . . . . . . . .

Algorithm for reuse-driven execution . . .

Effect of reuse-driven execution (I) . . . .

Effect of reuse-driven execution (II) . . . .

Examples of loop fusion . . . . . . . . . .

Assumptions on the input program . . . .

Algorithm for one-level fusion . . . . . . .

Algorithm for multi-level fusion . . . . . .

Example of bandwidth-minimal loop fusion

Minimal-cut algorithm for a hyper-graph .

Array shrinking and peeling . . . . . . . .

Store elimination . . . . . . . . . . . . . .

Effect of store elimination . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

27

29

30

31

32

33

34

39

43

46

49

50

51

3.1

3.2

3.3

3.4

3.5

Example of inter-array data regrouping . . . . . . . . . . . .

Computation phases of a hydrodynamics simulation program

Example of multi-level data regrouping . . . . . . . . . . . .

Algorithm for multi-level data regrouping . . . . . . . . . . .

Examples of extending data regrouping . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

54

56

61

62

63

4.1

Example of locality grouping . . . . . . . . . . . . . . . . . . . . . . .

69

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

ix

4.2

4.3

4.4

4.5

4.6

4.7

4.8

4.9

4.10

4.11

Effect of locality grouping . . . . . . . . . . . . . . . .

Example of data packing . . . . . . . . . . . . . . . . .

Algorithm of consecutive data packing . . . . . . . . .

Moldyn and Mesh, on 2K and 4K cache . . . . . . . . .

Mesh after locality grouping . . . . . . . . . . . . . . .

Moldyn kernel with a packing directive . . . . . . . . .

Moldyn kernel after data packing . . . . . . . . . . . .

Moldyn kernel after packing optimizations . . . . . . .

Primitive packing groups in Moldyn . . . . . . . . . . .

Compiler indirection analysis and packing optimization

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

69

70

71

73

75

76

77

78

79

80

5.1

Structure of the performance tool . . . . . . . . . . . . . . . . . . . .

85

6.1

6.2

6.3

6.4

6.5

6.6

6.7

6.8

6.9

6.10

6.11

Descriptions of Regular applications . . . . . . . . . . . . . . . .

Effect of transformations on regular applications . . . . . . . . .

Reuse distances of NAS/SP after maximal fusion . . . . . . . .

Descriptions of irregular and dynamic applications . . . . . . . .

Input sizes of irregular and dynamic applications . . . . . . . .

Transformations applied to irregular and dynamic applications .

Effect of transformations on irregular and dynamic applications

Effect of compiler optimizations for data packing . . . . . . . .

Memory bandwidth utilization of NAS/SP . . . . . . . . . . . .

Actual and predicted execution time . . . . . . . . . . . . . . .

Actual and predicted data transfer . . . . . . . . . . . . . . . .

7.1

Summary of evaluation results . . . . . . . . . . . . . . . . . . . . . . 114

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

94

95

99

100

100

101

103

105

106

108

109

1

Chapter 1

Introduction

“In science there is only Physics; all the rest is stamp collecting” – Ernest

Rutherford (1871-1937)

1.0

Thesis

At the dawn of the 21st century, the computing world is witnessing two powerful

but diverging trends of hardware and software. On the hardware side, single-chip

microprocessors have become the dominant platform for most applications simply

because of their tremendous computing power, which has increased by an astonishing

6400 times in the past twenty years. However, in sharp contrast to the rapid on-chip

improvement is the much slower rate of growth for off-chip memory bandwidth, which

has increased by merely 139 times over the same period of time. To close the memory

gap, all modern machines provide high-bandwidth on-chip data caches in the hope

that most data can be cached so that applications can largely avoid direct access to

memory.

Although caches have been successful for programs with small data sets and simple access patterns, their effectiveness has become increasingly problematic as the

software community has been relentlessly pushing into ever larger and more complex

systems. Not only do today’s programs employ a massive amount of data that is far

too large to fit in cache, they also access memory in a complex and dynamically changing manner that leads to extremely poor utilization of the available cache resource.

The problem of poor cache utilization is further compounded by the use of moduleor component-based programming styles that fragment both computation and data

that could be otherwise cached together. As a result of the poor cache utilization and

consequently poor memory performance, many applications can achieve only a few

percent of peak CPU performance on modern machines, leaving room for a potential

improvement of an order of magnitude if only caches could be better utilized.

2

The purpose of this thesis is to bridge the diverging trends of software and hardware by developing a compiler strategy that automatically transforms programs to

fully utilize machine cache. Specifically, this work demonstrates that

Global and run-time transformations can substantially improve the

overall performance of large, dynamic applications on machines

built from modern microprocessors; furthermore, these transformations can be automated and combined into a coherent compiler strategy.

The rest of this chapter first explains the problem of memory bottleneck and the

solution of cache reuse. Then it presents the overall compiler strategy for maximizing

cache reuse and compares this strategy with previous work. The succeeding chapters

will then flesh out the various components of the new compiler strategy.

1.1

Problem of Memory Performance

The problem of memory performance is rooted in the diverging trends of hardware

and software, in particular in the growing mismatch between the insufficient memory bandwidth supplied by machines and the massive memory transfer demanded

by applications. This section first defines a few key concepts of memory hierarchy.

The main part then studies the fundamental balance between computation and data

transfer on computing systems, formulates a performance model based on the concept of balance, and finally uses the model to identify the performance bottleneck on

modern machines.

1.1.0

Definitions

All modern machines built from microprocessors have data transferred through several

levels of storage. The closest to CPU is a set of registers, then one or more levels

of cache, and finally the main memory. This layered memory organization is called

memory hierarchy.

Memory bandwidth is the data bandwidth between CPU and main memory, that is,

how much data is communicated between them in each second. The communication is

two-way: data is fetched into CPU through memory reads and sent back to memory by

memory writebacks. The memory bandwidth of a program is called effective memory

bandwidth, which is the number of memory reads and writebacks a program performs

3

in each second. Since CPU and main memory are on different computer chips, the

effective memory bandwidth of a program is constrained by the physical memory

bandwidth of a machine, which is the cross-chip or off-chip hardware bandwidth

between CPU and main memory.

Cache is a data buffer between CPU and main memory. It serves memory requests for the buffered data without accessing main memory. Cache is organized as a

collection of non-unit cache blocks or cache lines. If a data item is buffered in cache,

the whole block of the adjacent data is also loaded into the same cache block. A

memory reference is a cache hit if the requested data is in a cache block; otherwise it

is a cache miss, and the data is loaded directly from memory.

A repeated memory reference to the same data is a data reuse. If the requested

data item is in cache, the data access is a cache reuse. Cache reuse may happen

directly when the same data is requested twice, in which case the reuse is called a

temporal cache reuse. Cache reuse may happen indirectly when a fresh data request

hits in cache because the requested data has been brought in by the block transfer of

a formerly requested data item, in which case the reuse is called a spatial cache reuse.

Since large cache blocks are more efficient for contiguous data access and less costly for

cache coherence, the size of cache blocks on modern machines is fairly large, ranging

from 32 bytes to 128 bytes. Large cache blocks make cache spatial reuse extremely

important for good cache utilization.

In the literature, cache spatial reuse is often defined differently in that it includes

the fuzzy property that cache blocks do not unnecessarily conflict with each other to

cause premature eviction from cache. This dissertation uses cache spatial reuse to

denote only the reuse within a cache block; the conflicts among different cache blocks

are referred to as cache interference.

1.1.1

Conflicting Trends of Software and Hardware

Since the advent of microprocessors in late 1970s, the capacity gap between off-chip

memory bandwidth and on-chip CPU power has been steadily widening. Historical

figures on processor performance and off-chip bandwidth have shown that over the

past twenty years, the average annual increase in CPU power is 55%, but the average

improvement in off-chip data bandwidth is merely 28%1 . In other words, as CPU

1

Estimation based on the historical figures compiled by Burger et al [BGK96].

4

power increased by 6,400 times in the past, memory bandwidth increased by no more

than 139 times.

To bridge the memory gap, all modern machines provide high-bandwidth on-chip

data cache in the hope that most memory reads and writebacks can be served by

cache without consuming the valuable memory bandwidth. Although machine cache

has been successful for programs with small data sets and simple access patterns, its

effectiveness has become increasingly problematic because of the following directions

pursued by modern software:

• Large data sets: A major goal in computing is to model the physical world, from

a galaxy to a DNA, from an airplane to a robot, and from molecular dynamics

to electromagnetism. Since we desire as large scope and as high precision as

possible, the demand for larger data representations is insatiable.

• Dynamic computation: Most real-world events are non-uniform and evolving,

such as that of a car crash or a drug injection. Consequently, both their computation structure and data representation are irregular and dynamically changing.

Even in simpler cases where data stays the same, the order of data access may

still change radically in different parts of a program. For example, a physical

model can be traversed first top-down and then inside out.

• Modularized programming: To manage the complexity of developing software

systems with sophisticated capabilities, modern software development must

practice modularization along with computation and data abstraction. A computing task is frequently divided into a hierarchy of sub-steps, and a complex

object broken into many sub-components.

Since large programs perform computation in many phases and access data in

many different places, accesses to the same data item are far separated in time, and

these accesses are often non-contiguous with large strides. When the reuse of a data

item is far separated by a large amount of other data access, the value may be evicted

from cache before it is reused, causing unnecessary data transfer from memory. Largestride accesses, on the other hand, waste cache capacity by causing useless data to be

transferred to cache. Furthermore, low utilization of cache blocks leads to an underutilized cache, effectively reducing its size and causing even more memory transfer.

Moreover, the extensive use of function and data abstraction aggravates the problem

by fragmenting computations and data that could be otherwise cached together.

5

On parallel machines such as high-end servers and supercomputers, the problem of

excessive memory transfer is as serious as it is on uni-processor machines. In fact, the

bandwidth problem may cause even worse consequences for such machines because

memory bandwidth is shared by a potentially large number of processors and consequently is a more critical resource. A single memory module can become the point of

contention and the bottleneck of the whole parallel system. Recently, cache-coherent

shared-memory multiprocessors have become increasingly popular because of their

ease of programming. On such machines, a cache block is the basis of cache coherence and consequently the unit of inter-processor communication. Therefore, low

cache-block utilization wastes not only memory bandwidth but also network bandwidth.

In summary, the analysis of hardware and software trends has revealed an alarming

tension between the excessive demand of memory transfer and the limited supply

of memory bandwidth. The next section examines the effect of this mismatch on

performance.

1.1.2

Memory Bandwidth Bottleneck

This section quantifies the memory bandwidth constraint by modeling and measuring

the fundamental balance between computation and data transfer.

Balance between Computation and Data Transfer

To understand the supply and demand of memory bandwidth as well as other computer resources, it is necessary to go back to the basis of computing systems, which

is the balance between computation and data transfer. This section first formulates

a performance model based on the concept of balance and then uses the model to

examine the performance bottleneck on current machines.

Both a program and a machine have balance. Program balance is the amount

of data transfer (including both data reads and writes) that the program needs for

each computation operation; machine balance is the amount of data transfer that the

machine provides for each machine operation. Specifically, for a scientific program,

the program balance is the average number of bytes that must be transferred per

floating-point operation (flop) in the program; the machine balance is the number

of bytes the machine can transfer per flop in its peak flop rate. On machines with

6

multiple levels of cache memory, the balance includes the data transfer between all

adjacent levels.

The table in Figure 1.1 compares program and machine balance. The upper half

of the table lists the balance of six representative scientific applications2 , including four kernels—convolution, dmxpy, matrix multiply, FFT—and two application

benchmarks—SP from the NAS benchmark suite and Sweep3D from DOE. For example, the first row shows that for each flop, convolution requires transferring 6.4

bytes between the level-one cache (L1) and registers, 5.1 bytes between L1 and the

level-two cache (L2), and 5.2 bytes between L2 and memory. The last row gives the

balance of SGI Origin20003 , which shows that for each flop at its peak performance,

the machine can transfer 4 bytes between registers and cache, 4 bytes between L1

and L2, but merely 0.8 bytes between cache and memory.

As the last column of the table shows, with the exception of mm(-O3), all applications demand a substantially higher rate of memory transfer than that provided by

Origin2000. The demands are between 2.7 to 8.4 bytes per flop, while the supply is

only 0.8 byte per flop. The striking mismatch clearly confirms the fact that memory

bandwidth is a serious performance bottleneck. In fact, memory bandwidth is the

least sufficient resource because its mismatch is much larger than that of register and

Programs

convolution

dmxpy

mm (-O2)

mm (-O3)

FFT

NAS/SP

Sweep3D

Origin2000

Program/machine Balance

L1-Reg L2-L1 Mem-L2

6.4

5.1

5.2

8.3

8.3

8.4

24.0

8.2

5.9

8.08

0.97

0.04

8.3

3.0

2.7

10.8

6.4

4.9

15.0

9.1

7.8

4

4

0.8

Figure 1.1 Comparison between program and machine balance

Program balances are calculated by measuring the number of flops, register loads/stores and cache

misses/writebacks through hardware counters on SGI Origin2000.

3

The machine balance is calculated by taking the flop rate and register throughput from hardware

specification and measuring memory bandwidth through STREAM[McC95] and cache bandwidth

through CacheBench[ML98].

2

7

cache bandwidth, shown by the second and the third column in Figure 1.1. The next

section will take a closer look at this memory bandwidth bottleneck.

The reason matrix multiply mm (-O3) requires very little memory transfer is that

at the highest optimization level of -O3, the compiler performs advanced computation blocking, first developed by Carr and Kennedy[CK89]. The dramatic change of

results from -O2 to -O3 is clear evidence that a compiler may significantly reduce the

application’s demand for memory bandwidth; nevertheless, the current compiler is

not effective for all other programs. I will return to compiler issues in a moment and

for the rest of this dissertation.

Memory Bandwidth Bottleneck

The precise ratios of the demand of data bandwidth to its supply can be calculated by

dividing the program balances with the machine balance of Origin2000. The results

are listed in Figure 1.2. They show the degree of mismatch for each application at

each memory hierarchy level. The last column shows the largest gap: the programs

require 3.4 to 10.5 times as much memory bandwidth as that provided by the machine,

verifying that memory bandwidth is the most limited resource. The data bandwidth

on the other two levels of memory hierarchy is also insufficient by factors between 1.3

to 6.0, but the problem is comparatively less serious.

The insufficient memory bandwidth compels applications into unavoidable low

performance simply because data from memory cannot be delivered fast enough to

keep CPU busy. For example, the Linpack kernel dmxpy has a ratio of 10.5, which

means an average CPU utilization of no more than 1/10.5, or 9.5%. One may argue

Applications Ratios of demand over supply

L1-Reg L2-L1 Mem-L2

convolution

1.6

1.3

6.5

dmxpy

2.1

2.1

10.5

mmjki (-O2) 6.0

2.1

7.4

FFT

2.1

0.8

3.4

NAS/SP

2.7

1.6

6.1

Sweep3D

3.8

2.3

9.8

Figure 1.2 Ratios of bandwidth demand to its supply

8

that a kernel does not contain enough computation. However, the last two rows show

a grim picture even for large applications: the average CPU utilization can be no

more than 16% for NAS/SP and 10% for Sweep3D. In other words, over 80% of CPU

capacity is left unused because of the memory bandwidth bottleneck.

The memory bandwidth bottleneck exists on other machines as well. To fully

utilize a processor of comparable speed as MIPS R10K on Origin2000, a machine

would need 3.4 to 10.5 times of the 300 MB/s memory bandwidth of Origin2000.

Therefore, a machine must have 1.02 GB/s to 3.15GB/s of memory bandwidth, far

exceeding the capacity of current machines such as those from HP and Intel. As

CPU speed rapidly increases, future systems will have even worse balance and a more

serious bottleneck because of the lack of memory bandwidth.

So far, the balance-based performance model has not considered the effect of the

latency constraint and, in particular, the effect of memory latency. It is possible that

memory access incurs such a high latency that even the limited memory bandwidth is

scarcely used. To verify that this is not the case, an additional study was performed

to measure the actual bandwidth consumption of a group of program kernels and a

full benchmark application, as reported in [DK00]. It found that these applications

consume most of the available memory bandwidth. Therefore, memory bandwidth is

a more limiting factor to performance than is memory latency.

In conclusion, the empirical study has shown that for most applications, machine

memory bandwidth is between one third and one tenth of that needed. As a result,

over 80% of CPU power is left un-utilized by large applications, indicating a significant

performance potential that may be realized if the applications can better utilize the

limited memory bandwidth. The next section introduces the solution developed by

this dissertation: improving effective memory bandwidth through global and dynamic

cache reuse.

1.2

Solution through Cache Reuse

This section starts with the general strategy of cache reuse, illustrates its power in

exploiting global and dynamic cache reuse, demonstrates the necessity for its compiler

automation, and finally presents the overall compiler strategy that systematically

applies this strategy to maximize cache performance.

9

1.2.1

Two-Step Strategy of Cache Reuse

Cache reuse can be maximized by the following two-step strategy.

• Step 1. fuse all the computation on the same data

• Step 2. group all the data used by the same computation

The first step, computation fusion, groups all the uses of the same data so that

when a data item is loaded into cache, the program performs all computation on that

data before moving it out. The second step, data grouping, gathers all data used by

the same computation so that during the computation, all cache blocks are utilized

to the greatest extent possible. Both temporal and spatial cache reuse are maximized

as a result of these steps.

Both steps have an implicit pre-step of separation before fusion and regrouping. The first step breaks computations into the smallest units before fusion so that

unrelated computations are separated. Similarly, the second step divides data into

the smallest pieces before regrouping so that unrelated data parts are disjointed.

Therefore, the two-step strategy can be viewed as having four steps if the separation

steps are made explicit.

The strategy is a direct solution to the problems caused by far-separated reuse and

large-stride access common in data-intensive programs. The fusion step minimizes

the distance of data reuse, and the grouping step optimizes the stride of data access.

As a result, computation fusion eliminates repeated memory transfer of the same data

while data grouping fully utilizes each memory transfer. Together they minimize the

total number of transferred cache blocks and therefore the total amount of memory

bandwidth consumption.

The two steps of this strategy are inherently related: they are inseparable and

they must proceed in order. The second step depends on the first because without

fusion, data reuses remain far-separated and the repeated data access would miss

in cache regardless of data grouping. On the other hand, the first step should be

followed by the second because without data grouping, the cache and cache blocks

may be polluted with useless data to the extent that only a few percent of cache is

useful, and the effective memory bandwidth can be reduced by an order of magnitude.

Therefore, neither step can work well without the other. This strategy and its benefits

are especially evident when optimizing large and dynamic programs, as described in

the next two sections and validated in the later chapters.

10

Global Cache Reuse

The strategy of cache reuse can be applied at the global level to improve data reuse

across all program segments and in all data structures. Figure 1.3 illustrates global

cache reuse. The example in (a) is a typical program written by a typical programmer.

It starts with data initialization and then proceeds with several steps of computation.

Although clear and simple logically, the program suffers from far-separated data reuse.

For example, none of the input data is used until all other inputs are processed.

Computation fusion merges the computations on the same data, as shown in

Figure 1.3(b). In the fused function Fused Step 1, each data element is used immediately after its initialization, thus having a minimal reuse distance. Therefore, each

element can be now buffered and reused with a fixed-size cache.

Initialize(...) {

For i

initial[i].data1 <-...

initial[i].data2 <...

End for

}

Process(...) {

Step_1(...) {

For i

tmp1[i].data1 <initial[i].data1

tmp1[i].data2 <tmp1[i].data1

End for

}

Step_2(...) {

For i

tmp2[i].data1 <initial[i].data2

End for

}

...

Fused_Step_1(...) {

For i

initial[i].data1 <-...

tmp1[i].data1 <initial[i].data1

Fused_Step_1(...) {

For i

Data_Group_1[i].data1 <- ...

Data_Group_1[i].data2 <Data_Group_1[i].data1

tmp1[i].data2 <tmp1[i].data1

End for

Data_Group_1[i].data3 <Data_Group_1[i].data2

}

End for

}

Fused_Step_2(...) {

For i

initial[i].data2 <- ...

tmp2[i].data1 <initial[i].data2

Fused_Step_2(...) {

For i

Data_Group_2[i].data1 <- ...

Data_Group_2[i].data2 <Data_Group_2[i].data1

End for

End for

...

}

...

...

}

...

}

...

(b) Computation fusion

(c) Data grouping

(a) Original program

...

Figure 1.3 Example of global cache reuse

The fused program is not perfect because it makes scattered data access to different

arrays. The second step, data grouping, gathers data used by the same computation

into the same data array, as shown in Figure 1.3(c). After data grouping, not only are

related data elements used together, they also locate together in physical memory. In

11

combination, the fusion shortens temporal reuse between global computations, and

the grouping increases spatial reuse among global data.

As shown by the example program, computation fusion and data grouping promise

significant global benefit but also impose drastic changes to the whole program.

Unlike localized techniques, a global transformation may move a piece of computation or data far away from its original place. New challenges immediately arise on

maintaining correctness and estimating profitability. Interestingly, computation and

data transformations follow different restrictions and cause different concerns. They

raise different sets of questions.

Computation fusion is limited by data dependence. Given the widespread and

complex dependences in real programs, how much fusion can a program have, or

equivalently, how close can the uses of the same data be? Starting from that, how

much can be achieved by a source-level transformation through a compiler? Since

computation fusion may produce loops of a huge size, what is the overhead of fusion

and how to eliminate or reduce that overhead? Chapter 2 will study computation

fusion and address these challenging questions.

Unlike computation fusion, data grouping is not constrained by correctness because it does not violate any data dependence as long as a single storage is maintained

for each program data. However, while fusion has no side effect on the unaltered program parts, data grouping uniformly affects every program segment that accesses the

transformed data. In particular, data grouping in one place may not be beneficial

for another place and may in fact be detrimental to overall performance. Therefore,

the crucial problem of data grouping is evaluating its profitability: how to address

the conflicting requirements of different program segments, and ultimately, how to

find an optimal data layout for the whole program? Chapter 3 will study solutions

to these problems.

Dynamic Cache Reuse

A large class of applications is dynamic, where some data structures and their access

pattern remain unknown until run time and may change during the computation. An

example is a car-crash simulation where the shape of the car remains unknown until

the simulation starts, and the shape may change radically during the simulation.

To optimize a dynamic application, the strategy of cache reuse must be applied

at run time after the computation and its data access are determined. Figure 1.4

12

illustrates dynamic data grouping. The example computation sequence traverses

random elements of array f. The stride of access is large and varied. Data grouping

first records the random data access and then gathers simultaneously used data into

contiguous memory locations. If the data is accessed in the same or similar order

multiple times, the overhead of grouping can be amortized effectively. With the

transformed array shown in Figure 1.4, the dynamic access becomes more contiguous

and obtains a better utilization of cache.

Figure 1.4 Example of dynamic cache reuse

Because of the unpredictable and dynamic nature of the computation and data,

both analysis and transformation have to be performed at run time and probably be

performed multiple times. Questions immediately arise on the feasibility, legality and

profitability of such transformations. How to insert run-time analysis and code generation? What methods are cost-effective at run time? How to ensure their correctness,

especially in the presence of repeated data layout changes? How much overhead do

they incur, and can it be reduced through additional compiler optimizations? These

questions will be addressed in Chapter 4.

1.2.2

The Need for Compiler Automation

Applying the strategy of cache reuse leads to radical program changes: computation

fusion rewrites the whole program structure, and data grouping re-shuffles the entire

data layout. In general, a program transformation may be carried out through three

13

different agents: programmers, compilers, or hardware/operating systems. However,

the global scope and extensive scale of computation fusion and data grouping suggest

that an automatic compiler is the most viable approach. To demonstrate, Figure 1.5

lists the characteristics of all three options.

approaches

advantages

√

hardware or

precise run-time

operating systems

information

programmers

compilers

disadvantages

× very limited scope

× run-time overhead of analysis

and transformation

√

domain knowledge × loss of function and data abstraction

× inter-dependence between function

and data

√

× imprecise program and

√ global scope

off-line analysis

machine information

and transformation

Figure 1.5 Comparison among hardware/OS, programmers and compilers

Hardware and operating systems have precise knowledge of the operations being executed and the data being accessed. However, they cannot anticipate future:

they can foresee at most a limited number of instructions down the executing path.

Furthermore, because of the run-time overhead, they cannot afford extensive analysis

and large-scale transformation, both of which are necessary for computation fusion

and data grouping.

Programmers have domain knowledge of their applications. But manual computation fusion and data grouping render program abstraction and modularization

impossible. Indeed, various functions must be mixed together if they access the

same data; similarly, different data structures must be merged if they belong to the

same computation. Furthermore, data layout now depends on computation structure.

Whenever a memory access is added or deleted, the entire data layout may have to be

reorganized. Therefore, if software development is to be scalable and maintainable,

manual fusion and grouping should be mostly avoided.

Among all three approaches, only a compiler can afford the global scope and the

extensive scale of computation fusion and data grouping. Given a source program,

a compiler can analyze and transform the structure of both global computation and

global data. The analysis and transformation are off-line without incurring any run-

14

time overhead. A compiler, however, has its limitations. Its source-level analysis

may not always accurate, and it cannot quantify the machine-dependent effect of a

transformation. Despite its limitations, a compiler is currently the only viable choice

to apply the strategy of cache reuse. If it succeeds, the benefit is enormous. The next

section outlines such a compiler.

1.2.3

A Unified Compiler Strategy

This section presents a unified compiler strategy that maximizes memory hierarchy

performance. It has four phases, as shown in Figure 1.6. The first two phases minimize

overall memory transfer by maximizing cache reuse. The third phase schedules the

remaining memory and cache access to tolerate its latency. The last phase engages

user’s help in identifying additional optimization opportunities that have been missed

by automatic methods. The last column of Figure 1.6 lists the suitable techniques.

Those developed by this dissertation are marked with a ⋆.

main phases

temporal reuse

in

cache and

registers

cache-block

reuse and

cache

utilization

latency

tolerance

user tuning

sub-steps

suitable techniques

(⋆ developed by this research)

global (multi-loop)

⋆ maximal loop fusion

local (single loop)

unroll-and-jam, loop blocking,

register allocation

dynamic

⋆ locality grouping,

space partitioning, curve ordering

inter-array spatial reuse ⋆ inter-array data regrouping

intra-array spatial reuse memory-order loop permutation,

array reshaping, combined schemes

dynamic spatial reuse

⋆ dynamic data packing

cache non-interference

array padding, array copying,

cache-conscious placement

local (single loop)

data prefetching,

instruction scheduling

global (whole-program) ⋆ model of machine & program balance

⋆ bandwidth-based performance tool

Figure 1.6 The overall compiler strategy

for maximizing memory performance

15

The first phase converts data reuse into cache and register reuse. The primary

method is computation fusion, which is first carried out at the global level across

multiple loops, then at the local level within a single loop nest, and finally at run

time for dynamic applications.

On an ideal machine with unit-size cache blocks, the first phase is sufficient for

minimizing memory transfer. On a real machine, however, the second phase is needed

to fully utilize non-unit cache blocks as well as memory pages. The first step of this

phase exploits spatial reuse among global arrays. The succeeding steps improve spatial

reuse within a single array both statically for regular programs and dynamically for

dynamic applications. Finally, the last step adjusts the placement of large arrays to

avoid the remaining cache interference.

After minimizing the amount of memory access by the first two phases, the third

phase schedules the expensive memory and cache accesses so that their latency can be

hidden as much as possible. The scheduling includes source-level data prefetching for

high-latency memory access and assembly-level instruction scheduling for low-latency

cache access. It should be noted that although latency tolerance is important, it does

not help in ameliorating the memory bandwidth bottleneck as the previous phases

do. In fact, data prefetching exacerbates the memory bandwidth problem because it

causes additional memory transfer.

Compiler transformations, however, may still miss optimization opportunities or

make imperfect transformations. When this happens, user tuning is necessary to

achieve top performance. The last phase provides effective and efficient user tuning

though a bandwidth-based performance tool. The tool can also provide accurate

compile-time performance prediction, which is crucial for subsequent parallelization

and run-time scheduling.

The global and dynamic techniques developed by this work play a vital role in

the overall compiler strategy. The later chapters will describe these techniques and

demonstrate their importance. The next section discusses existing local techniques

and their limitations, as well as previous attempts at global and dynamic optimizations.

1.3

Related Work

This section surveys the techniques related to the overall compiler strategy, especially

the previous work on global and dynamic transformations. Their limitations are first

16

discussed individually and then summarized in the last section from three aspects:

narrower purpose, lack of integrated transformation, and lack of compiler automation.

1.3.1

Complementary Techniques

Loop blocking and data prefetching are two widely used optimizations for memory

hierarchy. They complement but cannot achieve the effect of global computation

fusion and data grouping.

Loop Blocking

Loop blocking is a transformation that groups computations on sub-blocks of data

that are small enough to fit in registers or in cache. A comprehensive study of blocking techniques can be found in Carr’s dissertation[Car92]. The recent developments

include the work by Kodukula et al[KAP97] and by Song and Li[SL99]. Since the

new studies can implicitly optimize beyond a single loop nest, they will be discussed

in the next section with the explicit work on loop fusion.

The primary limitation of loop blocking is its local scope: blocking is applied

only to a single loop nest at a time. Consequently, it cannot exploit data reuse

among disjoint loops. To overcome this limitation, we have to fuse multiple loops

and determine how to interleave their iterations. This is precisely the process of loop

fusion, which is discussed in the next section. Another limitation of blocking is that it

cannot block computations and data that are unknown at compile time. Section 1.3.2

discusses related dynamic transformations.

Data Prefetching

Data prefetching is another widely studied technique. Unlike loop blocking or loop

fusion, the goal of data prefetching is to tolerate or hide memory latency rather

than to eliminate the memory access. Data prefetching identifies memory references

that are cache misses and then dispatches them early enough in execution so that

their latency can be overlapped with useful computation. Porterfield first developed

software prefetching[Por89]. Mowry designed and evaluated a complete algorithm

that later gained wide acceptance[Mow94].

Data prefetching, however, cannot hide memory latency imposed by the memory

bandwidth bottleneck. Indeed, data prefetching does not reduce a single byte of

memory transfer. On the contrary, it incurs additional memory transfer because it

17

may prefetch the wrong data or prefetch too early or too late. Since actual memory

latency is the reciprocal of the consumed memory bandwidth, data prefetching cannot

completely hide memory latency unless the memory bandwidth bottleneck has been

alleviated by other optimizations.

1.3.2

Global and Dynamic Optimizations

This section discusses previous work on global loop fusion, global data placement and

dynamic optimizations.

Global Loop Fusion

Many researchers have studied loop fusion. Allen and Cocke first published the

transformation[AC72]. The first significant role of fusion is to improve data reuse in

a virtual memory system, studied by Abu-Sufah et al[ASKL81]. Wolfe gave a simple

test for the legality of fusion[Wol82]. Two loops cannot be fused if they have fusionpreventing dependences, which are those forward dependences that are reversed after

loop fusion. In the same work, Wolfe demonstrated through a few examples how loop

fusion improves register reuse and reduces data storage on vector machines.

The first implementation of fusion in a compiler is by Allen[All83], who used loop

fusion to improve register reuse in a legendary compiler that was later adopted by all

vector supercomputers[AK87]. In its implementation, Allen required that fusible

loops must have the same lower bound, upper bound and increment, no fusionpreventing dependence, and no true dependence on any intervening statements. Since

the improvement by fusion is not as large as by other transformations such as loop

interchange, Allen used fusion as a “cleanup” operation.

Loop fusion later took a prominent role in the work of Callahan, who used it

to detect and construct coarse-grain parallelism[Cal87]. He gave a greedy fusion

algorithm that runs in linear time to the number of loops and produces the minimal

number of fused loops. The restriction for correctness is the same as in earlier studies,

and the criterion for profitability is parallelism rather than cache reuse. So Callahan’s

method may fuse loops of no data sharing.

To enable more loop fusion, Porterfield introduced a transformation called peeland-jam, which can fuse loops with fusion-preventing dependences by peeling off some

iterations of the first loop and then applying fusion on the remaining parts[Por89].

While Porterfield considered only a pair of loops, Manjikian and Abdelrahman later

18

extended peel-and-jam to find the minimal peeling factor for a group of fusible

loops[MA97]. They evaluated their fusion scheme for parallel programs. Also enabled

by peel-and-jam, Song and Li developed a new tiling method that blocks multiple

loops within a time-step loop with the goal of improving cache reuse[SL99]. However,

these methods are not a complete global strategy because they did not address the

cases where not all loops in a program are fusible. In addition, peel-and-jam is a limited form of loop alignment because it can only shift the first loop up (or the second

loop down), but not the reverse. So it does not always minimize the distance of data

reuse in fused loops. Finally, peel-and-jam cannot fuse loops that have intervening

statements that use the same data.

To find a solution for global loop fusion, a graph-partitioning formulation was studied independently both by Gao et al.[GOST92] and by Kennedy and McKinley[KM93].

Both their aims were to improve temporal reuse in registers, and they modeled the

benefit of register reuse as weighted edges between a pair of loops. The goal was

to partition all loops into legal fusible groups so that the inter-group edge weight

(unrealized data reuse) is minimal. Kennedy and McKinley proved that the general

fusion problem is NP-Complete. Both approaches used the heuristic that recursively

applies min-cut algorithm to bi-partition the graph. Both avoided fusing loops with

fusion-preventing dependences. However, a weighted-edge between two loops does

not correctly model data sharing. Therefore, the partitioning method on normal

graphs does not minimize the bandwidth consumption of the whole program. In another study of loop fusion, Darte considered the added complexity of loop shifting

and proved that even loop fusion for single types (e.g. parallel loops) is strongly NPcomplete in the presence of loop shifting[Dar99]. Recently, Kennedy developed a fast

algorithm that always fuses along the heaviest edge[Ken99]. His algorithm allows accurate modeling of data sharing as well as the use of fusion enabling transformations.

But none of these algorithms has been implemented or evaluated.

The first implementation for general fusion and its evaluation on non-trivial programs were accomplished by McKinley et al[MCT96]. They fused only loops with an

equal number of iterations and with no fusion-preventing dependences. As a result,

only 80 out of 1400, or 6% of tested loops were fused. The effect on full applications was mixed: fusion improved the hit rate for four out of 35 programs by 0.24%

to 0.95%, but it also degraded performance of other three programs. Singhai and

McKinley improved the fusion heuristic by considering the register pressure and by

approximating graph partitioning with optimal tree partitioning[hSM97]. Since they

19

fused only loops with no fusion-preventing dependences, the improvement to wholeprogram performance is modest except for two programs running on DEC Alpha. The

potential of global data reuse is much larger, as demonstrated by a simulation study

by McKinley and Temam[MT96]. They found that majority of program misses are

inter-loop temporal reuses. Therefore, the important question remains open on the

potential of global fusion, especially when aggressive fusion-enabling transformations

are used.

To enable more aggressive loop fusion, some researchers have taken a radically different approach. Instead of blocking loops, Kodukula et al. tiled data and “shackled”

computations on each data tile[KAP97]. Similarly, Pugh and Rosser sliced computations on each data element or data block[PR99]. Although effective for blocking

single loops, data-oriented approaches are not yet practical as a global strategy for

three reasons. First, without regular loop structures, it is not clear how to formulate and direct a global transformation. The shape of the transformed program is

highly dependent on the choice of not only the shackled or sliced data but also of its

starting loop. Furthermore, to maintain correctness, these methods need to compute

all-to-all transitive dependences, whose complexity is cubic in the number of memory

references in a program. Even when the dependence information is available, it is

still not clear how to derive the best partitioning and ordering of the computations

on different data elements, especially in the face of a large amount of unstructured

computation. Finally, it is not clear how data-oriented transformations interact with

traditional loop-based transformations, and how the side effect of fusion can be tackled. Kodukula et al. did not apply their work beyond a single loop nest[KAP97]. Pugh

and Rosser tested Swim and Tomcatv and found mixed results. On SGI Octane, the

first program was improved by 10% but the second “interacted poorly with the SGI

compiler”[PR99].

The previous work on loop fusion did not combine it with data transformations

with one exception. Manjikian and Abdelrahman, who applied padding to reduce

cache conflicts[MA97]. Array padding at large data granularity is not a direct solution

to cache utilization and has several important shortcomings compared to fine-grain

data optimization, as discussed in the next section.

20

Global Data Placement

Once computation is optimized, data layout still needs careful arrangement because

it affects the utilization within cache blocks and the interference among cache blocks.

Thabit studied the packing of scalars into cache blocks[Tha81]. He proved that

finding the optimal packing for non-unit cache blocks is NP-complete.

The primary method for exploiting spatial reuse in arrays is to make data access contiguous. Instead of rearranging data, the early studies reordered loops so

that the innermost loop traverses data contiguously within each array. Various loop

permutation schemes were studied for perfect loop nests or loops that can be made

perfect, including those by Abu-Sufah et al.[ASKL81], Gannon et al.[GJG88], Wolf

and Lam[WL91], and Ferrante et al.[FST91]. McKinley et al. developed an effective heuristic that permutes loops into memory order for both perfect or non-perfect

nested loops[MCT96]. Loop reordering, however, cannot always achieve contiguous

data traversal because of data dependences. This observation led Cierniak and Li to

combine data transformation with loop reordering[CL95], a technique that was subsequently expanded by Kandemir et al[KCRB98]. Regardless of the form of transformation, all these techniques are limited by their goal, which is to improve data reuse

within a single array, or intra-array spatial reuse.

Data reuse within a single array is not adequate because not all data access to

the same array can be made contiguous. One example is a dynamic application,

where the data access within the same array is unpredictable at compile time, making

it impossible to obtain contiguous memory access. Another example is a regular

application, where the computation traverses high-dimensional data through different

directions. Again, data access to a single array cannot always be made contiguous.

Data reuse among multiple arrays presents a promising alternative when data access can not be made contiguous. By combining multiple arrays and increasing the

granularity of data access, the portion of useful data in each cache block can be significantly increased. In fact for large programs with many data arrays, inter-array reuse

may fully utilize cache blocks without the need for contiguous data access. Interarray data transformations, however, have not been attempted except for the work

by Eggers and Jeremiassen[JE95]. They grouped all arrays accessed by a parallel

thread to reduce false sharing among parallel processors. However, blindly grouping

local data pollutes cache and cache blocks with useless data because not all local

data objects are used at once. Besides the work on arrays, many researchers stud-

21

ied data placement optimizations for cache spatial reuse among pointer-based data

structures. Seidl and Zorn clustered frequently referenced objects[SZ98], and Calder

et al. reordered objects based on their temporal relations[CCJA98]. Chilimbi et

al. clustered frequently used attributes within each object class[CDL99]. The basic

approach shared by these methods is to place frequently used or closely referenced objects in close by memory locations. However, that two objects being either frequently

accessed or for one time together accessed does not mean that they are always simultaneously accessed. Hence, their methods may place useless data into cache blocks

and therefore degrade actual performance. In a large program where different data

structures are used at different times, greedy grouping can seriously degrade cacheblock reuse rather than improving it. Furthermore, these methods are static and

therefore cannot fully optimize dynamic programs whose data access pattern changes

during execution. For example, in a sparse-matrix code, the matrix may be iterated

first by rows and then by columns. In scientific simulations, the computation order

changes as the physical model evolves. In these cases, a fixed static data layout is

not likely to perform well throughout the computation.

In addition to the reuse within the same cache block, attention needs to be paid to

the interference among multiple cache blocks. A program can rearrange the location

of whole arrays or array fragments in two ways: make them either well separated

by padding, studied by Bailey[Bai92], or fully contiguous by copying, first used by

Lam et al[LRW91]. Reducing cache interference, however, is not an approach as direct and effective as improving cache-block reuse. The best way to eliminate any

cache interference is to place simultaneously used data into the same cache block,

not by arranging them into multiple cache blocks. The large granularity used by

packing precludes data reordering within the data object and across multiple data

objects. Furthermore, padding cannot be applied to arrays of unknown size or machines with different cache parameters. It can reduce only cache interference but not

the page-table working set. Moreover, both padding and copying carry a run-time

cost, especially copying. Therefore, a compiler should first organize data within the

same cache block and then use techniques such as data padding and copying to reduce

cache interference if necessary.

Kremer developed a general formulation for finding the optimal data layout that is

either static or dynamic for a program at the expense of being an NP-hard

problem[Kre95]. He also showed that it is practical to use integer programming

to find an optimal solution for normal programs. However, Kremer’s formulation

22

requires the estimation on the overhead and the benefit of a data transformation,

which is not readily available to a compiler. He and others demonstrated that runtime communication and computation performance could be approximated through

the use of training sets[BFKK91]. However, it is yet to be seen how well memory

hierarchy performance can be predicted.

Dynamic Transformations

Researchers have long been studying dynamic applications such as molecular simulations. The best-known scheme is called inspector-executor, pioneered by Saltz and his

colleagues[DUSH94]. At run time, the inspector analyzes the computation and produces an efficient parallelization scheme. Then the executor carries out the parallel

execution.

Various specific schemes were also developed for optimizing cache performance.

Saltz’s group extended the inspector-executor model and used a reverse Cuthill Mcgee

ordering to improve locality in a multi-grid computation[DMS+92]. Another method,

domain partitioning, has been used to block computation for cache by Tomko and

Abraham[TA94]. Al-Furaih and Ranka examined graph-based clustering of irregular

data for cache[AFR98]. Mellor-Crummey et al. employed space-filling curve ordering

to block N-body type computations for multi-level memory hierarchy[MCWK99]. The

above methods are powerful, but they incur a cost higher than linear to the number