V-Transform: An Enhanced Polynomial Coefficient Based DC Suraj Sindia Virendra Singh

V-Transform: An Enhanced Polynomial Coefficient Based DC

Test for Non-Linear Analog Circuits

Suraj Sindia

Centre for Electronic

Design and Technology

Indian Institute of Science

Bangalore, India

Email: ssuraj@cedt.iisc.ernet.in

Virendra Singh

Supercomputer Education and Research Centre

Indian Institute of Science

Bangalore, India

Email: viren@serc.iisc.ernet.in

Vishwani Agrawal

Department of Electrical and Computer Engineering

Auburn University

Alabama, AL, USA

Email: vagrawal@eng.auburn.edu

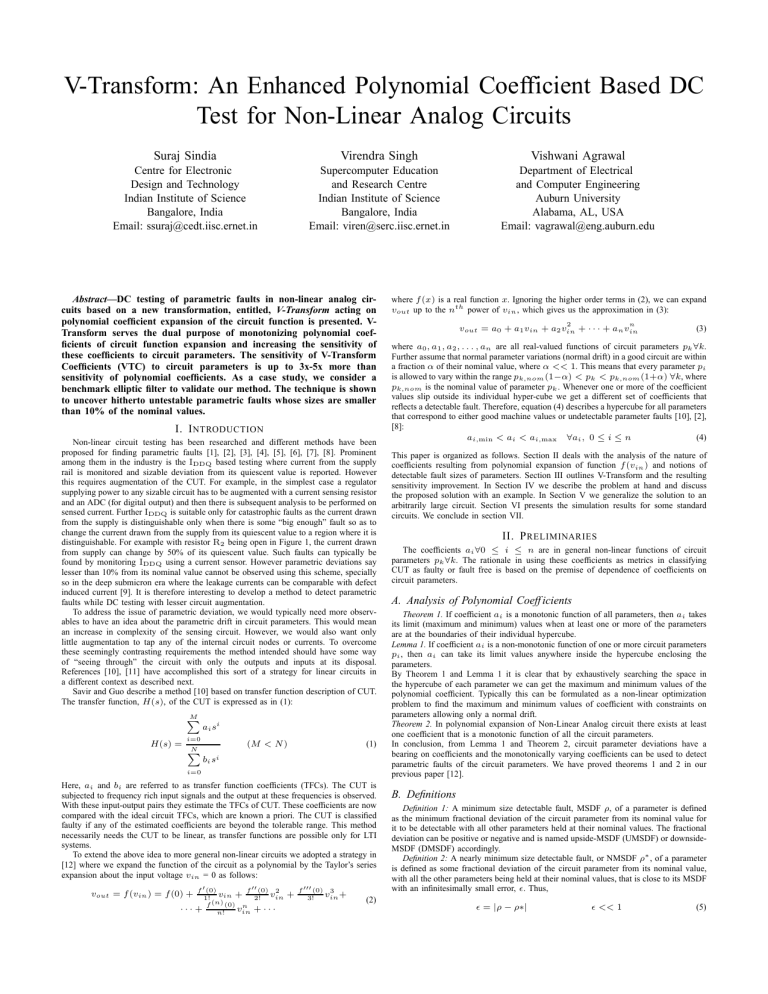

Abstract—DC testing of parametric faults in non-linear analog circuits based on a new transformation, entitled, V-Transform acting on polynomial coefficient expansion of the circuit function is presented. V-

Transform serves the dual purpose of monotonizing polynomial coefficients of circuit function expansion and increasing the sensitivity of these coefficients to circuit parameters. The sensitivity of V-Transform

Coefficients (VTC) to circuit parameters is up to 3x-5x more than sensitivity of polynomial coefficients. As a case study, we consider a benchmark elliptic filter to validate our method. The technique is shown to uncover hitherto untestable parametric faults whose sizes are smaller than 10% of the nominal values.

I. I

NTRODUCTION

Non-linear circuit testing has been researched and different methods have been proposed for finding parametric faults [1], [2], [3], [4], [5], [6], [7], [8]. Prominent among them in the industry is the I

DDQ based testing where current from the supply rail is monitored and sizable deviation from its quiescent value is reported. However this requires augmentation of the CUT. For example, in the simplest case a regulator supplying power to any sizable circuit has to be augmented with a current sensing resistor and an ADC (for digital output) and then there is subsequent analysis to be performed on sensed current. Further I

DDQ is suitable only for catastrophic faults as the current drawn from the supply is distinguishable only when there is some “big enough” fault so as to change the current drawn from the supply from its quiescent value to a region where it is distinguishable. For example with resistor R

2 being open in Figure 1, the current drawn from supply can change by 50% of its quiescent value. Such faults can typically be found by monitoring I

DDQ using a current sensor. However parametric deviations say lesser than 10% from its nominal value cannot be observed using this scheme, specially so in the deep submicron era where the leakage currents can be comparable with defect induced current [9]. It is therefore interesting to develop a method to detect parametric faults while DC testing with lesser circuit augmentation.

To address the issue of parametric deviation, we would typically need more observables to have an idea about the parametric drift in circuit parameters. This would mean an increase in complexity of the sensing circuit. However, we would also want only little augmentation to tap any of the internal circuit nodes or currents. To overcome these seemingly contrasting requirements the method intended should have some way of “seeing through” the circuit with only the outputs and inputs at its disposal.

References [10], [11] have accomplished this sort of a strategy for linear circuits in a different context as described next.

Savir and Guo describe a method [10] based on transfer function description of CUT.

The transfer function, H ( s ) , of the CUT is expressed as in (1):

M

P a i s i

H ( s ) = i =0

N

P b i s i i =0

( M < N ) (1)

Here, a i and b i are referred to as transfer function coefficients (TFCs). The CUT is subjected to frequency rich input signals and the output at these frequencies is observed.

With these input-output pairs they estimate the TFCs of CUT. These coefficients are now compared with the ideal circuit TFCs, which are known a priori. The CUT is classified faulty if any of the estimated coefficients are beyond the tolerable range. This method necessarily needs the CUT to be linear, as transfer functions are possible only for LTI systems.

To extend the above idea to more general non-linear circuits we adopted a strategy in

[12] where we expand the function of the circuit as a polynomial by the Taylor’s series expansion about the input voltage v in

= 0 as follows: v out

= f ( v in

) = f (0) + f

· · · +

0

(0)

1!

f

( n v in

) (0) n !

+ v f n in

00

(0)

2!

+ v

· · ·

2 in

+ f

000

(0)

3!

v

3 in

+

(2) where f ( x ) is a real function x . Ignoring the higher order terms in (2), we can expand v out up to the n th power of v in

, which gives us the approximation in (3): v out

= a

0

+ a

1 v in

+ a

2 v

2 in

+ · · · + a n v n in

(3) where a

0

, a

1

, a

2

, . . . , a n are all real-valued functions of circuit parameters p k

∀ k .

Further assume that normal parameter variations (normal drift) in a good circuit are within a fraction α of their nominal value, where α << 1 . This means that every parameter p i is allowed to vary within the range p k,nom

(1 − α ) < p k

< p k,nom

(1+ α ) ∀ k , where p k,nom is the nominal value of parameter p k

. Whenever one or more of the coefficient values slip outside its individual hyper-cube we get a different set of coefficients that reflects a detectable fault. Therefore, equation (4) describes a hypercube for all parameters that correspond to either good machine values or undetectable parameter faults [10], [2],

[8]: a i, min

< a i

< a i, max

∀ a i

, 0 ≤ i ≤ n (4)

This paper is organized as follows. Section II deals with the analysis of the nature of coefficients resulting from polynomial expansion of function f ( v in

) and notions of detectable fault sizes of parameters. Section III outlines V-Transform and the resulting sensitivity improvement. In Section IV we describe the problem at hand and discuss the proposed solution with an example. In Section V we generalize the solution to an arbitrarily large circuit. Section VI presents the simulation results for some standard circuits. We conclude in section VII.

II. P

RELIMINARIES

The coefficients a i

∀ 0 ≤ i ≤ n are in general non-linear functions of circuit parameters p k

∀ k . The rationale in using these coefficients as metrics in classifying

CUT as faulty or fault free is based on the premise of dependence of coefficients on circuit parameters.

A. Analysis of Polynomial Coeff icients

Theorem 1. If coefficient a i is a monotonic function of all parameters, then a i takes its limit (maximum and minimum) values when at least one or more of the parameters are at the boundaries of their individual hypercube.

Lemma 1. If coefficient a i p i

, then a i is a non-monotonic function of one or more circuit parameters can take its limit values anywhere inside the hypercube enclosing the parameters.

By Theorem 1 and Lemma 1 it is clear that by exhaustively searching the space in the hypercube of each parameter we can get the maximum and minimum values of the polynomial coefficient. Typically this can be formulated as a non-linear optimization problem to find the maximum and minimum values of coefficient with constraints on parameters allowing only a normal drift.

Theorem 2. In polynomial expansion of Non-Linear Analog circuit there exists at least one coefficient that is a monotonic function of all the circuit parameters.

In conclusion, from Lemma 1 and Theorem 2, circuit parameter deviations have a bearing on coefficients and the monotonically varying coefficients can be used to detect parametric faults of the circuit parameters. We have proved theorems 1 and 2 in our previous paper [12].

B. Definitions

Definition 1: A minimum size detectable fault, MSDF ρ , of a parameter is defined as the minimum fractional deviation of the circuit parameter from its nominal value for it to be detectable with all other parameters held at their nominal values. The fractional deviation can be positive or negative and is named upside-MSDF (UMSDF) or downside-

MSDF (DMSDF) accordingly.

Definition 2: A nearly minimum size detectable fault, or NMSDF ρ ∗ , of a parameter is defined as some fractional deviation of the circuit parameter from its nominal value, with all the other parameters being held at their nominal values, that is close to its MSDF with an infinitesimally small error, . Thus,

= | ρ − ρ ∗| << 1 (5)

R1

I

M1

Vdd

R2

I

M2

V out

TABLE I

MSDF FOR CASCADED AMPLIFIER OF F IGURE 1 WITH

α = 0.05.

Circuit parameter

Resistor R

1

Resistor R

2

%upside %downside

MSDF MSDF

10.3

12.3

7.4

8.5

M1 M2

V in

Fig. 1.

Cascaded amplifier.

NMSDF also has notions of upside and downside as in case of MSDF. In (5), can be perceived as a coefficient of uncertainty about the MSDF of a parameter. If ψ is the set of all coefficient values spanned by the parameters while varying within their normal drifts, i.e.,

ψ = { υ

0

, υ

1

∀ k

, · · · p

, υ n

| k,nom

υ

0

∈ A

0

, υ

1

(1 − α ) < p

∈ A

1 k

< p

, · · · , υ n k,nom

∈ A

(1 + α ) n

} then by definitions 1 and 2, ψ includes all possible values of coefficients that are not detectable. Any parametric fault inducing coefficient value outside the set ψ will result in a detectable fault.

III. V-T

RANSFORM

Let us define V-Transform coefficients as follows: if C

1

, C

2

· · · C n coefficients of CUT then their V-Transform coefficients denoted by V

C

1 are given by are polynomial

, V

C

2

· · · V

Cn

V

Ci

= e

γC

0 i

∀ 0 ≤ i ≤ n (6) where C 0 i are the modified polynomial coefficients defined indirectly as follows dC 0 i dp j

= dC i dp j

∀ 0 ≤ i ≤ n (7) a

0

= V

DD

− R

2

K a

1

= R

2

K W

L

2

W

L

2

( V

DD

R

2

1

K

2 W

L

2( V

DD

− V

T

− V

T

)

2

2

+

V

4

T

−

1

) R

1

W

L

1

V

T

2

4 R

2

1

K

2 W

L

+2( V

DD

2

1

− V

T

V

3

T

) R

1

K W

L

1

V

T a a

2

4

= R

2

K

W

L

2 a

3

= 4 V

T

K

3 W

L

2

1

= − K

3 W

L

2

1

2( V

DD

− V

T

) R

1

K

− 6 R

2

1

K

2 W

L

2

1

V

T

2

W

L

1

W

L

2

2

R

2

1

R

2

W

L

2

2

R

2

1

R

2

(10) a

0

= 1 .

2 − R

2

2 .

56 × 10 −

3

+ 1 .

024 × 10 −

7

− 5 .

12 × 10 −

4

R

1

R

2

1 a

1

= 4 .

096 × 10 − 9

R

2

1

R

2

+ 5 .

12 × 10 − 6

R

1

R

2 a

2

= 1 .

28 × 10 − 5

R

1

R

2

− 1 .

536 × 10 − 8

R

2

1

R

2 a

3

= 2 .

56 × 10 − 8

R

2

1

R

2 a

4

= 1 .

6 × 10 − 8

R

2

1

R

2

(11)

To find the limit values of the coefficient a

0 we assume the parameters R

1 and R

2 deviate by a fraction x and y from their nominal values respectively. To maximize a

0 we have the objective function as given by (12) subject to constraints in (13). Note that here we have set out to find MSDF of R

1

. Similar approach can be used to find the

MSDF of R

2

.

1 .

2 − R

2 ,nom

(1 + y )

(

2 .

56 × 10 −

3

+

1 .

024 × 10 −

7

R

2

1 ,nom

− 5 .

12 × 10 −

4

R

1 ,nom

(1 + x )

2

(1 + x )

)

(12)

The definition of C 0 i as in (7) ensures that these modified polynomial coefficients are monotonic with the polynomial coefficients. Further, the V-Transform coefficients

(VTC) are defined as exponential functions of these modified polynomial coefficients.

γ is a sensitivity parameter which can be chosen according to the desired sensitivity. The gain in sensitivity of V-Transform coefficients to circuit parameters over the sensitivity of ordinary polynomial coefficients is given by v out

S

S

VC i pi

Ci pi

=

IV. P

dCi dpi

γe

γC 0 i

• pi e

γC 0 i dCi dpi

• pi

Ci

ROBLEM AND

= a

0

+ a

1 v in

+ a

2 v

2 in

A

= γC

PPROACH

+ a

3 v

3 in i

+ a

4 v

4 in

(8)

We shall first illustrate with an example the calculation of limits of the polynomial coefficients for a simple circuit using MOS transistors. We shall follow this up with

MSDF values for the circuit parameters.

Example 1. Two stage amplifier Consider the cascaded amplifier shown in Figure 1.

The output voltage V out equation as in (9).

in terms of input voltage results in a fourth degree polynomial

(9)

Where the constants a

0

, a

1

, a

2

, a

3 are defined symbolically in (10) for M1 and M2 operating in saturation region. Nominal values of V

DD

=1.2V, V

T

= 400mV,

1

2

W

L

2

= 20 parameters R

1

, and and R

2

K = 100 µ A / V

2 as stated in (11).

W

L

=

1 are substituted to get coefficients in terms of

4 .

096 × 10

+ 5

−

+5 .

12 × 10 −

.

9

6

R

2

1 ,nom

12

R

1 ,nom

×

(1 +

(1 +

= 4 .

096 × 10 −

9 x

R

10

) x

2

2

)

R

R

2 ,nom

2 ,nom

1 ,nom

−

6

R

(1 +

(1 +

1 ,nom

ρ

(1 +

)

2

R

(1 + y )

ρ

2 y

)

)

,nom

R

2 ,nom

(13)

1

−

.

28

1 .

536

×

× 10

10

− 8

= 1 .

− 5

R

28

R

2

1 ,nom

×

1 ,nom

10

(1 +

(1 +

− 5

− 1 .

536 × 10

R

− 8 x

R

2

) x

2

) R

R

1 ,nom

2 ,nom

2 ,nom

(1 +

1 ,nom

(1 +

ρ

(1 +

)

ρ

(1 +

R

)

2 y ) y )

2 ,nom

R

2 ,nom

2 .

56 × 10 −

8

R

2

1 ,nom

(1 + x )

2

R

2 ,nom

= 2 .

56 × 10 −

8

R

2

1 ,nom

(1 +

(1 + ρ )

2 y

R

)

2 ,nom

(14)

(15)

1 .

6 × 10 − 8

R

2

1 ,nom

(1 +

= 1 .

6 × 10 − 8 x )

2

R

2 ,nom

R

2

1 ,nom

(1 +

(1 +

ρ )

2 y

R

)

2 ,nom

− α ≤ x, y ≤ α

(16)

(17)

The extreme values for x and y on solving the set of equations in (12-17) we have x =

− α and y = − α , this gives us the MSDF value for R

1

, ρ in (18).

ρ = (1 − α )

1 .

5

− 1 ≈ 1 .

5 α − 0 .

375 α

2

(18)

Table I gives the MSDF for R

1 and R

2 based on above calculation.

Start

Start

Apply DC sweep to input and note corresponding output voltage levels

Apply DC sweep to input and note corresponding output voltage levels

Polynomial Curve fit the obtained I/O data -find the coefficient values of fault free circuit

Polynomial Curve fit the obtained I/O data

Compute V-Transform

Coefficients

Compute V-Transform coefficients from the extracted polynomial coefficients

i = 0 i = i+1

Simulate for all parametric faults at the simplex of hypercube

Find min-max values of each V-Transform coefficient (V

Ci

) from i =1…N across all simulations

Stop

Yes

|C i

| > |C

|C i in

(1+

| < |C in

(1i

)| or i

)| i < N ?

No

No

Subject CUT to further tests

Yes

CUT is faulty

Stop

Fig. 3.

Flow chart of test procedure for CUT.

Fig. 2.

coefficients.

Flow chart showing fault simulation process and bounding of

R2

V. G

ENERALIZATION

In general, calculation as above cannot be done for arbitrarily large circuits. Such circuits are handled by obtaining a nominal numeric polynomial expansion of the desired circuit. This is done by sweeping the input voltage across all possible values and noting the corresponding output voltages. Now, the output voltage is plotted against the input voltage. A polynomial is fit to this curve and the coefficients of this polynomial are taken to be the nominal coefficients of the desired polynomial. A V-Transform curve is now obtained based on the polynomial curve using the transformation in equation (9).

The circuit is simulated for different drifts in the parameter values at equally spaced points from inside the hypercube enclosing each circuit parameter, spaced apart.

Polynomials coefficients and hence V-Transform coefficients are obtained for each of these simulations. The maximum and minimum values of coefficient in this search are taken as the limit value on that coefficient. Once the limit values on all coefficients have been determined the CUT is subjected to DC sweep at the input. Its response to the

DC sweep is curve fitted to a polynomial of order same as the fault free circuit. The

V-Transform coefficients for CUT are now obtained. If there are any coefficients that lay outside the limit values of corresponding coefficients of the fault free circuit, we can conclude the CUT is faulty with a high probability that is inversely proportional to coefficient of uncertainty . The converse is also true. Flow chart in Figure 2 summarizes the process of numerically finding the V-T coefficients and finding the bounds on V-T coefficients. Flow chart in Figure 3 outlines the procedure to test CUT using the V-

Transform coefficients. The bounds on coefficients of fault free circuit are found a priori as shown in flowchart of Figure 2.

VI. S

IMULATION

R

ESULTS

We subjected an elliptic filter shown in Figure 4 to V-Transform coefficient based test. The circuit parameter values are as in the benchmark circuit maintained by Stroud et al. [13]. Figure 5 shows the computed response and the estimated polynomial obtained by curve fitting: v out

= 4 .

5341

+ 2

−

.

3 .

498

1309 v v

3 in in

− 2 .

5487

− 0 .

50514 v v

4

2 in in

+ 0 .

039463 v

5 in

(19)

The combinations of parameter values leading to limits on the coefficients are as shown in Tables II and III. Some of the circuit parameters are not shown in the table because they do not appear in any of the coefficients and are kept at their nominal values. Further, results on pass/fail detectability of some injected faults is tabulated in Table IV.

Vin

R1

−

+

C1

R4

R3

C3

R7

R6

R5

C2 C4

−

+

R8

R9

R11

R10 C6

C5

Fig. 4.

Elliptic filter.

R12

R13

C7

−

+

R14

R15

Vout

VII. C

ONCLUSION

A new approach for testing non-linear circuits based on polynomial expansion of the circuit was proposed. The approach was underpinned by V-Transform which renders the polynomial coefficients monotonic and increases the sensitivity of polynomial coefficients in transform domain (V-domain). The minimum size detectable faults of some of the parameters in circuits are as low as 5% which implies impressive fault coverage can be achieved with VTC as the metric. The method has been extended to sensitivity based fault diagnosis with probabilistic confidence levels in parameter drifts. The method of polynomial expansion at DC alone, as described here, may not detect certain types of faults, such as, parametric faults of a capacitor. To overcome this, in our ongoing work, we are generalizing this technique to multiple frequencies.

A

CKNOWLEDGMENT

The authors would like to thank Prof. Vittala Rao, formerly with Dept. of mathematics,

IISc for his comments and help in monotonicity arguments of V-Transform coefficients.

3

2

1

0

−1

−2

−3

0

5

4

Polynomial Coefficient Plot

Simulated

5th degree polynomial a5 = 0.039463

a4 = −0.50514

a3 = 2.1309

a2 = −2.5487

a1 = −3.498

a0 = 4.5341

6000

5000

4000

3000

2000

1000

V−Transform Coefficient plot

Vc5 = 1.0402

Vc4 = 1.6572

Vc3 = 8.4224

Vc2 = 12.7904

Vc1 = 33.0492

Vc0 = 93.1396

1 2 3

Input DC Voltage (Vin)

4 5

0

0 1 2 3

Input DC Voltage (Vin)

Fig. 5.

DC response of elliptic filter with curve fitting polynomial and V-Transform plot

4 5

TABLE II

P ARAMETER COMBINATIONS LEADING TO MAXIMUM VALUES OF

V-T RANSFORM COEFFICIENTS WITH

α = 0.05.

TABLE IV

R ESULTS FOR SOME INJECTED FAULTS .

Circuit

Parameter

(Ω)

R

R

R

R

R

R

R

R

R

1

2

3

4

5

6

7

11

12

= 19.6k

= 196k

= 147k

= 1k

= 71.5

= 37.4k

= 154k

= 110k

= 110k

V c 0

V c 1

V c 2

P ARAMETER COMBINATIONS LEADING TO MINIMUM VALUES OF

Circuit

Parameter

(Ω)

V-T RANSFORM COEFFICIENTS WITH

α = 0.05.

R

1

= 19.6k

R

2

= 196k

R

3

= 147k

R

4

= 1k

R

5

= 71.5

R

6

= 37.4k

R

7

= 154k

R

11

= 110k

R

12

= 110k

V c 0

20.5k

205k

150k

V

18.6k

186k

139k

1010 950

80 70

R

TABLE III c 1

V c 2

18.6k

205k

139k

950

70

EFERENCES

V

V c 3 c 3

20.5k

205k

146k

950

80

V

V c 4 c 4

20.5k

205k

154k

950

70

V

V c 5

18.6k

20.5k

20.5k

20.5k

18.6k

18.6k

186k 205k 186k 186k 186k 205k

139k 154k 154k 154k 139k 154k

950 1010 1010 1010 1010 1010

70 80 80 70 80 70

37.4k

37.4k

37.4k

37.4k

37.4k

37.4k

161k 161k 146k 161k 146k 146k

115k 115k 104k 115k 104k 104k

104k 115k 104k 104k 104k 104k c 5

20.5k

186k

139k

950

80

39.2k

39.2k

39.2k

39.2k

35.5k

39.2k

146k 146k 161k 146k 161k 161k

104k 104k 115k 104k 115k 115k

115k 104k 115k 115k 115k 115k

[1] A. Abderrahman, E. Cerny, and B. Kaminska, “Optimization Based Multifrequency Test Generation for Analog Circuits,” Journal of Electronic

Testing: Theory and Applications, vol. 9, pp. 59–73, Mar 1996.

[2] S. Chakravarty and P. J. Thadikaran, Introduction to IDDQ Testing.

Kluwer Academic Publishers, 1997.

[3] S. Cherubal and A. Chatterjee, “Test Generation Based Diagnosis of

Circuit

Parameter

R

1 down 15%

R

2 down 10%

R

3 up 5%

R

4 down 15%

R

5 up 10%

R

7 up 5%

R

11

R

12 up 5% down 5%

Out of bound polynomial coeff.

a

3

, a

4 a

2 a

3 a

0 a

4

None

None

None

Yes

Yes

Yes

Yes

Yes

No

No

No

Fault Out of bound detected?

V-Transform coeff.

V

V c 1

V c

0 c

2

, V

V

V c

0

V c

0

V c

1

V c

4 c

4

− V c

4

, V c 2 c

5

, V c 3

− V c

4

, V c

4

, V

, V

, V c

2 c

5 c

5

Device Parameters for Analog Circuits,” in Proc. Design, Automation

and Test in Europe Conf., pp. 596–602, 2001.

[4] G. Devarayanadurg and M. Soma, “Analytical Fault Modeling and Static

Test Generation for Analog ICs,” in Proc. Int. Conf. on Computer-Aided

Design, pp. 44–47, Nov. 1994.

[5] S. L. Farchy, E. D. Gadzheva, L. H. Raykovska, and T. G. Kouyoumdjiev, “Nullator-Norator Approach to Analogue Circuit Diagnosis Using

General-Purpose Analysis Programmes,” Int. Journal of Circuit Theory

and Applications, vol. 23, pp. 571–585, Dec. 1995.

[6] R. K. Gulati and C. F. Hawkins, IDDQ Testing of VLSI Circuits. Kluwer

Academic Publishers, 1993.

[7] W. L. Lindermeir, H. E. Graeb, and K. J. Antreich, “Analog Testing by

Characteristic Observation Inference,” IEEE Trans. Comp. Aided Design, vol. 23, pp. 1353–1368, June 1999.

[8] R. Rajsuman, IDDQ Testing for CMOS VLSI. Artech House, 1995.

[9] J. Figueras, “Possibilities and Limitations of IDDQ Testing in Submicron

CMOS,” in Proc. Innovative Systems in Silicon Conf., pp. 174–185, Oct.

1997.

[10] Z. Guo and J. Savir, “Analog Circuit Test Using Transfer Function

Coefficient Estimates,” in Proc. Int. Test Conf., pp. 1155–1163, Oct.

2003.

[11] V. Panic, D. Milovanovic, P. Petkovic, and V. Litovski, “Fault Location in

Passive Analog RC Circuits by measuring Impulse Response,” in Proc.

20th Int. Conf. on Microelectronics, pp. 12–14, Sept. 1995.

[12] S. Sindia, V. Singh, and V. D. Agrawal, “Polynomial Coefficient Based

DC Testing of Non-Linear Analog Circuits,” in Proc. 19th ACM Great

Lakes Symp. on VLSI, May 2009.

[13] R. Kondagunturi, E. Bradley, K. Maggard, and C. Stroud, “Benchmark

Circuits for Analog and Mixed-Signal Testing,” in Proc. 20th Int. Conf.

on Microelectronics, pp. 217–220, Mar. 1999.

Fault detected?

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes