L6: FSMs and Synchronization Acknowledgements:

advertisement

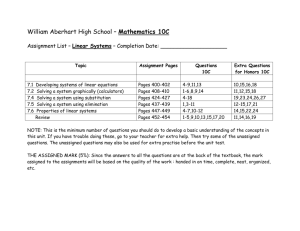

L6: FSMs and Synchronization Acknowledgements: Materials in this lecture are courtesy of the following sources and are used with permission. Rex Min J. Rabaey, A. Chandrakasan, B. Nikolic. Digital Integrated Circuits: A Design Perspective. Prentice Hall/Pearson, 2003. L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 1 Asynchronous Inputs in Sequential Systems What about external signals? Sequential System Can’t guarantee setup and hold times will be met! Clock When an asynchronous signal causes a setup/hold violation... I II III Q ? D Clock Transition is missed on first clock cycle, but caught on next clock cycle. Transition is caught on first clock cycle. Output is metastable for an indeterminate amount of time. Q: Which cases are problematic? Courtesy of Nathan Ickes. Used with permission. L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 2 Asynchronous Inputs in Sequential Systems All of them can be, if more than one happens simultaneously within the same circuit. Idea: ensure that external signals directly feed exactly one flip-flop Clocked Synchronous System Sequential System Async Input D Q D Q Q0 Clock D Q Q1 Clock Clock Courtesy of Nathan Ickes. Used with permission. This prevents the possibility of I and II occurring in different places in the circuit, but what about metastability? L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 3 Handling Metastability Preventing metastability turns out to be an impossible problem High gain of digital devices makes it likely that metastable conditions will resolve themselves quickly Solution to metastability: allow time for signals to stabilize Likely to be metastable right after sampling Very unlikely to be metastable for >1 clock cycle D Q D Q D Q Extremely unlikely to be metastable for >2 clock cycle Complicated Sequential Logic System Clock How many registers are necessary? Depends on many design parameters(clock speed, device speeds, …) In 6.111, one or maybe two synchronization registers is sufficient L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 4 Finite State Machines Finite State Machines (FSMs) are a useful abstraction for sequential circuits with centralized “states” of operation At each clock edge, combinational logic computes outputs and next state as a function of inputs and present state inputs + Combinational Logic present state n Q L6: 6.111 Spring 2006 + next state n CLK outputs FlipFlops D Introductory Digital Systems Laboratory 5 Two Types of FSMs Moore and Mealy FSMs are distinguished by their output generation Moore FSM: inputs x0...xn next state S+ Comb. Logic D n Flip- Q Flops Comb. Logic outputs yk = fk(S) CLK n present state S Mealy FSM: direct combinational path! inputs x0...xn S+ Comb. Logic D n FlipFlops outputs yk = fk(S, x0...xn) Comb. Logic Q CLK n S L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 6 Design Example: Level-to-Pulse A level-to-pulse converter produces a single-cycle pulse each time its input goes high. In other words, it’s a synchronous risingedge detector. Sample uses: Buttons and switches pressed by humans for arbitrary periods of time Single-cycle enable signals for counters Level to L P Pulse Converter Whenever input L goes from low to high... L6: 6.111 Spring 2006 CLK Introductory Digital Systems Laboratory ...output P produces a single pulse, one clock period wide. 7 State Transition Diagrams Block diagram of desired system: unsynchronized user input Synchronizer Edge Detector D Q Level to L Pulse P FSM D Q CLK State transition diagram is a useful FSM representation and design aid “if L=1 at the clock edge, then jump to state 01.” L=0 L=1 00 P=0 11 01 Low input, Waiting for rise High input, Waiting for fall Edge Detected! P=1 L=0 Binary values of states L=1 P=0 L=0 “if L=0 at the clock edge, then stay in state 00.” L6: 6.111 Spring 2006 L=1 Introductory Digital Systems Laboratory This is the output that results from this state. (Moore or Mealy?) 8 Logic Derivation for a Moore FSM Transition diagram is readily converted to a state transition table (just a truth table) 00 P=0 S1 0 0 0 0 1 1 L 0 1 0 1 0 1 L=1 11 01 Low input, Waiting for rise In L=1 L=1 L=0 Current State Edge Detected! P=1 L=0 High input, Waiting for fall P=0 L=0 S0 0 0 1 1 1 1 Next State S1+ 0 0 0 1 0 1 S0+ 0 1 0 1 0 1 Out P 0 0 1 1 0 0 Combinational logic may be derived by Karnaugh maps + S1S0 for S1 : 00 01 11 10 L 0 0 0 0 X 1 0 1 1 X + S1S0 for S0 : 00 01 11 10 L 0 0 0 0 X 1 1 1 1 X L6: 6.111 Spring 2006 S+ L Comb. Logic n D Flip- Q Flops CLK S S11++ == LS LS00 + S S00+ == LL Comb. Logic n S P S00 P == S S11S Introductory Digital Systems Laboratory P S0 S1 0 1 for P: 0 0 1 1 X 0 9 Moore Level-to-Pulse Converter inputs x0...xn next state S+ Comb. Logic D n Flip- Q Flops Comb. Logic outputs yk = fk(S) CLK n S S11++ == LS LS00 + S S00+ == LL present state S P S00 P == S S11S Moore FSM circuit implementation of level-to-pulse converter: L S0+ D CLK S1+ Q P Q D Q Q L6: 6.111 Spring 2006 S0 S1 Introductory Digital Systems Laboratory 10 Design of a Mealy Level-to-Pulse direct combinational path! S+ Comb. Logic n Comb. Logic D Flip- Q Flops CLK n S Since outputs are determined by state and inputs, Mealy FSMs may need fewer states than Moore FSM implementations 1. When L=1 and S=0, this output is asserted immediately and until the state transition occurs (or L changes). L P L=1 | P=1 L=0 | P=0 2 Clock 0 1 Input is low Input is high L=0 | P=0 L=1 | P=0 2. After the transition to S=1 and as long as L remains at 1, this output is 0. L6: 6.111 Spring 2006 1 Introductory Digital Systems Laboratory State Output transitions immediately. State transitions at the clock edge. 11 Mealy Level-to-Pulse Converter L=1 | P=1 0 1 Input is low Input is high L=0 | P=0 L=0 | P=0 L=1 | P=0 Pres. State In Next State Out S 0 0 1 1 L 0 1 0 1 S+ 0 1 0 1 P 0 1 0 0 Mealy FSM circuit implementation of level-to-pulse converter: P L S+ CLK D Q S Q S FSM’s state simply remembers the previous value of L Circuit benefits from the Mealy FSM’s implicit single-cycle assertion of outputs during state transitions L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 12 Moore/Mealy Trade-Offs Remember that the difference is in the output: Moore outputs are based on state only Mealy outputs are based on state and input Therefore, Mealy outputs generally occur one cycle earlier than a Moore: Moore: delayed assertion of P Mealy: immediate assertion of P L L P P Clock Clock State[0] State Compared to a Moore FSM, a Mealy FSM might... Be more difficult to conceptualize and design Have fewer states L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 13 Review: FSM Timing Requirements Timing requirements for FSM are identical to any generic sequential system with feedback Minimum Clock Period Combinational Logic inputs + present state n Minimum Delay outputs inputs + + next state present state Tlogic n Tcq Q CLK FlipFlops D n Combinational Logic outputs + next state Tlogic,cd n Tcq,cd Q Tsu CLK FlipFlops D Thold T T > Tcq + Tlogic + Tsu L6: 6.111 Spring 2006 Tcq,cd + Tlogic,cd > Thold Introductory Digital Systems Laboratory 14 The 6.111 Vending Machine Lab assistants demand a new soda machine for the 6.111 lab. You design the FSM controller. 30¢ All selections are $0.30. The machine makes change. (Dimes and nickels only.) Inputs: limit 1 per clock Q - quarter inserted D - dime inserted N - nickel inserted 30¢ COINS ONLY 25¢ 10¢ 5¢ Co Sprite Jolt Water LS163 Outputs: limit 1 per clock DC - dispense can DD - dispense dime DN - dispense nickel L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 15 What States are in the System? A starting (idle) state: idle A state for each possible amount of money captured: got5c got10c got15c ... What’s the maximum amount of money captured before purchase? 25 cents (just shy of a purchase) + one quarter (largest coin) ... got35c got40c got45c got50c States to dispense change (one per coin dispensed): got45c L6: 6.111 Spring 2006 Dispense Dime Dispense Nickel Introductory Digital Systems Laboratory 16 A Moore Vender Here’s a first cut at the state transition diagram. idle N=1 D=1 got5c N=1 D=1 got10c Q=1 N=1 D=1 got15c N=1 D=1 Q=1 got20c N=1 D=1 See a better way? So do we. Don’t go away... Q=1 got25c Q=1 N=1 D=1 * got30c * DC=1 Q=1 chg35 got35c DC=1 DN=1 got40c chg40 DC=1 DD=1 * * * * chg45 chg45b DD=1 DN=1 got50c chg50 chg50b DC=1 DD=1 DD=1 got45c DC=1 L6: 6.111 Spring 2006 * * Introductory Digital Systems Laboratory * 17 State Reduction idle Duplicate Duplicate states states have: have: The The same same outputs, outputs, and and The The same same transitions transitions idle N=1 D=1 There There are are two two duplicates duplicates in in our our original original diagram. diagram. got5c N=1 D=1 got10c D=1 D=1 Q=1 got20c D=1 Q=1 got30c DC=1 Q=1 D=1 * * chg40 DC=1 DD=1 got45c DC=1 17 states 5 state bits DN=1 got40c * * Q=1 got25c Q=1 * * DC=1 15 states 4 state bits rtn5 got35c DC=1 * DC=1 chg45 chg45b DD=1 DN=1 * got45c chg50 chg50b DC=1 DD=1 DD=1 Introductory Digital Systems Laboratory * * DD=1 rtn15 DD=1 * * rtn20 got50c DC=1 DN=1 rtn10 got40c got50c L6: 6.111 Spring 2006 * got30c DC=1 * * Q=1 chg35 got35c DC=1 got20c N=1 Q=1 * Q=1 N=1 N=1 D=1 Q=1 got15c N=1 got15c got25c got10c N=1 N=1 D=1 got5c N=1 D=1 N=1 D=1 D=1 Q=1 N=1 D=1 N=1 * DD=1 18 Verilog for the Moore Vender Comb. Logic n D State Q Comb. Logic Register module mooreVender (N, D, Q, DC, DN, DD, clk, reset, state); input N, D, Q, clk, reset; output DC, DN, DD; output [3:0] state; reg [3:0] state, next; CLK n States defined with parameter keyword FSMs are easy in Verilog. Simply write one of each: State register (sequential always block) Next-state combinational logic (comb. always block with case) IDLE = 0; GOT_5c = 1; GOT_10c = 2; GOT_15c = 3; GOT_20c = 4; GOT_25c = 5; GOT_30c = 6; GOT_35c = 7; GOT_40c = 8; GOT_45c = 9; GOT_50c = 10; RETURN_20c = 11; RETURN_15c = 12; RETURN_10c = 13; RETURN_5c = 14; State register defined with sequential always block Output combinational logic block (comb. always block or assign statements) L6: 6.111 Spring 2006 parameter parameter parameter parameter parameter parameter parameter parameter parameter parameter parameter parameter parameter parameter parameter always @ (posedge clk or negedge reset) if (!reset) state <= IDLE; else state <= next; Introductory Digital Systems Laboratory 19 Verilog for the Moore Vender Next-state logic within a combinational always block always @ (state or N or D or Q) begin case (state) IDLE: if else if else else (Q) next = GOT_25c; (D) next = GOT_10c; if (N) next = GOT_5c; next = IDLE; GOT_5c: if else if else else (Q) next = GOT_30c; (D) next = GOT_15c; if (N) next = GOT_10c; next = GOT_5c; GOT_10c: if else if else else (Q) next = GOT_35c; (D) next = GOT_20c; if (N) next = GOT_15c; next = GOT_10c; GOT_15c: if else if else else (Q) next = GOT_40c; (D) next = GOT_25c; if (N) next = GOT_20c; next = GOT_15c; GOT_20c: if else if else else (Q) next = GOT_45c; (D) next = GOT_30c; if (N) next = GOT_25c; next = GOT_20c; L6: 6.111 Spring 2006 GOT_25c: if (Q) next = GOT_50c; else if (D) next = GOT_35c; else if (N) next = GOT_30c; else next = GOT_25c; GOT_30c: GOT_35c: GOT_40c: GOT_45c: GOT_50c: next next next next next RETURN_20c: RETURN_15c: RETURN_10c: RETURN_5c: = = = = = next next next next IDLE; RETURN_5c; RETURN_10c; RETURN_15c; RETURN_20c; = = = = RETURN_10c; RETURN_5c; IDLE; IDLE; default: next = IDLE; endcase end Combinational output assignment assign DC = (state state state assign DN = (state assign DD = (state state endmodule == == == == == == Introductory Digital Systems Laboratory GOT_30c || state == GOT_35c || GOT_40c || state == GOT_45c || GOT_50c); RETURN_5c); RETURN_20c || state == RETURN_15c || RETURN_10c); 20 Simulation of Moore Vender State Output L6: 6.111 Spring 2006 idle got5c got20c got15c idle rtn15 rtn5 got45c C 10¢ Introductory Digital Systems Laboratory 5¢ 21 Coding Alternative: Two Blocks Next-state and output logic combined into a single always block always @ (state or N or D or Q) begin DC = 0; DD = 0; DN = 0; // defaults case (state) IDLE: else else else if (Q) if (D) if (N) next = next = GOT_25c; next = GOT_10c; next = GOT_5c; IDLE; GOT_5c: else else else if (Q) if (D) if (N) next = next = GOT_30c; next = GOT_15c; next = GOT_10c; GOT_5c; GOT_10c: else else else if (Q) if (D) if (N) next = next = GOT_35c; next = GOT_20c; next = GOT_15c; GOT_10c; GOT_15c: else else else if (Q) if (D) if (N) next = next = GOT_40c; next = GOT_25c; next = GOT_20c; GOT_15c; GOT_20c: else else else if (Q) if (D) if (N) next = next = GOT_45c; next = GOT_30c; next = GOT_25c; GOT_20c; GOT_25c: else else else if (Q) if (D) if (N) next = next = GOT_50c; next = GOT_35c; next = GOT_30c; GOT_25c; L6: 6.111 Spring 2006 GOT_30c: GOT_35c: GOT_40c: GOT_45c: GOT_50c: begin DC = end begin DC = end begin DC = end begin DC = end begin DC = end 1; next = IDLE; 1; next = RETURN_5c; 1; next = RETURN_10c; 1; next = RETURN_15c; 1; next = RETURN_20c; RETURN_20c: begin DD = end RETURN_15c: begin DD = end RETURN_10c: begin DD = end RETURN_5c: begin DN = end 1; next = RETURN_10c; 1; next = RETURN_5c; 1; next = IDLE; 1; next = IDLE; default: next = IDLE; endcase end Introductory Digital Systems Laboratory 22 FSM Output Glitching FSM state bits may not transition at precisely the same time Combinational logic for outputs may contain hazards Result: your FSM outputs may glitch! during this state transition... got10c D=1 got20c ...the state registers may transtion like this... ...causing the DC output to glitch like this! 0010 got10c 0 0110 got30c 1 0100 got20c 0 glitch assign DC = (state == GOT_30c || state == GOT_35c || state == GOT_40c || state == GOT_45c || state == GOT_50c); If the soda dispenser is glitch-sensitive, your customers can get a 20-cent soda! L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 23 Registered FSM Outputs are Glitch-Free Output Comb. Logic inputs NextState Comb. Logic registered outputs D Output Q Registers CLK next state State Q Registers D n CLK n present state S Move output generation into the sequential always block Calculate outputs based on next state L6: 6.111 Spring 2006 reg DC,DN,DD; // Sequential always block for state assignment always @ (posedge clk or negedge reset) begin if (!reset) state <= IDLE; else if (clk) state <= next; DC <= (next next next DN <= (next DD <= (next next end == == == == == == GOT_30c || next == GOT_35c || GOT_40c || next == GOT_45c || GOT_50c); RETURN_5c); RETURN_20c || next == RETURN_15c || RETURN_10c); Introductory Digital Systems Laboratory 24 Mealy Vender (covered in Recitation) A Mealy machine can eliminate states devoted solely to holding an output value. idle N=1 D=1 got5c N=1 D=1 got10c Q=1 N=1 D=1 got15c Q=1 N=1 D=1 * * idle got20c D=1 N=1 N=1 D=1 got25c Q=1 Q=1 | DC=1 N=1 D=1 got30c got35c DC=1 D=1 * rtn5 DN=1 got40c rtn10 DC=1 DD=1 got45c DC=1 * * DC=1 rtn15 DD=1 * D=1 Q=1 | DC=1 got15c Q=1 | DC=1 Q=1 | DC=1 got20c DD=1 D=1 N=1 | DC=1 L6: 6.111 Spring 2006 got10c rtn5 rtn10 * | DD=1 N=1 * rtn20 * * | DN=1 N=1 D=1 | DC=1 got50c got5c * | DD=1 N=1 Q=1 DC=1 Q=1 Q=1 D=1 | DC=1 N=1 got25c rtn15 rtn20 * | DD=1 Q=1 | DC=1 Introductory Digital Systems Laboratory 25 Verilog for Mealy FSM module mealyVender (N, D, Q, DC, DN, DD, clk, reset, state); input N, D, Q, clk, reset; output DC, DN, DD; reg DC, DN, DD; output [3:0] state; reg [3:0] state, next; parameter parameter parameter parameter parameter parameter parameter parameter parameter parameter IDLE = 0; GOT_5c = 1; GOT_10c = 2; GOT_15c = 3; GOT_20c = 4; GOT_25c = 5; RETURN_20c = 6; RETURN_15c = 7; RETURN_10c = 8; RETURN_5c = 9; // Sequential always block for state assignment always @ (posedge clk or negedge reset) if (!reset) state <= IDLE; else state <= next; L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 26 Verilog for Mealy FSM always @ (state or N or D or Q) begin DC = 0; DN = 0; DD = 0; case (state) IDLE: else else else if (Q) if (D) if (N) next = // defaults next = GOT_25c; next = GOT_10c; next = GOT_5c; IDLE; For state GOT_5c, output DC is only asserted if Q=1 GOT_25c: if (Q) DC = end else if (D) DC = end else if (N) DC = end else next = GOT_5c: if (Q) begin DC = 1; next = IDLE; end else if (D) next = GOT_15c; else if (N) next = GOT_10c; else next = GOT_5c; GOT_10c: if (Q) DC = end else if (D) else if (N) else next = GOT_15c: if (Q) DC = end else if (D) else if (N) else next = GOT_20c: begin 1; next = RETURN_5c; RETURN_20c: next = GOT_20c; next = GOT_15c; GOT_10c; RETURN_15c: begin 1; next = RETURN_10c; RETURN_10c: next = GOT_25c; next = GOT_20c; GOT_15c; RETURN_5c: if (Q) begin DC = 1; next = RETURN_15c; end else if (D) begin DC = 1; next = IDLE; end else if (N) next = GOT_25c; else next = GOT_20c; L6: 6.111 Spring 2006 begin 1; next = RETURN_20c; begin 1; next = RETURN_5c; begin 1; next = IDLE; GOT_25c; begin DD = end begin DD = end begin DD = end begin DN = end 1; next = RETURN_10c; 1; next = RETURN_5c; 1; next = IDLE; 1; next = IDLE; default: next = IDLE; endcase end endmodule Introductory Digital Systems Laboratory 27 Simulation of Mealy Vender State Output idle got5c got20c got15c rtn5 idle rtn15 C 10¢ 5¢ (note: outputs should be registered) L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 28 Delay Estimation : Simple RC Networks V in VDD 50% Vin t Vout CL tpHL V out tpLH 90% V DD 50% V DD t 10% tf R on tr (b) High-to-low (a) Low-to-high review V out V out CL vin R vout C CL R on tp = ln (2) τ = 0.69 RC L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 29 Clocks are Not Perfect: Clock Skew CLout In Combinational Logic D Q Wire delay D Q ClkD Clk CLK CLKD δ>0 T> Tcq + Tlogic + Tsu - δ Tcq,cd + Tlogic,cd > Thold + δ L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 30 Positive and Negative Skew In CLK R1 R2 Combinational Logic D Q Combinational Logic D Q tCLK1 tCLK2 TCLK + δ R3 D Q TCLK 1 • • • CLK1 3 δ tCLK3 CLK2 delay 2 delay 4 δ + th (a) Positive skew Launching edge arrives before the receiving edge In R1 D Q Combinational Logic R2 Combinational Logic D Q R3 TCLK + δ D Q ••• 1 CLK1 tCLK1 tCLK2 delay TCLK 3 tCLK3 delay CLK CLK2 2 δ 4 (b) Negative skew Receiving edge arrives before the launching edge L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 31 Clocks are Not Perfect: Clock Jitter TCLK 2 CLK 1 5 4 3 -tjitter In REGS tjitter 6 Combinational Logic CLK tc-q, t c-q, cd tsu, thold tjitter t logic t logic, cd T CLK – 2t jitter > tc – q + t log ic + t su or T > tc – q + tlog ic + tsu + 2t jitter L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 32 Summary Synchronize all asynchronous inputs Use two back to back registers Two types of Finite State Machines introduced Moore – outputs are a function of current state Mealy – outputs a function of current state and input A standard template can be used for coding FSMs Register outputs of combinational logic for critical control signals Clock skew and jitter are important considerations L6: 6.111 Spring 2006 Introductory Digital Systems Laboratory 33