A Low-Power Acoustic Periodicity Detector Chip for Voice and Engine Detection

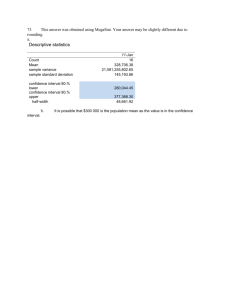

advertisement

A Low-Power Acoustic Periodicity Detector Chip for Voice and Engine Detection Hisham Abdalla1,2 Timothy Horiuchi1,2,3 1Electrical and Computer Engineering, 2Institute for Systems Research, 3Neuroscience and Cognitive Sciences Program Circuit for Generating Timing Signals Introduction Vdd The detection of voices or the rumble of engines is a desirable function in many different devices from toys to smart homes to military applications. Typical approaches involving frequency-domain computation are quite computationally intensive and require a significant power and computational budget. In an effort to construct a very low-power detector capable of acting as a wake-up signal for other systems, we have designed a simple, low-power (1.5uW) analog VLSI circuit that detects periodicity in the time-domain envelope of the acoustic signal. Vdd Vdd reset Vdd Vdd _ _ __ _ sp ik e 100f b1 VL Vdd Vdd Vn-1 300f Ith Ith Vb Vbias re se t p u ls e = s p ik e 100f Vdd Vdd out Ib Vdd sa m p le p u lse Vth2 Vth VH Vdd sa m p le Vdd Vdd Vb Vdelr __ _ _ _ sp ik e Interval Comparator Interval Limiter Vdd out Vn M2 Vx Vdd I1 Vy Vn-1 I1 I2 I2 M1 M2 M1 Vdelo System Block Diagram Peak Detector Signal 200f Interval To Voltage Spike Generator g u a rd b a n d On the negative edge of spike , three independent ramps are triggered with different slopes. As each ramp crosses the threshold of an inverter, a pulse is generated. The first ramp starts the sampling process by pulling the sample pulse low. The second ramp pulls turn off sample high, turning off the sampling pulse. The third ramp turns on the reset pulse. The guard interval can be adjusted to ensure that both the sampling process and the interval comparison have ended before the onset of the reset pulse. Timing Signals Sample Comp tu rn o ff sa m p le b2 Interval to Voltage Conversion, Sampling and Storing Intervals Detect Shift Register Logic Interval Limiter Memory Current interval Vdd Previous interval (memory) Vdd Vdd Vdd The interval limiter defines an acceptance zone defined in terms of voltages VL and VH. If the stored interval Vn-1 satisfies the inequality VL<Vn-1<VH, then the two current mirrors will ensure that the two output transistors, M1 and M2, are on pulling the output of the circuit low indicating a valid interval. If the inequality is not satisfied, one of the two output transistors will be off, the output will be pulled up high indicating an invalid interval. The interval comparator decides whether the two “inter-spike intervals”, Vn and Vn-1, match. Vb sets a current Ib in the differential pair which is split into I1 and I2. Vth sets Ith such that Ith < Ib/2. When the two inputs match, both I1 and I2 are strong enough to hold Vx and Vy low turning off M1 and M2 and the output is high indicating matched intervals. When the inputs do not match, one of the two output transistors, M1 and M2, is turned on pulling the output low indicating non-matching intervals. Vdd Vdd A valid interval together with matching intervals is defined as a hit. Our chip can count up to five consecutive hits. Vdd Vramp The circuit takes the input through a peak detector and generates a spike at the onset of a peak. The inter-spike intervals are then converted to a voltage. That voltage is then sampled and stored to be compared with the new sampled voltage. A valid interval that matches (as decided by the interval comparator stage) is called a hit. The circuit can store up to five consecutive hits. Peak Detector and Spike Generator Circuits Vdd Vdd Vin Vdd Vdd + wide-range transamp - o1 Vb3 M1 o2 o2 _____ spike Peak Detector Output Output Vd transamp2 + reset M2 sample transamp1 Vbs M1 Vc out out V- + V- Chip Testing Results V+ V+ C4 C2 sample 0.4pF Sampling Interval to Voltage current interval Conversion C3 Vbs 2pF mean number of hits (in 4 minutes) 2pF transamp1 Transconductance amplifier Storing previous interval transamp2 Transconductance amplifier An inter-spike interval is linearly converted to a voltage by means of a voltage ramp. A voltage ramp is generated on C2 as it is being charged by a constant current source (M1). Vramp controls the slope of the ramp. When a spike is triggered, two events take place; First, the voltage ramp Vc2 is sampled when the sample pulse turns on the follower (transamp1). The sampled inter-spike interval Vn is temporarily stored on C3. Second, the reset pulse turns M2 on discharging C2 and the capacitor starts charging up again. The storage process occurs through a weakly biased follower (transmp2), this allows Vn to slowly be copied to C4 and stored as Vn-1. mean number of hits (in 4 minutes) 3 hits 3 hits Background Noise Level: -28 dB 5 hits 5 hits Noise Power (dB) SNR (dB) Chip response to a White Gaussian Noise input, lowpass filtered at 1KHz Chip response to a 20 Hz sinusoidal input, lowpass filtered at 1 KHz C1 speaker Input Vrefractory S p ik e Current Source Speech “ z e ro ” Spike Peak detector: when peak detector’s output drops below input, M1 is turned on charging C1 to Vin Vdd Vdd Edge detector: the rising edge of o2 is used to generate a voltage spike. Sampled Interval Vn D e te c t ( 3 h it s ) Voltage ramp V c3 Vdd V n = 2 .0 5 V P itc h = 1 8 0 H z Vdd Vb V+ (Ch1) o1 Spike (Ch2) (yellow) (purple) (blue) Dual-output, wide-range transconductance amplifier (transamp) Previous interval Input o2 V- Oscilloscope trace demonstrates the peak detector’s response to an input signal and the spike generation process Oscilloscope traces illustrate the interval-to-voltage conversion process by means of a voltage ramp, as well as the sampling and storing processes. microphone S a m p le d In t e r v a l Peak Detector Output (Ch3) Storage process (slow follower) Current interval V n = 2 .1 9 3 V P itc h = 1 6 5 H z Response to the speech utterance “zero”: No detection during the ‘noisy’ onset. Detects the voiced segments.The sampled interval can be used to estimate the pitch. Chip being tested in the field We thank Shihab Shamma for early discussions of this work and the Signal Systems Corporation for providing various acoustics recordings during the design period of this project. We also thank the MOSIS fabrication service for its continuous support in providing fabrication facilities. This work was supported by a contract with DARPA (Air Coupled Microsensors-0001400C0315)