Implementation of Power Efficient Decoding Technique of Polar Code

advertisement

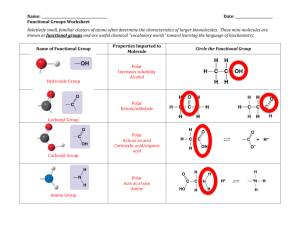

International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 8 - May 2014 Implementation of Power Efficient Decoding Technique of Polar Code Sapna R. Makvana, Asst.Prof. Brijesh vala, Asst.Prof. Ankit Pancholi ME-CE Dept,PIET, Waghodiya, Vadodara. Gujrat.(INDIA) ,CSE Dept,PIET, Waghodiya, Vadodara. Gujrat.(INDIA) EC Dept, SNPIT & RC, Bardoli, Surat.(INDIA) Abstract-In information theory and coding, good error control performance requires the scheme to be selected based on the characteristics of the communication channel & the coding algorithms used in it. Polar codes are one of them which are the first ones to achieve channel capacity of any binary discrete memory less channel (B-DMC) with an explicit construction. In the research, the method relates with polar codes, channel polarization and encoding & decoding of polar code is measured that in the live structure of polar code when BER gets increase, channel capacity is satisfied but overall power of data transmission in channel gets increase. So here the main issue is related with the power consumption. Encoding & decoding construction of polar codes is based on XOR-XNOR gates which play an important role in digital systems including arithmetic and encryption circuits. Now the XOR circuits’ design which uses 6 transistors instead of conventional structure is designed and it is suitable for low-voltage and low-power application by achieving Power consumption, Power Dissipation and power-delay product (PDP). So by using this design phenomenon of XOR gate it is possible to achieve lower power consumption in data transmission and construct power efficient encoding and decoding of polar codes. Keywords-Polar Code, XOR-XNOR Gate, Power Consumption, Power Delay Product (PDP), Delay, Power Dissipation. 1. INTRODUCTION Due to the increasing use of portable systems e.g. notebook computers, personal digital assistants, and cellular phones, power is rapidly becoming as important a parameter as area and speed in the design of such systems [9]. The limited power supply ability of present battery equipment has made power consumption an important figure in portable devices So, It is necessary to achieve the power consumption and delay in real time applications for improved use in day to day life and get better generosity. There is clearly need for new technology and ISSN: 2231-5381 design phenomenon that would achieve ultra low power dissipation below performance & cost constrains. The two central topics of information theory are the compression and the transmission of data. Shannon, in his decisive work, dignified both these problem and determined their fundamental limits. Since then the main goal of coding theory has been to find practical schemes that approach these limits. Polar codes, invented by Arıkan, are the first “practical” codes that are known to achieve the capacity for a large class of channels [1]. The encoding as well as the decoding operation of polar codes can be implemented with O (N log N) complexity, where N is the block length of the code [5]. For decoding, he considers applying a simple linear transform to the channel inputs before transmission and a successive cancellation decoder at the output [2]. So by using polar code the complexity and bandwidth is reduced and data rate and channel capacity is increased. But at the other side overall power of data transmition gets increased. Now when the information bits are encoded and decoded in the channel they are XORed with each other. In encoding structure of polar codes, there is XOR operation is performed at channel combining stage of channel polarization. So here the point of attention is the design criteria of XOR gates. The increasing speed and complexity of today’s designs implies a considerable increase in the power consumption problem. To meet this challenge, researchers have developed many different design techniques to reduce power. In brief, by concentrating and take XOR gates as one parameter of the issue of power consumption; it has gone through substantial improvement in power consumption, delay, power delay product, speed and size with its different circuit designs [3]. By adding this approach in polar codes’ encoding structure with XOR gate’s new circuit design, it might be possible to achieve power consumption at transmission of information of polar code within the channel. Further the rest of paper is organized as follows: section II deals with a brief technical description of Polar codes with its encoding and decoding part. Section III provides description about proposed work. Section IV provides technical comparison of conventional & proposed circuit designs of XOR http://www.ijettjournal.org Page 373 International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 8 - May 2014 gate with result analysis and finally section VI delivers the conclusions. II. POLAR CODE Polar codes are recently invented in 2008 [7]. This code can achieve the symmetric capacity which is the highest capacity of the channel with same probabilities for any given Binary Discrete Memoryless Channel (B-DMC) [5]. The encoding and decoding capacity of polar code is O (N log N). Here N is Block Length of code and the complexity is n log N. so this is a big achievement and this can solve the big open problem of Coding Theory. noiseless channel (called good bit channel) approaching the capacity of I (W) or into a pure noise channel (called bad bit channel) approaching 1- I (W) [1].So by using this sort of polarization method the construction of Polar codes is done in which data is send through those channel with high capacity and fix the inputs through those channels with low capacity. 2.1 Encoding of Polar code Basically, polar codes were constructed using a generator matrix created using the Kronecker power of the base 10 matrix = to the block of N= 2n bits. This construction 11 method yields polar codes whose lengths are powers of two. For example, the generator matrix of an n=8 polar codes are: = = ⨂ 0 0 0 0 0 0 0 Fig 2.2 Combining of Channels 10000000 ⎡ 11000000 ⎤ ⎢ 10100000 ⎥ ⎢ ⎥ 11110000 ⎥ = ⎢ ⎢ 10001000 ⎥ ⎢ 11001100 ⎥ ⎢10101010⎥ ⎣ 11111111 ⎦ Fig 2.1 Generator Matrix of n=8 Generally what is done here, that the information bits of Polar codes work by encoding an information vector u into a codeword X by multiplying it with a generator matrix G, using X= u.G. This resulting vector is then transmitted over a communication channel. A decoder receives a noisy version of X called Y from the output of the channel. This decoder then estimates the original information vector u as showen in Figure 2. 2.2 Channel Polarization A method is proposed to constrict code sequences that achieve the symmetric capacity of any given B-DMC is called channel polarization, [7]. It works with two operations, one is channel combining and other is channel splitting [1]. Channel Polarization synthesize N channel of B-DMC then it split into ISSN: 2231-5381 2.3. Belief Propagation Decoding Algorithm Thought A Successive cancelation decoding is the capacity-achieving property of the polar code, Belief Propagation decoding obtain better BER performance while keeping the decoding complexity at O (N log N). The BP is an algorithm that helps to solve inference in graphical models. More accurately, it provides estimates of the subsequent marginal distributions of the variables, called beliefs. To obtain the beliefs, the BP passes messages iteratively between the variable nodes and the check nodes, according to their neighborhood dependence. Belief propagation decoding is easily obtained by adding check nodes to the polar code as it is shown in figure 2.3 for length n=8.it is also called “Tanner Graph” of the code. The graph is formed of columns of variable nodes and check nodes. In the tanner graph, each variable node v has a set of check nodes as its neighbors, denoted by Cv. The check nodes in Cv also have a set of variable nodes Vv as their neighbors from which we exclude v. We refer to Vv as”depth-2 neighborhood” of v and we call the members of Vv”depth-2 neighbors” of v. In [6] they are particularly interested in the analysis of”stopping sets” in the tanner graph of the polar code, A stopping set is a set of variable nodes such that every neighboring check node of the set is connected to at least two variable nodes in the set. Fig.2.3 shows an example of the stopping set in the polar codes’ graph. http://www.ijettjournal.org Page 374 International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 8 - May 2014 III PROPOSED WORK In this work, the issue of interest is methods of modeling the power consumption in XOR dominated circuits. The primary concern to design XOR-XNOR gate is to obtain low power consumption and delay in the critical path and full output voltage swing with low number of transistors to implement it. XOR-XNOR functions using different number of circuit techniques and approaches with different circuit designs they vary in methodologies and transistor count to improve the circuit performance in term of speed, density and power. Fig 2.3 Normal realization of the encoding graph for N = 8. An example of the stopping set is shown with white variable and check nodes [6] It is easy to see that if all the variable nodes in a stopping set are erased, then none of them can be decoded in belief propagation. Further, if any of the variable nodes in a stopping set is decoded then all of them can be decoded [6]. As a result, the probability of decoding error is closely related to the probability of having a stopping set with erased variable nodes. Since the stopping set with the minimum number of variable nodes, called ”minimal stopping set”, is more probable to be erased than larger stopping sets, it plays the dominant role in the error probability. It is also referred that Polar codes are based on the observation that specific bits in the input data going to be better protected from noise than others. As described in [2] that as the code length N grow larger, individual bits in the input word tend to become either very well or very poorly protected. Polar codes are constructed by identifying those well-protected bit indices in the information vector and using them to transmit information. They are called information set while the remaining positions form the frozen set, which is usually set to a predetermined value known by both the encoder and the decoder. So here channel capacity is achieved but the overall power of data transmit ion gets increased. Now when bit are encoded and decoded in the channel they are XORed with each other or I can say that in encoding and decoding structure of polar codes, there is the XOR operation is performed. At channel combining stage of channel polarization which is shown in fig.3.1 which shows the first recursion manner of n=1 for channel Wn where N=2n, N>=0. Fig.3.1 combining of channels W2 [7] Fig.2.4 Decoding Result of Polar Code with BP algorithm for BER Vs SNR In fig.2.4 the value of m=8 and n=16 and the iteration is 80.It can be seen from the simulated graph that BER is 10 . while SNR is 3.5 db. So, by using both this algorithm we can decode the code bits which are output of the transmition channel. But here it is noticed that BP performs better than SC in terms of BER. ISSN: 2231-5381 It is illustrated using a graph representation in that figure the information vector u is presented on the left-hand side of the graph and the resulting decoded codeword x is obtained on the right-hand side. The ⊕ symbols represent XOR operations. The XOR gates used in this structure has the circuit design with 8transistor logic. Description: XOR and XNOR gate plays an important role in digital systems including arithmetic and encryption circuits. The XOR and XNOR gate functions are shown in Table 2.3and denoted by http://www.ijettjournal.org Page 375 International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 8 - May 2014 and respectively. The logic expression for XOR and XNOR are A B = A'B + AB' & A B = A'B’ + AB [5] Table I XOR and X-NOR gate function [5] Numerous designs were reported to realize the XOR-XNOR functions using different number of circuit techniques and approaches. They vary in methodologies and transistor count to improve the circuit performance in term of speed and density. It can be clear from the given figures of XOR-XNOR circuit designs with different no. of transistor. The proposed design of XOR-XNOR gate using six transistors is shown in Figure 3.3. It uses a concept of pass transistor and CMOS inverter. The inverter is used as a driving output to achieve a perfect output swing. Vdd connection to transistor M3 and M4 are use to drive a good output of ‘1’. Transistor M4 is used to drive the output signal when XOR output ‘0’ [5]. It offers the lowest power dissipation at a low supply voltage And Better performance especially in low supply voltage compared to the previous designs by reducing the no. of transistor in circuit design. Thus, the proposed circuit is suitable for low-voltage and low-power application. By merging This approach in polar codes’ conventional encoding structure with XOR gate’s new circuit design we will try to achieve overall power consumption with polar codes at transmission of information within the channel. This implementation may be used for various kind of data transmit ion in future when where accurate channel capacity is required and power is an essential factor in that. 3.1 XOR gate circuit design with 8- transistor Fig 3.2 XOR-XNOR gate using 8 transistors [5] Now in [5] Ahmad and hasan proposes a new design of combination of XOR-XNOR gate using 6-transistors for low power applications. Fig.3.4 MICROWIND circuit design of XOR gate with 8- transistor Fig 3.3 Proposed XOR-XNOR Gates Using 6 Transistors [5] ISSN: 2231-5381 http://www.ijettjournal.org Page 376 International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 8 - May 2014 3.2 Simulation result of XOR circuit with 8-transistor 3.4 Simulation result of XOR circuit with 6 –transistor Fig.3.7 Simulation Result of XOR gate with 6- transistor Fig.3.5 Simulation Result of XOR gate with 8- transistor Sr.No Performance Measures 1 Power Dissipation Memory occupied Delayed in Out put Power Delay Product 3.3 XOR gate circuit design with 6 -transistor 2 3 4 Design of XOR with 8 transistors 6.9 µW Design of XOR with 6 transistors 1.3% 1.2 % 6ns 5ns 41.4ns 12.55ns 2.51µW IV RESULT ANALYSIS Table II Performance Measures of both XOR circuit design Fig.3.6 MICROWIND circuit design of XOR gate with 6- transistor ISSN: 2231-5381 Newly design of XOR with 6 transistors has 2.51 µW power dissipation, memory occupied space of 1.2 % , Delayed in output of 5ns and power delay product 12.55ns against the conventional XOR with 8 transistors has 6.9 µW power dissipation, memory occupied space 1.3% ,delayed output 6ns and power delay product 41.44 ns respectively. Thus new design provides varied differences in feature based Design of XOR which ultimate makes it more efficient to operate, low in power consumption and hence cheaper and efficient alternative to conventional design of XOR. http://www.ijettjournal.org Page 377 International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 8 - May 2014 Table III List of Different Polar Code Circuit with Transistor Requirement SR. No. 1. 2. 3. 4. 5. Design of Polar code Circuits 8 – bit Encoders SC8 bits Butterflies SC8 bits Pipelining SC-8 bits Line Belief Propagation Numbers of Transistors Required 12 12 REFERENCE [1] Ahmed Elshahawy, Bahram Honary “An overview on Channel Polarization and Polar Codes” ISBN: 978-1-902560-26-7 © 2012. [2] Peter Trifonov “Efficient Design and Decoding Of Polar Codes”, Member, IEEE IEEE Transactions On Communications, Vol. 60, No. 11, November 2012. 7 [3] Hardware architectures for successive cancellation decoding by Leroux,C McGill Univ., Montreal, QC, Canada,IEEE- 978-1-4577-0539-©2012. 4 8 [4] A. Eslami and H. Pishro-Nik “A Practical Approach to Polar Codes”, IEEE International Symposium on Information Theory Proceedings, 2011. Here above mentioned table shows no. of transistors used, if we used newly designed XOR with 6 transistors for belief propagation then we have to use just 48 transistors (8*6) instead of conventional XOR design 64 transistors (8*8). Thus we able to save 16 transistors for transferring 8 information bits for belief propagation decoder, same way by adopting newly formed circuit design for the use of large no. of data transferring of information bits and apply this calculation, we can reduce the overall requirement of transistor and reduce the overall power consumption on data transmition. [5] Nabihah Ahmad Rezaul Hasan “A New Design of XOR-XNOR gates for low power Application” International Conference on Electronic Devices, Systems & Applications (ICEDSA), 2011. [6] A. Eslami and H. Pishro-Nik. “On the Performance of Polar Codes under Belief Propagation Decoding”-2010. [7] Jun Li1, Ying Guo and Moon Ho Lee “Iterative Decoding Algorithm in the Turbo, LDPC, Polar Codes”, 2010. [8] Erdal Arıkan “Channel Polarization: A Method for Constructing CapacityAchieving Codes ” ISIT 2008, Toronto, Canada, July 6 - 11, 2008. [9] Yibin Ye, Kaushik Roy and Rolf Drechsler “Power Consumption in XORBased Circuits”,IEEE,0-7803-5012-X/99/@1999. V CONCLUSION & FUTURE ENHANCEMENT Polar codes are the first provably capacity achieving codes for any symmetric binary-input discrete memory less channels (BDMC) which have low complexity encoding and decoding algorithms O (N log N). But In practice, channel properties may change with time, therefore it is important to analyze the performance of the constructed code for channel model e.g. BEC or BSE with different noise level. Also the main point of attention is Problems with previous reported XOR design which are: Power Consumption, Power dissipation &PDP so there is a clear need of modern design of XOR-XNOR gate to obtain low power consumption and delay so the approach of power consumption is also taken as most important factor into account in the encoding and decoding structure of polar code. Here the proposed XOR circuit is suitable for low-voltage and low-power application which is helpful in future to consume low power for data transmition in the channel with Polar code. ACKNOWLEDGEMENTS I would like to sincerely thank Mr. Brijesh Vala & Mr. Ankit pancholi for all his attentiveness, guidance, support, motivation and inspiration throughout this work. ISSN: 2231-5381 http://www.ijettjournal.org Page 378