Power Optimized Differential Conditional Capturing Flip-Flop for Clock Distribution Network

advertisement

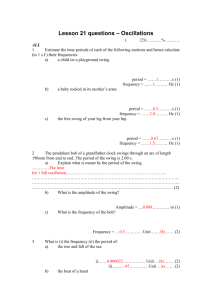

International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 1 - May 2014 Power Optimized Differential Conditional Capturing Flip-Flop for Clock Distribution Network Anandkumar.M1, Arun.T2, Kanagaraj.G3,Sampath kumar.K4 Assistant Professor & ECE & Maharaja institute of technology Abstract- The operation of low/full swing LC resonant clocking scheme helps in reducing the overall power of the system by introducing a modern new flip-flop. The proposed dual mode low/full-swing differential conditional capturing flip-flop (LF-CCFF) operates with a low/fullswing sinusoidal clock through the utilization of reduced swing inverters at the clock port. The functionality of the proposed (LF-CC) flip-flop was verified at extreme corners through simulation with parasitic extracted from layout. The LF-CCFF enables 5.5% reduction in power compared to the single mode full-swing flip-flop with 26% area overhead. The power has been calculated by using TSMC 180-nm CMOS technology. In addition, a frequency dependent delay associated with driving pulsed flip-flops with a low/full-swing sinusoidal clock has been characterized. The LF-CCFF has compared to the fullswing flip-flop both having the same setup time for a 100 MHz sinusoidal clock. The functionality of the proposed flip-flop was tested and verified by using the LF-CCFF in a dual-mode multiply and accumulate (MAC) unit fabricated in TSMC 70-nm CMOS technology. Index terms— Delay, Flip-flop, low swing, Full swing, power, resonant clock. clock double-edge triggered flip-flop has enabled 78% power savings in the CDN. We have to lookout a similar approach to the one proposed in [4] which the clock buffers are removed to allow the global and local clock energy to resonate between the inductor and entire clock capacitance including the receiving end flip-flops thus enabling maximum power savings. In addition, eliminate the clock buffers simplifies LC low-swing clocking since only reduced swing buffers are used at the flipflop gate and not in intermediate levels within the clock tree [7].In this paper, we introduce a low/full-swing differential conditional capturing flip-flop (LF-DCCFF) for use in low/full-swing LC resonant CDNs. As far as the authors know, this is the third application of low/full-swing clocking to LC resonant CDNs. Already low swing and full swing are available in the LC Network. In our approach, no additional power supply is required to achieve low/full-swing clocking. We have characterized a frequency dependent delay associated with driving the pulsed flip-flop with a low/full-swing sinusoidal clock. We also provide measurement results from an integrated test chip fabricated in TSMC 180-nm CMOS technology. II. EXISTING SYSTEM I. INTRODUCTION The clock distribution network (CDN) in digital integrated circuits distributes the clock signal which acts as a timing reference controlling data flow within the system. Since the clock signal has the highest capacitance and operates at high frequencies, the CDN consumes a large amount of total power in synchronous systems. Approximately 40%–50% of high performance processor power is consumed in the CDN [1]. The CDN and latches dissipate around 60% of the IBM POWER 1.4 GHz microprocessor’s power [2]. Latest developments in integrated circuit design specifically in 3-D integration where multi plane synchronization is required, looking forward to believe that the power consumption of the CDN will remain at these high levels [3].Resonant clocking enables the generation of clock signals with reduced power consumption. The traditional approach for LC resonant CDNs is to use the LC tank to drive the global clock distribution while the local square clock is being delivered through conventional buffers. Therefore, around 66% of clock power is being dissipated in the last buffer stage driving the flip-flops [4], leading to minor power savings in LC globally-resonant locally-square CDNs. In order to achieve maximum power savings, the LC tank should drive the entire clock network (both global and local) without using intermediate buffers. This would require designing, modifying and understanding flip-flop performance with the sinusoidal clock signal generated in LC resonant networks [5] demonstrated that a low-swing square-wave ISSN: 2231-5381 The Conditional capturing flip-flop is shown in the Fig.1 is used to minimize power at low data switching activities by eliminating redundant internal transitions [8]. As shown in Fig.1, reduced swing inverters similar to the one presented in [7] are used at the node fed by the low-swing sinusoidal clock signal. This is done to reduce short circuit power. The load pMOS transistor in the reduced swing inverters is always in saturation since VGS=VDS. It lowers the voltage at the source of the second pMOS in each inverter to approximately VDD -|VTP| thus turning it off when the lowswing sinusoidal clock signal reaches its peak voltage. The peak voltage for the low-swing clock was chosen to be equal to 0.65 V since VDD= 1 V and the threshold voltage of the pMOS transistor is approximately -0.34 V. From here on and for simplicity the term LS and FS refer to low swing and fullswing, respectively.Due to the time difference between the low- and full-swing sinusoidal clock signals to reach V PULLDOWN, the low-swing flip-flop experiences longer data to output delay(TDQ) as compared to the full-swing flip-flop for the same setup time (TDCLK). Let the full swing and low swing clock signal be given by the equations: V(t)full_ swing=1/2 vdd sin(2πft-π/2)+1/2vdd (1) V(t)low_ swing=0.65/2 vdd sin(2πft-π/2)+0.65/2vdd (2) where f is the clock frequency, VDD and 0.65 VDD are the peak voltage for the full and low-swing sinusoidal clock signals, respectively. http://www.ijettjournal.org Page 1 International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 1 - May 2014 Fig.1 LS_DCCFF The power dissipation of the resonant clock network is given by the following equation: Presonant_clock=Rclk/2(πfVpeak(Cclk+αNCFF))2 (3) Where Rclk and Cclk are the clock capacitance and resistance as seen by the driver, f and Vpeak are the frequency and peak voltage of the generated clock signal, C FF is the loading capacitance of the flip-flop, is the number of flipflops, and α is the factor by which the loading capacitance of the flip-flop connected at the clock leaves is reflected to the driver side. Equation (7) illustrates that generating a lowswing clock signal with Vpeak=0.65VDD results in around 55% power reduction in the clock network. Fig. 2 Low/Full-swing flip-flop IV. SIMULATION RESULTS A. Low swing flip-flop The Fig.3 shows the output wave form of existing system with tanner tool by using TSMC 180nm technology. The overall work was done with Tanner 13.0 and layout can be developed by using Microwind tools. III. PROPOSED SYSTEM To analysis the correct operation of the proposed LF-DCCFF and to highlight potential power savings enabled through low/full-swing clocking clocking , a test chip with a MAC unit designed using the proposed flip-flop under low/full-swing sinusoidal clocking was fabricated in TSMC 180-nm CMOS technology. Since the 16*16-bit multiplier itself was not pipelined, a clock frequency of 100 MHz was chosen for the test chip. Due to the large inductor needed for clock generation and the limited area available, the clock generator was not implemented on-chip. The sinusoidal clock signal is fed by an external source through an analog pad. Furthermore, the DCCFF was modified to enable dual-mode operation of the MAC unit under full- and low-swing clocking without significant area overhead. As illustrated in Fig.2, the LF-DCCFF presented in Fig. 1 was modified at node X to allow the operation under full- and low-swing clocking, it acts as an output path while executing. When signal FULL_SWING is high, full-swing clocking is enabled and the inverted clock output of the normal inverters CLKD_FS is feeding transistor MN1. Whereas low-swing clocking is enabled when signal FULL_SWING is low and the output of the reduced voltage swing inverters CLKD_LS feeds transistor. Two separate instances of the full- and low-swing DCCFF were implemented at the lower portion of the chip for testing. The overall area of the low/full-swing is taken from microwind tool with TSMC 70nm technology. Finally the area of the swing is reduced. ISSN: 2231-5381 Fig. 3 Output Waveform of existing method B. Low swing flip-flop, When D=1 The Fig.4 shows the output waveform shows the output wave form of proposed system with tanner tool by using TSMC 180nm technology. The overall work was done with Tanner 13.0 and layout can be developed by using Microwind tools. If fs value is given by 1, it is working as a full swing clocking and if fs=0, it working as a low swing clocking. http://www.ijettjournal.org Page 2 International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 1 - May 2014 TABLE II POWER ANALYSIS OF LOW/FULL SWING DESIGN POWER FULL SWING 4.778121e LOW SWING 3.440391e FULL/LOW SWING 5.111633e The Table.2 shows the power analysis of the existing and proposed circuit for low, full and full/low swing circuits, while using the 180NM the power consumption are different in the tanner tool. Fig. 4 Output Waveform C. Low swing flip-flop, When D=0 The Fig.5 shows the output waveform shows the output wave form of proposed system with tanner tool by using TSMC 180nm technology. The overall work was done with Tanner 13.0 and layout can be developed by using Microwind tools. If fs value is given by 1, it is working as a full swing clocking and if fs=0, it working as a low swing clocking. E. Comparison of charts Fig. 7 Power analysis Fig. 5 Output Waveform D. Layout design of modified low/full swing Fig. 8 Area analysis Fig. 6 Layout Design of proposed circuit The Figure shows the layout design of proposed work (low/full swing circuit) by using TSMC 70nm technology. The Chart comparison of the circuit with proposed and existing systems of the low, full and low/full swing are charted here for representation of clear view. V. CONCLUSION TABLE I ANALYSIS PARAMETERS OF LOW/FULL SWING DESIGN MODULES FULL SWING LOW SWING FULL/LOW SWING 90 NM 126.7µm2 709.3µm2 422.0µm2 70 NM 182.3µm2 258.9µm2 280.08µm2 The Table.1 shows the area analysis of the existing and proposed circuit for low, full and full/low swing circuits, while using the different NM the range of the size and power are different in the microwind tool. ISSN: 2231-5381 Thus we have used the newly designed Power optimized conditional capturing flip-flop for the reduction of overall power used and the area consumed. The flip-flop used for the low swing mechanism which reduces the overall power consumption of the IC and thereby reducing the component requirements. By using the power efficiency calculations more effectively we can reduce the power and the size of the IC further in the future. REFERENCES [1] Asgari.F.H.A and Sachdev.M(2012), “A low-power reduced swing global clocking methodology,” IEEE Trans. Very Large Scale Integr.(VLSI)Syst., vol. 12, no. 5, pp. 538-545. http://www.ijettjournal.org Page 3 International Journal of Engineering Trends and Technology (IJETT) – Volume 11 Number 1 - May 2014 [2] [3] [4] [5] [6] [7] [8] [9] [10] Drake.A.J, Nowka.K.J, Nguyen.T.Y, Burns.L.J, and Brown.R.B(2004), “Resonant clocking using distributed parasitic capacitance,” IEE J.Solid-State Circuits, vol. 39, no. 9, pp. 1520-1528. Esmaeili.S.E, Al-Khalili.A.J, and Cowan.G.E.R,(2010)“Dual-edge triggered sense amplifier flip-flop for resonant clock distribution networks,” IET Compute. Digit. Tech., vol. 4, no. 6, pp. 499-514. Esmaeili.S.E., Al-Khalili.A.J, and Cowan.G.E.R, (2010) “Estimating required driver strength in the resonant clock generator,” in Proc. IEEE Asia Pacific Conf. Circuits Syst., pp. 927-930. Kim.C and Kang.S.M (2001), “A low-swing clock doubleedge Triggered flip-flop,” in Proc. Symp. VLSI Circuits, pp. 183-186. Mahmoodi, Tirumalashetty.V, Cooke.M, and Roy.K (2009), “Ultra low-power clocking scheme using energy recovery and clock gating,”IEEE Trans. Very Large Scale Integer. (VLSI) Syst., vol. 17, no. 1, pp.33-44. Naffziger.S.D and Hammond,(2002) “The implementation of the next generation 64 b Itanium™ microprocessor,” in Dig. Tech. Papers,IEEE Int. Solid-State Circuits Conf.pp. 344-472. Pangjun.J and Sapatnekar.S.S (2010), “Low- power clock Distribution using multiple voltages and reduced swings,” IEEE Trans.Very Large ScaleIntegr. (VLSI) Syst., vol. 10, no. 3, pp. 309- 318. Pavlidis.V.F, Savidis.I, and Friedman.E.G, (2010) “Clock distribution networks in 3-D integrated systems. Xu.Z and Shepard.K.L,(2009) “Design and analysis of activelydesk wed resonant clock network,” IEEE J. SolidState Circuits, vol.44, no. 2,pp. 558-568 ISSN: 2231-5381 http://www.ijettjournal.org Page 4