An Approach for Optimized Timing of Error Correcting Unordered Codes

advertisement

International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue8- August 2013

An Approach for Optimized Timing of Error Correcting Unordered Codes

Nida Yasmeen1, Sudhir Dakey2

1

Post Graduate Student, Department of Electronics and Communication,MVSR Engineering College,Hyderabad,India-500510

2

Associate Professor, Department of Electronics and Communication,MVSR EngineeringCollege,Hyderabad,India-500510

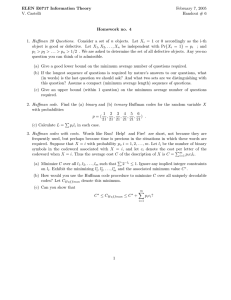

Abstract - This Paper proposes an approach for

reducing latency in asynchronous communication.

This paper uses a new family of error correcting

unordered codes for global communication called

Zero Sum. The important feature of the zero sum

is that they are systematic, allowing direct

extraction of data, and weighted, where the check

field is computed as the sum of data index weights.

The zero sum, family of error correcting codes

consists of basic zero sum ecu code, zero-sum+ and

zero-sum* which detects multiple errors. Each

transmission includes a time-out mechanism. That

is, there is a notion of time window of

transmission, which can be made arbitrarily long,

but must be defined by the user. The proposed

approach to reduce simulation time which is taken

by time-out mechanism and proposed architecture

has been evaluated and proved to have better or

comparable timing efficiency, about 93%. zero

sum codes were simulated using modelsim tool

version 10.2b.

Keywords- asynchronous, delay insensitivity, error

correction, fault tolerance, systematic, timing

robustness

I.

INTRODUCTION

Continuous

technology

scaling

enables

implementation of complex application on a single

chip. This remarkable development is the result of

technology scaling that led to fabrication of Integrated

Circuit (IC) with smaller feature sizes, higher levels

of integration and faster operating frequencies. The

process of device scaling evolved from few

micrometers to nanometres today, and the circuit

complexity has advanced from Small-Scale

Integration (SSI) in 1960s to Giga-Scale Integration

(GSI) in 2000s. The performance of transistors is

continually improved through scaling. However, the

impact of technology scaling on long wires is reverse.

Hence, coordination and communication between

these components become challenging. Globally

Asynchronous Locally Synchronous (GALS) scheme

has been proposed as a solution. [5], to provide

flexibility in system integration. Some recent

ISSN: 2231-5381

applications of asynchronous global communication,

using delay-insensitive (DI) codes [5]. The

contributions of this paper are centered around a

family of error-correcting unordered (ECU) codes for

use in asynchronous global communication, called

Zero-Sum [1], [2],[3]These codes support two types

of robustness: timing-robustness, fault tolerance. By

the use of DI codes we can achieve timing robustness

and fault tolerance provides error correction and

detection.

All introduced Zero-Sum codes are systematic

[2],where data appears in unaltered form in each

codeword and can be directly extracted by the

receiver without any decoding hardware. They are

also weighted, where the check field is computed as

the sum of data index weights.

The basic method for generating the ZeroSum code builds on a prior approach briefly

introduced by Berger [8] and Bose [7]. In addition,

neither practical hardware support was provided nor

experimental evaluation was performed.

The key contributions of this paper are as

follows.

1) Defining the complete family of Zero-Sum codes,

by exploring the feasible space of index weight

assignments and permutations.

2) A new code, called Zero-Sum+, which guarantees

detection of up to 3-bit errors, or alternatively can

simultaneously support 1-bit correction and 2-bit

detection. These codes can also detect all odd

numbers of errors.

3) Zero-Sum* code,

which extends Zero-Sum+

through a

variety of weight assignment

strategies, to heuristically provide a high coverage for

2- bit correction.

4) An outline of the overall micro architecture and

system level asynchronous communication protocol.

5) A comparative evaluation of the proposed ZeroSum code approach

II. Background

Background and related work on asynchronous

communication and error correction are now briefly

reviewed. A brief review of the Zero-Sum code is also

presented.

http://www.ijettjournal.org

Page 3277

International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue8- August 2013

A. Point-to-Point Asynchronous Communication

The family of zero-sum codes assume

point-to-point communication [5] between a sender

and a receiver.

1) Asynchronous Communication Channels

Unlike synchronous design style which uses

a globally distributed clock signal to indicate

moments of stability of the data, asynchronous

circuits exchange information using handshakes to

explicitly indicate the validity and acceptance of data.

Abstractly, the sender provides a

request output signal (REQ) to the receiver. The

receiver in turn provides an acknowledgment input

signal (ACK) to the sender. If the sender passes actual

data to the receiver the REQ is typically replaced by

the encoded data, as shown in the Fig 1. A codeword

is placed by the sender on the data channel (where

each wire corresponds to a bit of the codeword), and

passed to the receiver. The ACK indicates that data

has been received by the receiver and new data can

eventually be sent.

Receiver

Sender

ACK

Fig. 1 Point-to-point asynchronous communication

ACK+. At this point, the reset operation begins. The

sender de-asserts the REQ− and in turn, the receiver

de-asserts its ACK− which is the final event of the

reset stage and the four-phase transaction. If data is

used, the data channel replaces the REQ wire. The

channel is initially all-0 (spacer state); data is

transmitted by asserting high the individual 1 bit of

the codeword (equivalent to REQ+); data is reset after

receiving ACK− by de-asserting low the individual 1

bit (equivalent to REQ−).

TABLE I

Four phase communication

EVEN

Data

0

1

0

Phase/parity

0

1

0

Logic

0

1

Null

3) Two-Phase Communication Protocol

Two phase handshaking

protocol where the information is carried by the

transition. Both rising and falling transitions are

equivalent, each being interpreted as the two-phase

protocol passes data using a request signal transition,

and acknowledges data reception with an

acknowledge

signal

transition.

Two-phase

handshaking is preferred for long on-chip

communication since it reduces the required number

of transitions by half and avoids the requirement of

spacer compared to four-phase signalling This saves

communication time and energy of the system

significantly.Therefore a four phase asynchronous

communication protocol is assumed in this paper.

2) Four-Phase Communication Protocol

Evaluate

operation

Reset

operation

REQ

ACK

Fig. 2 Four Phase protocol

Given an asynchronous communication

channel, a protocol is needed to transfer information

from sender to receiver. The most widely used

protocol is four-phase or return-to-zero (RZ) [5]. As

illustrated in Fig. 2.The protocol has two operations:

a) evaluate, and b) reset. During the evaluate

operation, the sender first indicates the start of an

event by issuing a rising REQ+ to the receiver. Once

this signal has been received, the receiver asserts an

ISSN: 2231-5381

3) DI Codes

The

delay-insensitivity

makes

the

communication robust and attains average-case

performance rather than worst case which is the

situation in communication based on timing

constraints. The delay-insensitivity makes the data

transfer robust, because the sender and the receiver

modules can communicate reliably regardless of

delays in the transceivers and wires. Delay-insensitive

data encoding technique requires 2N wires to transmit

N-bit data. When asynchronous communication is

used, data must be suitably encoded so that the

receiver can identify when a packet has been received.

DI codes [4], (i.e., unordered codes [6]) are

insensitive to propagation delays on individual bits in

a codeword. The key property is that no valid

codeword is covered by another.

Assuming a four-phase protocol, where the

channel is reset to all-0 (i.e., spacer) between

successive

transmissions,

the receiver

can

unambiguously identify the arrival of a valid

codeword. In particular, as the individual 1 bit of a

codeword arrive (i.e., rising wire transitions), no other

http://www.ijettjournal.org

Page 3278

International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue8- August 2013

Table III

codeword will be seen transiently during the

transmission, since the 1-bit pattern of each valid

codeword is never covered (i.e., not a subset) by any

other. As the bits arrive, several codeword may be

candidates for the transmitted one, but a unique valid

codeword will only be seen when precisely all bits

have arrived. As a result, in an asynchronous system,

these codes have an inherent timing-robustness, where

individual bits of a codeword can arrive in any order

and at any time during transmission, and the final

valid codeword can be uniquely identified.

2-bit zero-sum code

Dataword

indices

weights

i 5 I4

53

00

Check

bits

i3 i 2 i 1 i 0

8421

1000

01

0101

10

0011

11

0000

Table IV

4-bit zero sum code

Indices

Weights

Fig. 3 Delay Insensitive

For example consider Fig. 3, the data to be trans

mitted is 1011 and four phase protocol requires 2N

lines for N data bits .according to table I, the data

forms as in Fig. 3.First null bits transmitted, then data

bits. After every data bits null bit is transmitted. The

data bit is valid if and only if there is a null bit after

databit.

III. RELATED WORK

A .Basic Zero-Sum Code:

This section reviews the basic Zero-Sum code. This

code uses the single index weight assignment only

briefly discussed in Berger [7] and Bose [10]..Code

construction combines aspects of both Hamming

codes and Berger [7] codes. In particular, as in Berger

codes, the pattern of 0 bit in the dataword is used to

generate the DI field. However, while the Berger

method counts the number of 0s, the Zero-Sum

approach adds the 0-bit index weights. Similarly,

Zero-Sum adopts the bit index numbering scheme

used in Hamming codes, but typically requires extra

bits.

TABLE II

3-bit Zero-sum code

indices

weights

Dataword

I6 i 5 I4

65 3

000

Check bits

i3 i 2 i 1 i 0

8421

1110

001

1011

010

1001

100

1000

011

0110

101

0101

110

0011

111

0000

ISSN: 2231-5381

Dataword

Check Bits

i8 i 7 i 6 i 5

7 6 5 3

0000

I4 i3 i 2 I1 i 0

16 8 4 2 1

10101

0001

10010

0010

10000

0100

01111

1000

01110

0011

01101

0101

01100

1001

01011

0110

01010

1010

01001

1100

01000

0111

00111

1011

00110

1101

00101

1110

00011

1111

00000

B. Code Overview

The code has two fields: dataword, and

check. Each bit position is assigned an index. The

check bits index weights are powers-of-two (for

nonnegative exponents), and the dataword index

weights are the remaining positive integers [1]. Fig 2

shows examples of zero sun ECU codes for 2 bit, 3bit,4-bit data fields

1) Check Field Generation

The Zero-Sum code uses a unified check

field, based on single operation: it is binary

representation of the arithmetic sum of the dataword

http://www.ijettjournal.org

Page 3279

International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue8- August 2013

index weights whose bit is 0, hence the name of the

codes, Zero-Sum Code length calculation, the check

field must be Large enough to cover binary

representation of all data fields.

Therefore, the total number of check bits allocated is

the log2 (_dataword index weights) + 1.the equation

becomes with check field length k in terms of data

field length n

k = log2 ([(n + µ)(n + µ + 1)/2] − 2µ + 1)

Where µ is given by

2µ−1 < n+µ < 2µ

,

B. Zero sum + codes

The codeword structure is the same as the original

Zero-Sum Code, but the difference is in data field

indices. . It provides two alternative modes. In one

mode, up to 3-bit errors and all odd errors can be

detected. In a second mode, both correction and

detection can be handled together: every 2-bit error

can be detected and every 1-bit error can be corrected

1) Overview

Start

Input the Data (n

bits)

Yes

Data [n]

=0

No

No

Example 1: suppose there is an error in transmitting

the 4-bit dataword 1010, due to a flip in the data bit

with index 7 (i.e., erroneous dataword 0010),

transmitted with the original error-free check field

(i.e., 01001). The newly calculated check field, based

on the corrupted dataword, is 16 (i.e., 7 + 6 + 3).

Therefore, the syndrome is 16 − 9 = 7, which is

nonzero and not a power of- two. This syndrome

therefore precisely identifies the index (i.e., 7) of the

corrupted data bit. In contrast, if a single check bit has

an error, the syndrome will be a power-of-two and

identify the corresponding index of the corrupted

check bit.

Add the

weight

indices of

data word

It is essentially a Zero-Sum code with parity

bit attached. The new field is the parity bit, which

provides even parity. Its index weight is 0.

2) Error Detection

Error detection mode can detect up to 3-bit

errors and all odd numbers of bit errors. In the case of

0 errors in the received codeword is where the parity

is correctly set to even and the syndrome is equal to 0.

If a 1-bit error occurs in either the dataword or the

check fields, the syndrome will be nonzero. When a

2-bit error occurs, the parity of the received codeword

will be correctly set to even; however, the syndrome

is guaranteed to be nonzero.

Is data

word

length=0

Yes

Print the data,

check bits

Stop

Table V

4-bit Zero-sum+

Fig. 4 zero sum code encoding

indices

Weight

2) Detecting and Correcting a 1-Bit Error

The Zero-Sum ECU code provides a

unified syndrome which is a single positive integer:

the absolute value of the difference between the

appended check field and a newly calculated check

field. In Zero-Sum, the receiver creates a regenerated

check field C ‘ from its data field, and compares C’

to the actual received check field C. The resulting

Zero-Sum syndrome, is the absolute difference of |C’

− C|. If the difference is zero, there is no error. The

syndrome is also used to correct a 1-bit error: its value

is theindex of the corrupted bit.

ISSN: 2231-5381

Dataword

Check bits

Parity

I9 i 8 i 7 i 6

7 6 5 3

0000

0001

0010

0100

1000

0011

0101

1001

0110

1010

1100

0111

1011

1101

1110

1111

I5 i 4 i 3 I2 i 1

16 8 4 2 1

10101

10010

10000

01111

01110

01101

01100

01011

01010

01001

01000

00111

00110

00101

00011

00000

I0

0

1

1

0

1

0

1

0

1

0

0

1

0

1

1

1

0

http://www.ijettjournal.org

Page 3280

International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue8- August 2013

TABLE VI

Zero-Sum+ Error Detection Classification

# of errors

0

1

2

3(or odd)

Parity

Even

Odd

Even

Odd

Syndrome value

Zero

Zero or nonzero

Nonzero

Zero or nonzero

Approach 1: Basic Unoptimized Method:

1. Generate all possible original code words.

2. Find the syndromes

3.Prune code words based on the syndrome.

Table VIII

4-bit Zero-sum * code

3) Error Correction:

Indices

weights

Table VI gives correction methods for a zero

sum + .When 0 errors occur, the parity is even and

syndrome values are correct.

TABLE VII

Zero-Sum+ Error Correction Classification

No. of

errors

0

1

Parity

Even

Odd

Syndrome

value

Zero

Nonzero

2

Odd

Zero

Error

handling

None

1-bit

correction

Toggle parity

Therefore, no error handling method is applied. When

1 error occurs, there are two cases. If the error occurs

in either the dataword or the check fields, the

syndrome value is nonzero and the parity is

incorrectly set to odd. The error correction is handled

in same way as presented in section III.

C. Zero-Sum* Code:

The codes support heuristic multi-bit

correction by varying the index weight assignment

Check bits

Parity

I9 I 8 I 7 I 6

3 7 11 5

0000

I5 I4 I 3 I2 I 1

16 8 4 2 1

10101

I0

0

1

0001

10010

0

0010

10000

1

0100

01111

0

1000

01110

1

0011

01101

0

0101

01100

0

1001

01011

0

0110

01010

1

1010

01001

0

1100

01000

1

0111

00111

1

1011

00110

0

1101

00101

0

1110

00011

1

1111

00000

0

TABLE IX

Zero-Sum* Error Correction Classification

1) Overview

The dataword and check fields are assigned

distinct integer weights. The dataword field is

assigned non-power-of-two values {3, 7, 11, 5}, as

shown in Table VIII

2)2-Bit Correction

The Zero-Sum* code can correct all 1-bit

errors and some times of 2-bit errors. Table III

summarizes how each error type is classified and

corrected.

A 1-bit error is corrected by either toggling

the parity bit or using the 1-bit correction method.

Two alternative approaches are proposed to correct 2bit errors. The unoptimized approach performs 2-bit

correction by generating the syndromes of all possible

candidate code words. In the optimized approach,

complete syndromes are not explicitly generated,

instead, a precalculated lookup table is used, and a

targeted evaluation of index pairs which produced the

syndrome is performed.

ISSN: 2231-5381

Dataword

Each candidate codeword that has nonzero syndromes

No.of

errors

0

1

Parity

Syndrome value

Error handling

Even

Odd

Zero

nonzero

1

2

Odd

Even

Zero

nonzero

None

1-bit

correction

method

Toggle parity bit

2-bit

correction

method

is discarded. Such a candidate codeword with a

nonzero syndrome could not have been the original

codeword. If there exists exactly one valid candidate

codeword, then correction can be performed.

Intuitively, one remaining codeword means that there

was precisely one way to reach the received codeword

from a valid codeword in 2-bit flips. This single

remaining codeword is the original sent codeword.

When multiple code words remain, there is ambiguity

in how the received codeword has reached, since any

one could have been the originally sent codeword.

http://www.ijettjournal.org

Page 3281

International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue8- August 2013

Step 2

Step 2

Dataword

I9 I 8 I7 I6

indices

Dataword

Check bits

Parity

Candidate

Indices

I9 I 8 I 7 I 6

I5 I4 I 3 I2 I 1

I0

Flipped

Codeword

weights

3 7 11 5

16 8 4 2 1

0

indices

syndrome

1 11 1

11111

1

(I9 I 8)

31-0=31

1001

1 11 1 1

1

(I9,I 7)

31-18-13

1010

11111

1

(I9 I 6)

31-12=19

1011

01111

1

(I9 I5 )

15-7=8

weights

sent

codeword

rxd

corrupted

codeword

Parity

I0

3 7 11 5

0010

Check bits

I5 I 4 I 3 I 3

i2i1

16 8 4 2 1

1110

0011

1011

1

0

1

ERROR

Syndrome 31-10=21

Fig. 6 Received codeword with 2-bit errors step 1

0111

0010

--

---

--

---

11011

1

(I8, I3)

27-3=24

--

---

--

---

01111

1

(I6 I5)

15-15=0

[syndrome

zero]

1

(I3, I1)

25-10=15

-0011

11001

{I9,I8 } ------> -3-7=-10

{I9,I6} ---- 3+5=2

{I9,I5} ----- -3+16=13

{ I9,I8} ----- -7+4=-3

----------------{ I9,I8} ---- 5+16=21

{I9,I8 } ---- 4+2=6

{I9,I8} ------ 2+1=3

Value matches

syndrome

Fig. 5 Optimized approach for example: step 2

--

---

Approach 2: Optimized Method:

Generate the syndrome of the received codeword.

Find value for each pair of indices prune pairs based

on the value: An index pair whose value does not

match that of the received codeword’s syndrome is

discarded. This pair could not have been the pair of

indices that flipped to form the syndrome. A 2-bit

error can be corrected when exactly one such pair

exists. Intuitively, this pair precisely represents the

two weights which flipped to create the syndrome.

Otherwise, if multiple pairs exist, then there is

ambiguity about which pair flipped to create the

syndrome.

Example: As shown in Fig.2, when transmitting valid

codeword 0010 01111 1, suppose the receiver

receives codeword 0011 11111 1, where a 2-bit error

occurred

ISSN: 2231-5381

Fig 3: Step 2: find values for each pair of indices

in index pair {i6, i5}. For both bits, the value is

toggled from 0 to 1. Fig. 3 shows the corresponding

steps of the optimized approach. In Step 1, the

syndrome of the received codeword is generated. This

syndrome has a value of 21 (i.e., 31-10). Next, for

each indices pair, the associated value is found. For

example, index pair {i9, i8} has a value of −10 (or −3

− 7) since both bits make a 0 to 1 transition from the

received codeword. For this particular example, there

are 45 (i.e., 10 choose 2) pairs of indices, thus only a

limited set has been illustrated. In Step 3, the pairs are

pruned according to their values, where only pairs

whose values equal the syndrome are kept. The pair

whose value matches the syndrome highlighted in Fig.

10. Since only one pair exists in the example,

correction can be performed. Therefore, flipping

index pair {i6, i5} from the received codeword will

correctly restore the original sent codeword of 0010

01111 1.

IV. TIME-OUT MECHANISM

A time-out signal is asserted if a valid

codeword is not received within a reasonable amount

of time [1]. The time-out counter is activated once the

first 1 bit is received on the input channel, and runs

http://www.ijettjournal.org

Page 3282

International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue8- August 2013

during the receipt of additional bits of the codeword

[2].

V. RESEARCH WORK

The timeout mechanism the above method as

shown in simulation results takes a simulation of 6160

ns. To increase the speed of the hardware the counter

in the hardware has been removed and the completion

detector has designed to take the valid or invalid

codes at the input not like the one discussed in [1]

,which takes only valid code words and it makes ACK

to ‘1’ to the transmitter and gets corrected it at the

receiver. This takes a time of 400ns of time for

simulation as shown in fig

VI. RESULTS

VIII. CONCLUSION

The above approach focuses on errorhandling in the evaluate phase. Zero-Sum errorcorrecting unordered codes support the design of

asynchronous global communication which combines

two forms of reliability: timing robustness and fault

tolerance. The design without timeout mechanism has

given a pretty good efficient design which has given

93% time efficient design. However there is an area

overhead due to proposed approach.

ACKNOWLEDGMENT

I owe my sincere gratitude to my guide

Mr.Sudhir Dakey (Associate Professor) for guiding

me on regular basis. I thank for his immense support

and his sagacious guidance throughout the project.

REFERENCES

[1] M. Y. Agyekum and S. M. Nowick, “An error-

Fig. 4 simulation time with a time out mechanism

Fig. 5 simulation time without time out mechanism

VII. COMPARISION

TABLE X

Device utilization summary of completion detector with a timer

Number of Slices:

Number of 4 input LUTs:

Number of IOs:

Number of bonded IOBs:

8

15

10

10

out of 960

out of 1920

out of

66

1%

1%

15%

TABLE X

Device utilization summary of completion detector without a timer

Number of Slices:

8 out of 960

1%

Number of 4 input LUTs:

15 out of 1920

1%

Number of IOs:

19

Number of bonded IOBs:

19 out of 66

28%

ISSN: 2231-5381

correcting unordered code and hardware support for robust

asynchronous global communication,” IEEE trans compt.,

vol. 31, no. 1, Jan 2012

[2] M. Y. Agyekum, “Designing delay-insensitive codes for

robust global asynchronous

communication,” Ph.D. dissertation, Columbia University,

New York,Jan. 2011

[3] M. Y. Agyekum and S. M. Nowick, “An delayinsensitive bus-invert code and hardware support for robust

asynchronous global communication,” in Proc. DATE, Mar.

2011, pp. 1–6.

[4] J. M. Berger, “A note on error detecting codes for

asymmetric channels,” Inform Contr., vol. 4, no. 1, pp. 68–

73, 1961.

[5] T. Verhoeff, “Delay-insensitive codes: An overview,”

Distrib. Comput., vol. 3, no.1, pp. 1–8, 1988.

[6] B. Bose, “On unordered codes,” IEEE Trans. Comput.,

vol. 40, no. 2, pp. 125–131, Feb. 1991

[7] B. Bose, “Unidirectional error correction/detection for

VLSI memory,” in Proc.

ISCA, 1984, pp. 242–244.

[8] J. M. Berger, “A note on error detecting codes for

asymmetric channels,” Inform. Contr., vol. 4, no. 1, pp. 68–

73,

1961.

http://www.ijettjournal.org

Page 3283