FPGA based Conducted Noise Mitigation in technique

advertisement

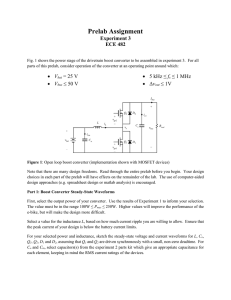

International Journal of Engineering Trends and Technology (IJETT) - Volume4Issue4- April 2013 FPGA based Conducted Noise Mitigation in Fly-back Converter using Adaptive and Random technique Syamala P.J#1, R.Vimala#2 #1 Department of EEE PSNA College of Engineering and Technology Dindigul, India. #2 Department of EEE PSNA College of Engineering and Technology Dindigul, India Abstract— Switching power converters (SPC) are always required to operate without affecting the performance of the adjacent circuits. This paper proposes two methods for conducted noise reduction in fly back converter. Adaptive Digital Pulse Width Modulation (DPWM) and Randomized Pulse Width Modulation (RPWM) are the two techniques. Spread spectrum technique is used to reduce the Electromagnetic interference (EMI) produced in the converter by spreading the noise over a large bandwidth in RPWM. Adaptive DPWM uses the noise shaping characteristics of a sigma-delta modulator to reduce the noise produced by the converter. The two schemes is implemented using Field Programmable Gate Array (FPGA) controller. The effect of using the propose controller on common mode, differential mode and total conducted mode noise characteristics of flyback converter is analysed. Keywords—EMC, FPGA, Randomized switching control, flyback Converter, EM, spread spectrum, Digital pulse width modulation. I. INTRODUCTION In day today life there is a wide range of applications where SPC is used. SPC’s are ranging from a mill watt in on-chip power management to hundreds of megawatts in power systems. The advantage of switching at higher frequencies led the AC- DC and DC- DC SPC’s to be used in many systems. The size of the components and the weight of the transformer can be reduced by allowing the system to operate at high frequency and this in turn increase the efficiency compared to linear power supplies [1], [2]. It always requires an efficient and cost-effective static and dynamic power control over a wide range of operating conditions for most of applications. The SPC’s uses an analog or digital controller within the feedback loop, which effectively controls the on/off states of the power semiconductor switch to realize input or output regulation. When the SPC’s operate at high frequencies, noise will be generated due to large change in voltage and current during turning ON and turning OFF of the switches. The international standards like CISPR, FCC has imposed limits on the amount ISSN: 2231-5381 of EMI noise that a converter can add into the utility supply [3]. EMI noise is of two types, conducted and radiated.EMI generated by SPC’s will depend upon on many factors such as converter topology, control technique, circuit design, components used and circuit parasitic[4]-[9]. Some of the techniques used to reduce the noise are flow pass filtering, active filtering and soft switching. But these techniques require bulky circuit design and as a result the cost also increases. This makes it unsuitable for compact and price limited application [10]. Fly-back converter is the most commonly used and simple SPC circuit for low output power high frequency applications where the output voltage need to be separated from the input main supply. In order to bring the EMI level in the SPC’s operating at high frequencies within the desired level imposed by the standards digital control is used [11]. The main advantages of the digital techniques are reduction in the number of passive components, programmability of control and system parameters, system integration, calibration and diagnostics capabilities[12],[13]. This paper proposes two methods to reduce the EMI. The former is RPWM, where spread spectrum scheme is used to spread the noise over a large bandwidth to a smoother continuous spectrum. This reduces the acoustic disturbance and EMI [14]. Thus the average spectral power density of the broadband noise can be considerably reduced. The latter is the DPWM technique where a sigma delta modulator noise shaping characteristic is used to minimize the clock spur produced by the PWM signal. Both of the schemes are implemented using Field Programmable Gate Array (FPGA) controller. Better performance and cost reduction of FPGA technology have made it suitable for power supply applications. The digital realization of the control circuits improves the efficiency without any change in the topology of the circuit [15]. Thus reduce the cost, size of the components compared to other methods of control. http://www.ijettjournal.org Page 901 International Journal of Engineering Trends and Technology (IJETT) - Volume4Issue4- April 2013 II. PROPOSED RANDOM SWITCHING CONTROL FOR FLYBACK CONVERTER USING FPGA Several controlling techniques are proposed in the literature to reduce the conducted EMI produced in fly-back converter. Randomized pulse width modulation technique is a best method to distribute the noise over a wide frequency range and thus enable to minimize the high frequency conducted noise [16]. The overall circuit block diagram of a fly-back converter using FPGA controller which is randomly switched is shown in the Fig.1. The major components are fly-back converter power switching circuit, an Analog to Digital Conversion (ADC) circuit and its driver, the proposed FPGA digital controller, interface power switches and its driver circuits. The fly-back converter is considered to be working in the Continuous Conduction Mode (CCM) with minimum output current. P P in o FLYBACK CONVERTER v o PSEUDORANDOM STREAM GENERATOR INTERFACE & POWER SWITCHES DRIVER ADC DRIVER ADC RN (n+1) VV DPWM gs1 gs2 DIGITAL COMPENSATOR 8-bit FPGA-BASED DIGITAL CONTROLLER Fig.1 Randomly switched fly back converter using FPGA The output voltage of the SPC’s is converted into a digital 8-bit signal by means of an Analog to Digital Converter (ADC). This signal from the ADC is processed by the digital compensator to compute the duty ratio (α). The ADC’s driver is designed and kept inside the FPGA-based digital controller. The conversion cycle is begins with the switching cycle and finished within the same switching cycle. A digital compensator is designed to manage the output voltage to make it same as that of the specific voltage reference for a range of input voltage values, load currents, and change of temperature [17]. The compensator does not allow the output voltage to vary during randomized variations in the switching frequency. At this present switching cycle, the digital compensator calculates the digital duty ratio α (n+1) for the subsequent switching cycle in one of three modes. In the step decrease mode, the duty ratio is reduced by a step change (∆α) when the output voltage is greater than the upper threshold voltage (Vref + αz) where Vref is the reference voltage and αz is the step change duty ratio. If the output voltage is less than the lower threshold voltage (Vref - αz) the duty ratio is increased by a step change (∆α).Dead zone mode will keep the duty ratio same as the present value, when the output voltage lies between the upper and lower threshold ISSN: 2231-5381 voltage limits. In this way, by employing a dead zone comparator undesired oscillations in the converter output is prevented. Thus, a stable operating condition is obtained for the converter using the digital compensator. A pseudorandom number generator (PRNG) is an algorithm for generating a series of numbers that has similar properties of random numbers. The series of numbers so generated is not truly random. The series that are nearer to truly random can be also produced using hardware random number generators. The required number of maximum length Linear Feedback Shift Registers (m-LFSR) with maximum period is arranged in parallel to attain the random sequence. The diverse mLFSRs output bits with dissimilar primary contents of the mLFSRs taps are EX-ORed consecutively with the output and then fed back into the leftmost bit of the linear feedback shift register. The flow of the data in all of the m-LFSRs is controlled by the same clock. The designed pseudorandom stream generator can deliver a 16-bit output; the maximal number it can generate is up to 216-1 = 65535. The output from the PSRN generator is provided to the Digital Pulse Width Modulator (DPWM). During beginning of each switching cycle, the random output bits are transformed into an integer number (SRN) and it is used in the DPWM. But, the remaining generated random output bits are discarded. At the beginning of each switching cycle, the DPWM consider the duty ratio of the next switching cycle α (n+1) as the duty ratio of the present switching cycle duty ratio. The compensator also receives the integer number by transforming the output of the PSRN generator. The switching frequency and duty ratio for the next switching cycle is calculated as: FSW = FL + A ×SRN (1) SF = fclk / fsw (2) α r = SF × α (n) (3) Whereas; FSW : Switching frequency FL : Lower frequency limit A: Constant for achieving the requisite randomized frequency range SRN: Pseudorandom output stream converted into an integer number SF: Needed number of steps to fulfil the switching frequency FCLK : Clock frequency αr: Needed number of steps to fulfil the duty-ratio dt: Dead Time The clocked counter in the designed DPWM increments up to the next switching cycle SF and then resets at the end of the switching cycle. When the counter value exceeds the reference value of the number of steps required for attaining the duty ratio (αr), the PWM output changes the state from high to low level. The DPWM waveforms (Vgs1; 2) with the commanded duty ratio at the calculated switching frequency are generated in this way. http://www.ijettjournal.org Page 902 International Journal of Engineering Trends and Technology (IJETT) - Volume4Issue4- April 2013 III. PROPOSED ADAPTIVE DIGITAL PULSE WIDTH MODULATION TECHNIQUE The SPC’s uses PWM technique as a controlling method to obtain the desired output which is more suitable while using a high speed controller to control the output. But switching noise will be produced a result of high speed switching and will also appears in the output voltage at multiple clock frequency [18]. The DPWM resolution is made higher to avoid the limit cycle oscillation and to improve the efficiency of the output voltage. The major constraint is that the DPWM resolution is proportional to the switching frequency and energy consumption which limits the application. The overall block diagram is shown in the fig.2 Schematic diagram of digital controller for fly-back converter. counter-comparator can adjust the incoming system clock frequency to adjust the alteration of ADC resolution [20]. 2 fs fs D[K+3:3] > 5-bit MASH e(k+7.0) PID Controller PWM D[3:0] Form controller d(k+8.0) Sc K-bit counter comparator 4-bit DCM multiplier phase-shift > Digital controller Adaptive Digital PWM 2k fs k vref e(t) A/D Converter D[K+7:0] comparator Fig.3 Proposed adaptive DPWM block diagram + - c(t) vout Fly-back Converter vin Fig. 2 Schematic diagram of digital controller for Fly-back converter The proposed method is uses a adaptive DPWM which includes 4-bit Digital Clock Manager (DCM), phase-shift characteristics available in FPGA with a selectable frequency and combines a k-bit counter-comparator block with 5-bit Multi-stAge-noise-SHaping (MASH) ∆-∑ modulator. The resolution of MASH and the DCM block is kept as fixed and capable of adapting to the resolution of the Analog to digital converter (ADC) frequency switching. The MASH sigma delta high resolution high frequency high resolution DPWM and also allows to operate at high switching frequency effciently.The value Signal Transfer Function (STF) and the Noise Tranfer Function (NTF) is taken as z~1 and ||NTF<<1|| respectively for effective noise reduction and to avoid quantization error at the input voltage.DCM module in the FPGA produce four version phase-shift clocks (clk_0, clk_π/2, clk_π and clk_3π/2) respectively, and also produce four times of the incoming clock concurrently. A segmented DCM module arranged in series is proposed in this paper a consistsDCM multiplie and phase shift and a multiplexer [19].The DCM module will receive the clock signal from MASH modultaor and adjust itself to the resolution of the ADC.Thus it will generate two dissimilar version of the phase shift frequencies signals.The ISSN: 2231-5381 IV. SIMULATION RESULTS Hardware Description Languages (HDLs) are used to describe the behaviour, structure of system and circuit designs. Xilinx ISE is a popular, most suitable development environment for designing Xilinx Complex Programmable Logic Devices (CPLD) and FPGAs. The coding for each component is developed and simulated to obtain the PWM signal to trigger the MOSFET. The PWM signal is obtained at various time intervals using RPWM scheme is obtained. Figure 4 shows the PWM signal in µS. Figure 6 shows the PWM signal in nS. Figure 7 shows the overall PWM signal obtained using RPWM. These PWM gate signals are used to trigger the switch of the fly back converter and the output waveform is analysed. Fig. 4 PWM signal in µS To generate the high resolution PWM signal in an adaptive DPWM technique, the system clock frequency must be increased to match with the switching frequency. But the increase in frequency may increase power consumption this http://www.ijettjournal.org Page 903 International Journal of Engineering Trends and Technology (IJETT) - Volume4Issue4- April 2013 cannot be changed in random. The ADC increases the resolution to make the adaptive DPW/m more efficient when the system is in stable condition. Similar to the RPWM technique the VHDL code are simulated to obtain different PMW signal for different ADC resolution. The Figure 8 shows the PWM signal generated by adaptive method for ADC resolution of 16 bit. fig 10 shows the conducted noise spectrum using RPWM technique. Fig.7 Adaptive DPWM adapted to 16-bit ADC simulation result Fig. 5 PWM signal in nS The noise so produced by the converter is reduced by the adaptive technique. But it is possible to reduce only up to the FCC limit. Randomly switching technique provides the highest conducted-noise peak reduction in the high and lowfrequency ranges. As shown in Fig. 10, it is seen that the conducted-noise spectrum and its components are significantly improved. The noise level is effectively reduced up to 50db. It is evident that by using the proposed FPGA controller with randomization values enable the converter to meet the FCC class B limits. Fig.6 Overall PWM signal obtained using RPWM tecnique V. EXPERIMENTAL SETUP AND INVESTIGATION The fly-back converter circuit is designed and the control techniques is implemented using Spartan 3A FPGA. The value of the inductor and the capacitor is chosen in such a way that the converter will operate in the continuous conduction mode. The conducted noise is sensed and standardized using a line impedance stabilizing network. The experimental setup is shown in the fig 8.The two control techniques is analysed one by one. In RWPM scheme, the SPC is triggered randomly using the FPGA controller. The output of the SPC is analysed using a spectrum analyser. The randomly switched converter noise spectrum is compared with the adaptive DPWM switched SPC. The noise spectrum of the converter with adaptive DPWM is shown in the fig 9. And the ISSN: 2231-5381 Fig.8 Experimental setup for noise analysis VI. CONCLUSION The control schemes implemented digitally using FPGA controller allows smooth, fast and ease of controlling the flyback converter. The RPWM technique by using the spread spectrum concept as the key criterion enables the spreading of the noise concentrated at a specific frequency range. The noise concentrated at low and high frequency range is brought down within the safer limits. Adaptive DPWM technique also controls the noise produced during the switching of power semiconductor switches. But the main constraint is that the power consumption will increase if the resolution and frequency is increased. It is evident that from the experimental investigations that the RPWM technique is more effective http://www.ijettjournal.org Page 904 International Journal of Engineering Trends and Technology (IJETT) - Volume4Issue4- April 2013 than the adaptive PWM technique. The overall cost of implementing two techniques very much less compared to the conventional analog method. [4] [5] [6] [7] [8] [9] [10] [11] Fig.9 Conducted noise spectrum using adaptive DPWM technique [12] [13] [14] [15] [16] [17] [18] Fig.10 Conducted noise spectrum using randomization technique. REFERENCES [1] [2] [3] M.H. Nagrial, A. Hellany, “Radiated and conducted EMI emissions in switch mode power supplies (SMPS): sources, causes and predictions”, IEEE Multi Topic Conference, pp. 54-61, 2001. J. Kaewchai, W. Khangern, S. Nitta, “Controlling conducted EMI emission on a buck-boost converter using gate controlled circuit”, International Symposium on Electromagnetic Compatibility, pp. 541544, 2002. K.Mainali, R. Oruganti, K. Viswanathan, and S. P. Ng (2008), “A metric for evaluating the EMI spectra of power converters,” IEEE Trans. Power Electron., vol. 23, no. 4, pp. 2075–2081. ISSN: 2231-5381 [19] [20] L.H. Mweene, “How to ease EMI compliance in power converters”, EE Times Design, pp. 1-2, 2006. Z.Y. He, F.Y. Shih, Y.T. Chen, Y.P. Wu, “Analysis and design of EMI filter for multi-output switching mode power supply”, International Telecommunications Energy Conference, pp. 457-463, 1994. J. Paramesh, A. Von Jouanne, “Use of sigma-delta modulation to control EMI from switch-mode power supplies”,IEEE Transactions on Industrial Electronics, Vol. 48, pp. 111-117, 2001. Y.C. Son, S.K. Sul, “Generalization of active filters for EMI reduction and harmonics compensation”, Industry Applications Conference, Vol. 2, pp. 1209-1214, 2003. R. Bera, J. Bera, A.K. Sen, P.R. Dasgupta, “Reduction of EMI from SMPS (switched mode power supplies) by resonance technique and its utilities in industrial process control instruments”, International Conference on Electromagnetic Interference and Compatibility, pp. 445-448, 1999. K. Yoshida, T. Ishii, N. Nagagata, “Zero voltage switching approach for fly back converter”, International Telecommunications Energy Conference, pp. 324-329, 1992. H. Hsieh, J. Li, and D. Chen (2008), “Effects of X capacitors on EMI filter effectiveness,” IEEE Trans. Ind. Electron., vol. 55, no. 2, pp. 949–955. S.Y. Oh, Y.-G. Jung, S.H. Yang, and Y.C. Lim (2009), “Harmonicspectrum spreading effects of two-phase random centered distribution PWM (DZRCD) scheme with dual zero vectors,” IEEE Trans. Ind. Electron.,vol. 56, no. 8, pp. 3013–3020. B. Miao, R. Zane, D. Maksimovic, “A modified cross-correlation method for system identification of power converters with digital control,” IEEE PESC 2004. pp 3728 - 3733. S. Kaboli, J. Mahdavi, and A. Agah, “Application of random PWM technique for reducing the conducted electromagnetic emissions in active filters,” IEEE Trans. Ind. Electron., vol. 54, no. 4, pp. 2333– 2343.2000. Y. Liu and P. C. Sen August, “Digital control of switching power converters”, Proceedings of the 2005 IEEE Conference on Control Applications, Toronto, Canada, Vol.2, pp.635–640, Aug.2005. D.Maksimovic, R. Zane, and R. Erickson, “Impact of digital control in power electronics”, IEEE Power Semiconductor Devices and ICs, Proceeding of the 16th International Symposium, pp.13–22, 2004. A.Peterchev and S.Sanders, IEEE Transactions on Power Electronics, pp.18,-301, (2003). B. J. Patella, A. Prodic, A. Zirger, and D. Maksimovic, IEEE Transactions on Power Electronics, pp.18- 438, 2003. V. Yousefzadeh, T. Takayama, and D. Maksimovic, “Hybrid DPWM with digital delay-locked loop”, 2006 IEEE Computers in Power Electronics Workshop, Rensselaer Polytechnic Institute, Troy, NY, USA, pp.142–148, July 2006. A. Syed, E. Ahmed, E. Alarcon, and D. Maksimovic, “Digital pulse width modulator architectures”, 35th Annual IEEE Power Electronics Specialist Conference, Aachen, Germany, pp.4689–4695, 2004. O. Trescases, G. Wei, and W. T. Ng, “A segmented digital pulse width modulator with self-calibration for low-power SMPS”, IEEE Conference on Electronic Devices and Solid-State Circuits, Hong Kong, China, pp http://www.ijettjournal.org Page 905