Recursive CORDIC- Based Low Power DCT Architecture

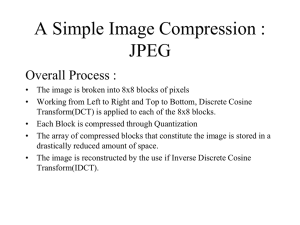

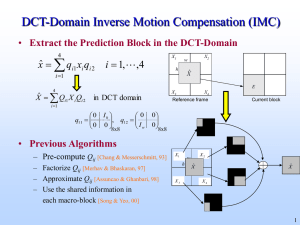

advertisement

International Journal of Engineering Trends and Technology (IJETT) – Volume 20 Number 6 – Feb 2015 Recursive CORDIC- Based Low Power DCT Architecture Mrs. M.NIDHIYA ARAVIND #1 , Ms.A.SHANMUKAPRIYA#2 #1 Assistant professor, #2P.G.Scholar, II M.E.VLSI Design Department of Electronics and Communication Engineering, #1,#2 Avinashilingam Institute for Home Science and Higher Education for Women-University Coimbatore, India #1,#2 Abstract- One of the maximum commonly used transform technique is Discrete Cosine Transform (DCT). In the DCT algorithm the inputs are in spatial domain and the outputs are in frequency domain and it is mostly used for image compression. DCT using Coordinate Rotation Digital Computer (CORDIC) algorithm lessen the number of calculation and increases the accuracy. Therefore discrete cosine transform design using CORDIC is used to obtain low power. All calculation in DCT are not equitably essential in producing the frequency domain output. Therefore the calculation energy can be lessen without severely incriminating the image quality. The 2-D DCT achieves more power saving. In a lookahead CORDIC approach, all interior data path become individualistic and the number of repetition can be easily controlled but the implementation complexity of lookahead CORDIC is considerably high because it requires more area. Therefore the recursive CORDIC is proposed in this project. This technique is easy to implement and considered as an appropriate technique. The power requirement for recursive CORDIC is less compared to lookahead CORDIC. The implementation is done using the Modelsim SE9.1i software. Keywords-Coordinate rotation digital computer (CORDIC), low power, discrete cosine transforms (DCT). I. INTRODUCTION The demand for low power implementation is tremendously increasing, with the explosive growth of multimedia services. The significant part of multimedia system involving image and video processing. DCT is one of the maximum calculation procedure in image compression and it is commonly used in many traditional such as JPEG [2], MPEG [3]. The trigonometric function in signal processing may be easily estimated by using Coordinate Rotation Digital Computer (CORDIC).For the multiplier less low-power DCT architectures, CORDIC has been widely used. CORDIC can be easily implemented with the iterative operations of additions and shifts. For reducing the hardware complexity of DCT Many previous research works were focused such as DCT based distribute arithmetic (DA) [6] and Multiplication constant ISSN: 2231-5381 Multiple (MCM)-based commence [7]. The simple DCT design offers a bit-serial DA-based commence but enormous hardware space is required for additional ROMs and control logics. The low-power CORDIC-using DCT design used the data correlations, it reduces the correlation between adjacent pixels are effectively used to avoid the interior CORDIC repetitions. In DCT, in producing the frequency domain outputs (DCT constants) all the calculation are not equally vital. A low-power CORDIC-using DCT design, where the DCT constants are economically abused to achieve the power savings minimum image quality degradation. The conventional CORDIC architecture is a data dependencies because the present iteration is depend on previous iteration. A lookahead CORDIC design [8]–[9] are preferred to overcome the characteristic data-dependencies in the traditional CORDIC architecture. The rest of the paper is structured as follows, The Existing system is given in Section II.The Proposed system is given in Section III. The Simulation results and analysis is given in Section IV. Conclusion is given in Section V. II.EXISTING SYSTEM A.CORDIC Architecture: In CORDIC the basic fundamental is to using a rotation matrix [4], which is illustrated as follows http://www.ijettjournal.org Page 270 International Journal of Engineering Trends and Technology (IJETT) – Volume 20 Number 6 – Feb 2015 for column DCT , we use another DCT.The 2-D DCT procedure with separate 1-D DCT is shown in fig [1]. (1) where the vector correspondent constitution of x and y axes represent x and y, correspondingly, the i th repetition step represent i, σ is the bit that can be +1 or −1 pointing the clockwise and counter clockwise path of the vector revolution, z is the aggregate angle, and α is the defined angle. In the CORDIC architecture, by using vectoring mode we can easily calculated the amplitude and argument of a given vector, while by the revolution mode the sine and cosine values can be computed. Lookahead CORDIC Approach: In the CORDIC equation shown in (1), the data from the preceding stage repetition must be computed first to determine the result of the present stage. The conventional CORDIC are data dependencies because the present iteration is depend upon the previous iteration. Lookahead CORDIC [8]–[10] is enhanced, to overcome the information dependent, where lookahead denote to finish the iterations at one time. Fig 1: 8 × 8 2-D DCT procedure with separable 1-D DCT. The 8*8 1-DCT Transform is represented as (3) x(i) is the input information, x(k) is the 1-DCT output information . X is the output vector, x is the input vector.DCT can be implemented by shifters and adders. After 2-D DCT procedure, the DCT inputs are in spatial domain and the outputs are in frequency domain [13]. The DCT has the energy B. CORDIC Operations Of Scale-Factor compression feature, so the a low frequency In the CORDIC process, after every repetition the component is mostly focused on DCT coefficient. revolution vector is measured and aggregate Hardware design of CORDIC-using 1-D DCT is shown in fig.2. concordant to the following equation: (2) Where n is the number of repetition. The scale factor is determined by the number of iteration. By the low power CORDIC design changing the number of repetition, In only one guidance, where the vector revolves to the destination angle. The consistent scale factor must be changed concordant to the repetition. C.CORDIC-Using DCT Architecture The 2-D DCT process is disintegrated into an 1-D DCT .In 2D DCT process we are using two 1-DCT inorder to perform a row DCT and column DCT. Inorder to perform row DCT we use an 1-D DCT, ISSN: 2231-5381 Fig. 2. Hardware architecture of CORDIC-based 1-D DCT. http://www.ijettjournal.org Page 271 International Journal of Engineering Trends and Technology (IJETT) – Volume 20 Number 6 – Feb 2015 After quantization the high frequency DCT coefficient become lessen because the low frequency component are highly sensitive to human eyes when compare to high frequency component .In CORDIC,large number of repetition is used for low frequency coefficient in order to get the accurate result, where the high frequency coefficient require a small no of iteration. TABLE I Required iteration and direction for vector rotation D.Low Power DCT Architecture Using Look ahead CORDIC In the conventional CORDIC structure having the crossing datapath, the two separate CORDIC data path is not feasible and also changing the number of iteration in conventional CORDIC structure[1].The lookahead approach-based design of CORDIC module is shown in fig.3.In the look ahead CORDIC we assign a different number of iteration to the cordic datapath.In the look ahead, all the interior datapath become independent, and the number of iteration can be easily controlled [8]-[10]. For example if we revolve the vector of an angle π/16, only the ith repetition (i=0, 1, 3, 10) are required, the rest of repetition can be avoided for power saving. III. PROPOSED SYSTEM. The Recursive CORDIC design block diagram is shown in Fig.4. In the recursive style the equations (4) must be appareled. The representation “>> (n-1)” denote the shifting process.In Fig.4 shows the recursive design and the primary inputs are X0 andY0 for the first repetition. For rest of the repetition the output from the adder is get back to the input via a Multiplexer. Fig 3: lookahead approach-based architecture of CORDIC module. The most interesting fact is that the look ahead technique is enforced to the CORDIC, it eliminate the high shift term because of using less number of Fig. 4. Recursive CORDIC Architecture. iteration, means the CORDIC with low calculational difficulty, a CORDIC using low power DCT .By using select signal the multiplexer is limited. architecture can be derivative. By using the lookahead The block with symbol “+” mean an adder. The cordic we can achieve a low power owing to lesser significance of di decide the addition process has to number of repetition. Required iteration and direction be approved out. To attain exact output, N-number for vector rotation is shown in table I. ISSN: 2231-5381 http://www.ijettjournal.org Page 272 International Journal of Engineering Trends and Technology (IJETT) – Volume 20 Number 6 – Feb 2015 of repetition is known by the lookahead CORDIC architecture and then the output is get back to the DCT OUTPUT: The output image file size is that 238KB input via the multiplexer. X (i+1) = K (i) [x (i) – y (i) d (i) 2^-i] (4) Y (i+1) = K (i) [y (i) + x (i) d (i) 2^-i] The recursive architecture requires less area and also for calculating few angle inputs consumes lesser power, for the physical implementation .In terms of area, power the recursive design of CORDIC core is more efficient. In the recursive CORDIC both iteration and recursive function is used Fig. 6. DCT output image. IDCT OUTPUT IV.SIMULATION RESULTS AND ANALYSIS The various design of CORDIC based DCT architecture is implemented using front end. The design is coded in VHDL and simulated using ModelSim 6.3f software. The analysis of area and power are performed using Xilinx ISE 8.1 software. Fig. 7. IDCT output image. The simulation result for implementing existing methodology using lookahead CORDIC based DCT SIMULATION RESULT: architecture is determined using ModelSim 6.3f software. The generated output for every clock pulse is shown in the Fig.11. The Area and Power report for lookahead CORDIC using DCT design is determined using Xilinx ISE 9.1. Total Equivalent Gate Count for implementing the design is 9270. The total power estimation is 43 mW. INPUT IMAGE: By using MATLAB the input image will be get in terms of pixel by the MATLAB R2007b. The input image file size is that 288KB Fig 8: Simulation result for CORDIC based DCT architecture. Fig. 5. Input image. ISSN: 2231-5381 Since the Existing methodology had various complexities such as area, power . To overcome http://www.ijettjournal.org Page 273 International Journal of Engineering Trends and Technology (IJETT) – Volume 20 Number 6 – Feb 2015 these difficulties the architecture is modified by recursive architecture. The simulation result for recursive architecture using ModelSim 6.3f. The Area and Power report for recursive architecture is determined using Xilinx ISE 9.1. Total Equivalent Gate Count for implementing the design is 3711. The total power estimation is 34 mW.(Table.1) Table .II Comparision Table Area Power ( Gate Count) (mW) area.In terms of area, power the recursive design of CORDIC core is more efficient. In the recursive CORDIC both iteration and recursive function is used. The Recursive CORDIC based DCT architecture is coded using VHDL and simulated using ModelSim 6.3f. The gate count and power consumption of the lookahead and recursive CORDIC were analyzed using Xilinx ISE 8.1 software. V1. REFERENCES [1] Min-Woo Lee, Ji-Hwan Yoon, Jongsun Park “Reconfigurable CORDICBased Low-Power DCT Architecture Based on Data Priority” 2014 Volume: 22, Issue: 5, IEEE Look ahead CORDIC 9270 43 [2] G. K. Wallace, “The JPEG still picture compression standard,” IEEE Trans. Consum. Electron., vol. 38, no. 1, pp. 18–34, Feb. 1992. Recursive CORDIC 3711 [3] D. L. Gall, “MPEG: A video compression standard for multimedia applications,” Commun. ACM, vol. 34, no. 4, pp. 46–58, Apr. 1991. 34 [4] J. E. Volder, “The CORDIC trigonometric computing technique,” IRE Trans. Electron. Comput., vol. 8, no. 3, pp. 330–334, Sep. 1959. [5] E. P. Mariatos, D. E. Metafas, J. A. Hallas, and C. E. Goutis, “A fast DCT processor, based on special purpose CORDIC Rotators,” in Proc. IEEE Int. Symp. Circuits Syst., Jun. 1994, pp. 271–274. V.CONCLUSION In the conventional DCT architecture, the output of the frequency domain all the calculation are not evenly significant. This paper conferred a lowpower Recursive CORDIC-using DCT design, To assign the numbers of CORDIC repetition where the significant differences in DCT coefficients were effectually abused. Instead of conventional CORDIC, to overcome the information-needs the Lookahead CORDIC design were effectually used. In proposed the Recursive CORDIC design is used in DCT architecture in order to reduce power and ISSN: 2231-5381 [6] S. Yu and E. E. Swartziander, “DCT implementation with distrib-uted arithmetic,” IEEE Trans. Comput., vol. 50, no. 9, pp. 985–991, Sep. 2001. [7] B. Kim and S. G. Ziavras, “Low-power multiplierless DCT for image/video coders,” in Proc. IEEE Int. Symp. Consum. Electron., May 2009, pp. 133–136. [8] J. Li, “Sign lookahead CORDIC,” M.S. thesis, Dept. Electr. Eng., Nat. Cheng Kung Univ., Tainan, Taiwan, 2008. [9] S. Wang and E. E. Swartzlander, “Merged CORDIC algorithm,” in Proc. IEEE Int. Symp. Circuits Syst., May 1995, pp. 1988–1991. [10] B. Gisuthan and T. Srikanthan, “Pipelining flat CORDIC based trigonometric function generators,” Microelectron. J., vol. 33, nos. 1–2, pp. 77– 89, Jan. 2002. http://www.ijettjournal.org Page 274