FPGA Design for Efficient Architecture for the Convolution Encoder

advertisement

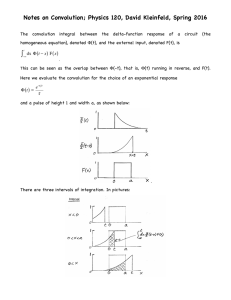

International Journal of Engineering Trends and Technology (IJETT) – Volume 9 Number 2 - Mar 2014 FPGA Design for Efficient Architecture for the Convolution Encoder and Viterbi Decoder Vinita Soni TIT Bhopal Madhya Pradesh Prof. Sandip Nemade TIT Bhopal Madhya Pradesh Abstract- Convolution encoding is used in almost all digital communication systems to get better gain BER and all applications need high throughput rate. The main aim of this paper is to design FPGA based convolution encoder and viterbi decoder which encodes/decodes the data. In this paper we are presenting an efficient design structure for the convolution encoder and decoder (Viterbi) for the FPGA implementation we also analyzed the developed mode for noisy situations for it correcting capabilities. The proposed model is synthesized and simulated using Xilinx ISE 14.4 software which shows that the proposed design effectively reduces the resource requirements and the power analysis on X-Power Analyzer shows considerable reduction in power requirements. . Keywords- Convolution Encoder, Viterbi Decoder, FPGA VHDL 1. Introduction The convolution codes falls in non-block codes whose performance are superior to block code sin the same coding efficiency situation [1]. As the name suggest the coding scheme performs a convolution of the input stream with the encoder's impulse responses. This procedure spreads the bits information over the large sequences which results the increased of transmission redundancy. In practice these operations are performed by using EX-OR operation. Since the information is encoded by means of correlations the decoder needs to be able to retrieve that information to correct any possible error in the sequence. The complexity of the receiver increases exponentially with the depth of trace back and coding rate. Therefore an optimum designing is required to make a practical decoder with the FPGA technology. The FPGA technology is particularly chosen because it can be used to design highly parallel architecture which reduces the processing delay and not feasible for microprocessor or microcontrollers. As showed in Table 1, the constraint length, code rate and polynomial of convolution code. Table 1: Code Parameters Of Different Standards Code parameter Standard Constraint length LTE 7 1/3 (133,171,165)oct UMB 9 1/3 (577,633,711)oct WIMAX 7 1/2 (133,171,)oct ISSN: 2231-5381 Code rate polynomial The rest of this paper is organized as follows. Section II gives a review of some recent development and the published research arch literature.The background information about Convolution encoder and Viterbi decoder is presented in Section III. The proposed architecture is discussed in the section IV followed by the synthesis and power estimation results in Section V. in section VI simulation waveform is analysed and finally conclusions are given in Section VII. 2. Literature Review In this section some of the important literatures related to the proposed work are discussed. Yan Sun et al [1] presented FPGA Design and Implementation of a Convolution Encoder and a Viterbi Decoder Based on 802.11a for OFDM. The proposed design uses full-parallel structure improve computational speed for the addcompare-select(ACS) modules, adopts optimal data storage mechanism and supports a generic, robust and configurable Viterbi decoder with constraint length of 7, code rate of 1/2 and decoding depth of 36 symbols. High-Speed Low-Power Viterbi Decoder Design for TCM Decoders is presented by Jinjin He et al [2]. They proposed a pre-computation architecture in corporate with Talgorithm for Viterbi decoder (VD),which can effectively reduce the power consumption without degrading the decoding speed much .A general solution to deriving the optimal pre-computation steps is also given in the paper. Nayel Al-Zubi [3] proposed Pipelined Viterbi Decoder using a carry-save technique, which gets the advantage that the critical path in the ACS feedback becomes in one direction and get rid of carry ripple in the “Add” part of ACS unit. Li Zhou et al [4] presented an architecture of flexible Viterbi decoder for Software Defined Radio (SDR). The SDR requires reconfigurable platform due to the reuse of hardware and in order to support multi-standard service, a decoder compatible for different protocols is needed. In this paper, we designed a flexible Viterbi decoder which is compatible with Wi MAX, UMB and LTE’s channel coding scheme. High efficient cascaded Add-compare-select unit architecture and sliding window method for trace back a represented. Usana Tuntoolavest et al [5] presented the implementation result of List-of2 soft-decision Viterbi decoder on FPGA platform. Unified NULL Convention Logic Environment which is an end-to-end toolset for creating asynchronous designs using NULL Convention Logic (NCL) is presented by Robert B. Reese et al [6]. Liu Yanyan proposed et al [7] proposed a parallel decoding algorithm to achieve high speed and parallel Viterbi decoding method, which is realized easily by FPGA http://www.ijettjournal.org Page 74 International Journal of Engineering Trends and Technology (IJETT) – Volume X Issue Y- Month 2014 3. Convolution Encoder The convolution code is a kind of linear coding method with memory packet and equivalent to convolution between the input information stream and an impulse response. The constraint length of the convolution code determines the coded error resilience ability, constraint length is longer, error resilience capability is stronger, but the decoding complexity is increased significantly [6].The difference between block codes and convolution codes is the encoding principle. In the block codes, the information bits are followed by the parity bits. In convolution codes the information bits are spread along the sequence. That means that the convolution codes map information to code bits not block wise, but sequentially convolve the sequence of information bits according to some rule. The code is defined by the circuit which consist soft different number of shift registers all owing building different codes in terms of complexity [8]. Convolution codes are commonly specified by three parameters (n, k and m). n = number of output bits k = number of input bits m = number of memory registers The quantity k/n called the code rate, is a measure of the efficiency of the code. Commonly k and n parameters range from 1 to 8, m from 2 to 10 and the code rate from 1/8 to 7/8 except for deep space applications where code rates as low as 1/100 or even longer have been employed. Often the manufacturers of convolution code chips specify the code by parameters (n,k,L), the quantity L is called the constraint length of the code and is defined byConstraint Length, L = k (m-1)The constraint length L represents the number of bits in the encoder memory that affect the generation of the n output bits. The constraint length L is also referred to by the capital letter K, which can be confusing with the lower case k, which represents the number of input bits. In some books K is defined as equal to product of the k and m. Often in commercial spec, the codes are specified by (r, K), where r = the code rate k/n and K is the constraint length. The constraint length K however is equal to L -1 [10]. 3.1 Structure of the Convolution Encoder A convolution code is generated by passing the information sequence to be transmitted through a linear finite-state shift register. In general, the shift register consists of K (k-bit) stages and n linear algebraic function generators as shown in the Fig. 1. Figure 1 shows the structure of convolution encoder of rate 1/3. Each input bit is coded into 3 output bits. The constraint length of the code is 2. The 3 output bits are produced by the 3 modulo-2 adders by adding up certain bits in the memory registers. The selection of which bits are to be added to produce the output bit is called the generator polynomial (g) for that output bit. The polynomials give the code its unique error protection quality. One (3,1,4) code can have completely different properties from an another one depending on the polynomials chosen . 3.2 Trellis Diagram Trellis diagrams are messy but generally preferred over both the tree and the state diagrams because they represent linear time sequencing of events. The x-axis is discrete time and all possible states are shown on the y-axis. We move horizontally through the trellis with the passage of time. Each transition means new bits have arrived. Figure 2: Trellis Diagram of Convolution Encoder 4. Viterbi Decoder Viterbi decoding is the best known implementation of the maximum likely-hood decoding. Here we narrow the options systematically at each time tick. The principal used to reduce the choices is this. 1. The errors occur infrequently. The probability of error is small. 2. The probability of two errors in a row is much smaller than a single error, which are distributed randomly. The Viterbi decoder examines an entire received sequence of a given length. The decoder computes a metric for each path and makes a decision based on this metric. All paths are followed until two paths converge on one node. Then the path with the higher metric is kept and the one with lower metric is discarded. The paths selected are called the survivors. For an N bit sequence, total numbers of possible received sequences are 2N. Of these only 2kL are valid. The Viterbi algorithm applies the maximum-likelihood principles to limit the comparison to Figure 1: Basic structure of convolution encoder ISSN: 2231-5381 2 to the power of k L surviving paths instead of checking all paths. The most common metric used is the Hamming distance metric. Following are the main advantages of the Viterbi algorithm http://www.ijettjournal.org Page 75 International Journal of Engineering Trends and Technology (IJETT) – Volume X Issue Y- Month 2014 Guaranteed to find the ML solution The complexity is only O(2K) Complexity does not depend on the number of original data bits Easily implementable in hardware 4.1 Working Steps Takes advantage of the structure of the trellis Goes through the trellis one stage at a time. At each stage, finds the most likely path leading into each state (surviving path) and discards all other paths leading into the state (non-surviving paths) Continues until the end of trellis is reached At the end of the trellis, traces the most probable path from right to left and reads the data bits from the trellis In principle whole transmitted sequence must be received before decision. However, in practice storing of stages with length of 5K is quite adequate. 5. Proposed Design Synthesis and Analysis 5.1 HDL Synthesis Report Macro Statistics RAMs 8x6-bit single-port Read Only RAM 1 1 Multiplexers 16-bit 7-to-1 multiplexer X ors 1-bit xor2 1 1 560 560 Primitive and Black Box Usage: # BELS # LUT2 # LUT3 149 29 5 # # # # 8 24 76 7 LUT4 LUT5 LUT6 MUXF7 # IO Buffers # IBUF # OBUF 52 36 16 Time Delay for Different Operations Sequences Figure 3: RTL of the Convolution Encoder Delay(ns) in Previous Delay(ns) in Proposed 000 7.00 7.00 001 10.00 9.50 010 9.00 8.50 011 6.00 6.00 100 7.00 7.00 101 7.00 7.00 110 9.50 9.00 111 7.00 6.00 Power Dissipation Activity Rate 50% 100% Dissipation(W) in Previous Dissipation(W) Proposed 0.014 0.011 0.030 0.024 in Figure 4: RTL of the Signal Generator Unit ISSN: 2231-5381 http://www.ijettjournal.org Page 76 International Journal of Engineering Trends and Technology (IJETT) – Volume X Issue Y- Month 2014 [3] D.A.F. El-Dib, M.I. Elmasry, “Low-power register-exchange Viterbi decoder for high-speed wireless communications”, Proceedings of IEEE International Symposium on Circuitsand Systems, IEEE Conference Publishing Services, May 26-29, 2002, pp. 737–740 6. Simulated Waveform [4] P. J. Black and T. H. Meng, “A 140-Mb/s, 32-state, radix-4 Viterbi decoder”, IEEE Journal of Solid-State Circuits, Vol. 27, No. 12, 1992, pp. 1877-1885. [5] D. Yeh, et al., “RACER: a reconfigurable constraint-length 14 Viterbi decoder”, Proceedings of IEEE Symposium on FPGAs for Custom Computing Machines, IEEE Conference Publishing Services, April 17-19, 1996, pp. 60-69. [6] W. Ching-Wen and C. Yun-Nan, “Design ofViterbi decoders with in-place state metric update and hybrid traceback processing”, Proceedings of IEEE Workshop on Signal Processing Systems, IEEE Conference Publishing Services, September 26-28, 2001, pp. 5-15. [7] Xilinx Corporation, “Viterbi decoder: product specification (v6.2)”, October, 2007. Figure. 6.1 Convolution encoder simulation waveform [8] L. Bissi, et al., “A Viterbi decoder architecture for a standard-agile and reprogrammable transceiver”, Integration-the VLSI Journal, Vol.41, No. 2, 2008, pp. 161-170. [9] Y. Gang, T. Arslan, and A. T. Erdogan, “An efficient pre-traceback approach for Viterbi decoding in wireless communication”, Proceedings of IEEE International Symposium on Circuits and Systems, IEEE Conference Publishing Services, May 23-26, 2005, pp. 5441–5444. [10] B. Pandita and S. K. Roy, “Design and implementation of a Viterbi decoder using FPGAs”, Proceedings of the 12th International Conference on VLSI Design, IEEE Conference Publishing Services, January 10-13, 1999, pp. 611-614. [11] W. H. W. Tuttle bee, “Software-defined radio: facets of a developing technology”, IEEE Personal Communications Magazine, Vol. 6,No. 2, 1999, pp. 38-44. Figure. 6.2 viterbi decoder simulation waveform 7. Conclusion In this paper, we presented a low complexity low area and low power architecture for Viterbi decoder for different applications. The proposed decoder can deal the convolution code in wireless standard WiMAX, UWB, and LTE etc. It is reconfigurable and suitable for software define radio platform also. The proposed architecture is highly efficient the comparison shows that it outperforms the previous architecture by 25% when handling different code parameter. The strategy we applied made a good trade off between performance, power, area and delay. Hence future scope indicates testing of convolution encoder and viterbi decoder with more than 9 bit constraint length. 8.References [1] M. Irfan, et al., “Design and Implementation of Viterbi Encoding and Decoding Algorithm on FPGA”, Proceedings of the 17th International Conference on Microelectronics, December 13-15, 2005, pp. 234-239. [2] G. Forney, “Convolutional codes II. Maximum-likelihood decoding”, Information and Control, Vol. 25, No. 3, 1974, pp. 222-266. ISSN: 2231-5381 http://www.ijettjournal.org Page 77