Microprocessors 2 stage

advertisement

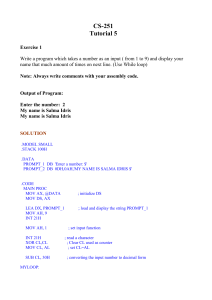

Microprocessors 2nd stage 7-5-2012 Lec. (17) College of sciences for women ((())) Dept. of computer sciences Year 2012-2013 22.4 Segment: Offset Memory address Since all registers in the 8086 are 16 bits wide, the address space is limited to 216, or 65,536 (64 K) locations. As a consequence, the memory is organized as a set of segments. Each segment of memory is a linear contiguous sequence of up to 64K bytes. In this segmented memory organization, we have to specify two components to identify a memory location: a segment base and an offset. This two-component specification is referred to as the logical address. The segment base specifies the start address of a segment in memory (called paragraphs) that can exist in a 20-bit address space and the offset specifies the address relative to the segment base. The offset is also referred to as the effective address. The Instruction Pointer register contains the offset address of the next sequential instruction to be executed. The IP register cannot be directly modified. Nonsequential instructions which cause branches, jumps and subroutine calls will modify the value of the IP register. Figure 27 illustrates how the address is formed. Figure 27: Memory address based upon segment and offset model. Lecturer: Salah Mahdi Saleh 99 It is obvious from this model that the same memory address can be specified in many different ways. In any case, the 20-bit address is calculated by taking the 16-bit address value in the appropriate segment register and then doing an arithmetic shift left by 4 bit positions. Since each left shift has the effect of a multiplication by 2, four shifts multiply the address by 16 and result in the base addresses for the paragraph boundaries as shown in Figure 27. The offset value is a true negative or positive displacement centered about the paragraph boundary set by the segment register. Figure 27 shows that the physical address range that is accessible from a segment register value of 9000h extends from 88000h to 97FFFh. Offset addresses from 0000h to 7FFFh represent a positive displacement (towards higher addresses) and addresses from 0FFFFh to 8000h represent negative displacements. Once the paragraph boundary is established by the segment register, the offset value (either a literal or register content) is sign extended and added to the shifted value from the segment register to form the full 20-bit address. This is shown in Figure 28. Figure 28: Converting the logical address to the physical address in the 8086 architecture. While the physical address of memory operands is 20-bits, or 1 MByte, the I/O space address range is 16-bits, or 64K. The four, higher order address bits are not used when addressing I/O devices. Lecturer: Salah Mahdi Saleh 100 22.5 Memory Addressing Modes The 8086 architecture provides for 8 addressing modes. The first two modes operate on values that are stored in internal registers or are part of the instruction (immediate values). These are: 1. Register Operand Mode: The operand is located in one of the 8 or 16 bit registers. Example of Register Operand Mode instructions would be: MOV AX,DX MOV AL,BH INC AX 2. Immediate Operand Mode: The operand is part of the instruction. Examples of the Immediate Operand Mode are: MOV AX,0AC10h ADD AL,0AAh There is no prefix, such as the ‘#’ sign, to indicate that the operand is an immediate. The next six addressing modes are used with memory operands, or data values that are stored in memory. The effective addressing modes are used to calculate and construct the offset that is combined with the segment register to create the actual physical address used to retrieve or write the memory data. The physical memory address is synthesized from the logical address contained in the segment register and an offset value, which may or may not be contained in a register. The segment registers are usually implicitly chosen by the type operation being performed. Thus, instructions are fetched relative to the value in the CS register; data is read or written relative to the DS register; stack operations are relative to the SP register and string operations are relative to the ES register. Registers may be overridden by prefacing the instruction with the desired register. For example: ES:MOV AX,[0005h] will fetch the data from ES:0005, rather than from DS:0005. The effective address (offset address) can be constructed by adding together any of the following three address elements: Lecturer: Salah Mahdi Saleh 101 a. An 8-bit or 16-bit immediate displacement value that is part of the instruction, b. A base register value, contained in either the BX or BP register, c. An index value stored in the DI or SI registers. 3. Direct Mode: The memory offset value is contained as an 8-bit or 16-bit positive displacement value. Unlike the 68K, the offset portion of the address is always a positive number since the displacement is referenced from the beginning of the segment. The Direct Mode is closest to the 68K’s absolute addressing mode, however, the difference is that there is always the implied presence of the segment register need to complete the physical address. For example: MOV AX,[00AAh] copies the data from DS:00AA into the AX register, while, CS:MOV DX,[0FCh] copies the data from CS:00FC into the DX register. Notice how the square brackets are used to symbolize a memory instruction and the absence of brackets means an immediate value. Also, two memory operands are not permitted for the MOV instruction. The instruction, MOV [00AAh],[1000h] is illegal. Unlike the 68K MOVE instruction, only one memory operand is permitted. 4. Register Indirect Mode: The operand offset is contained in one of the following registers: • BP • BX • DI • SI The square brackets are used to indicate indirection. The following code snippet writes the value 55h to memory address DS:0100. MOV BX,100h MOV AL,55h Lecturer: Salah Mahdi Saleh 102 MOV [BX],AL 5. Based Mode: The memory operand is the sum of the contents of the base register, BX or BP and the 8-bit or 16-bit displacement value. The following code snippet writes the value 0AAh to memory address DS:0104. MOV BX,100h MOV AL,0AAh MOV [BX]4,AL The Based Mode instruction can also be written: MOV [BX-4],AL. Since the displacement can be a positive or negative number, the above instruction is equivalent to: MOV [BX + 0FFFCh],AL 6. Indexed Mode: The memory operand is the sum of the contents of an index register, DI or SI, and the 8-bit or 16-bit displacement value. The following code snippet writes the value 055h to memory address ES:0104. MOV DI,100h MOV AL,0AAh MOV [DI]4,AL The code snippet above illustrates another difference between using the index registers and the base registers. The DI register defaults to ES register as its address segment source, although the ES register may be overridden with a segment override prefix on the instruction. Thus, DS:MOV [DI+4],AL would force the instruction to use the DS register rather than the ES register. 7. Based Indexed Mode: The memory operand offset is the sum of the contents of one of the base registers, BP or BX and one of the displacement registers, DI or SI. The DI register is normally paired with the ES register in the Indexed Mode, but when the DI register is used Lecturer: Salah Mahdi Saleh 103 in this mode, the DS register is the default segment register. The following code snippet writes the value 0AAh to memory location DS:0200h MOV DX,1000h MOV DS,DX MOV DI,100h MOV BX,DI MOV AL,0AAh MOV [DI+BX],AL The instruction MOV [DI+BX],AL may also be written: MOV [DI][BX],AL 8. Based Indexed Mode with Displacement: The memory operand offset is the sum of the contents of one of the base registers, BP or BX, one of the displacement registers, DI or SI and an 8-bit or 16-bit displacement. The DI register is normally paired with the ES register in the Indexed Mode, but when the DI register is used in this mode, the DS register is the default segment register. The following code snippet writes the value 0AAh to memory location DS:0204h: MOV DX,1000h MOV DS,DX MOV DI,100h MOV BX,DI MOV AL,0AAh MOV [DI+BX]4,AL The instruction MOV [DI+BX]4,AL may also be written: MOV [DI][BX]4,AL or MOV [DI+BX+4],AL. Offset calculations can lead to very interesting and subtle code defects. Examine the code segment shown below: MOV DX,1000h MOV DS,DX Lecturer: Salah Mahdi Saleh 104 MOV BX,07000h MOV DI,0FF0h MOV AL,0AAh MOV [DI+BX+0Fh],AL This code assembles without errors and writes the value 0AAh to DS:7FFF. The physical address is 17FFFh. Now, examine the next code segment: MOV DX,1000h MOV DS,DX MOV BX,07000h MOV DI,0FF0h MOV AL,0AAh MOV [DI+BX+10h],AL This code assembles without errors and writes the value 0AAh to DS:8000. However, the physical address is not 18000h, the next physical location in memory, it is actually 08000h. We have actually wrapped around the offset and gone from memory location 17FFFh to 8000h. If we had been in a loop, writing successive values to memory, we would have had an interesting problem to debug. Lecturer: Salah Mahdi Saleh 105