قارعلا ةيروهمج

advertisement

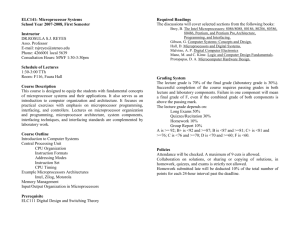

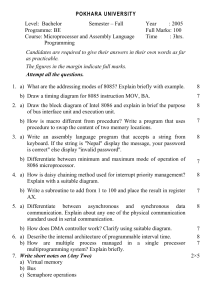

جمهورية العراق وزارة التعليم العالي والبحث العلمي وثق ما تفعل وافعل ما توثق ادارة الجودة الشاملة جامعة بابل كلية العلوم للبنات .......................... قسم علوم الحاسبات ........................... الدراسات االولية /الدراسات العليا رقم المقرر الدولي Curriculum and Process Design Evidence )CAPDE (Q.S.P-7-3-1.2.3.-02-01 العـدد: دليل تصاميم المناهج والمقررات Course NO.: التاريخ: ـــــــــــــــــــــــــــ استمارة عرض المقرر على الطلبة Microprocessors and Assembly Language اسم المقرر........................................... : -1 نعم إجباري .......اختياري........ 2 4 6 -2عدد الوحدات ........... :عدد الساعات االجمالي ..........النظري .......... -3المرحلة الدراسية : الثانية -4اسم التدريسي أو التدريسيين -1صالح مهدي صالح -2 -3 -4 -5الشهادة واللقب العلمي -1ماجستير علوم حاسبات (مدرس) -2 -3 -4 ()2-1 2 العملي .................. برنامج المقرر المقدمة:أوال This unit guide is intended to provide a general idea of the teaching content and assessment criteria for the unit entitled Microprocessors and assembly language. General aims are to provide an understanding of the operation of microprocessors and their interfacing components, and to offer essential design considerations in Microprocessor and Computer Interfacing applications. Microprocessors and Interfacing deals with the general principles of microprocessor design and interfacing by looking at the Intel 8086 microprocessor and its associated peripheral interface chips. Programming the microprocessor is done using the MASM assembly language under visual studio 2008 environment on the PC. This is done to emphasis the sequence of operations of software code and their implications on the hardware. The unit deals with microprocessor architecture, operation of registers and data manipulation as well a program control. أهداف المقرر:ًثانيا 1. Understand components of the computers, microprocessors. 2. Know how to approach and undertake microprocessor development. 3. Learning role of CPU, registers, buses. 4. Know how interface memory and peripheral devices to a microprocessor. 5. Learning addressing modes (Immediate, direct, extended, indexed, indexed-indirect, and relative addressing modes). 6. Know the architecture of the 80x86-type microprocessor. Its capabilities and limitation and how it fits in with modern computers. 7. Understanding the function of each pin in 8086 microprocessor. 8. Learning interrupt vectors, interrupt process, interrupt priorities, external and advanced interrupts 9. Learning how to write program in assembly language using MASM under Visual C++ environments. 10. Learning assembly-programming styles, structured assembly language programming مفردات المقرر او المحتوى:ًثالثا Week 1 2 3 4 5 6 7 Theoretical Review of microprocessor syllabus and an introduction to microprocessors Microprocessor History The Computer Level Hierarchy Microprocessor Architecture, Microprocessors and Memory Central processing unit (CPU), data/program memory input/output devices and bus structure. 8 9 What is data bus, address bus and control bus. CPU registers, Register Transfer Memory 10 11 12 1st Examination Fetch and Execute cycles interrupts, Interrupt Handling, CONTROL UNIT. 13 Instruction Set Architecture, Number of Addresses 14 ADDRESSING MODES 15 RISC and CISC Designs (Evolution, principles, features). 16 Instruction Types, Instruction Formats. 17 Half-year Break 18 Advantages of High-Level Languages, Assembly Language Programming The Intel x86 Architecture, The Architecture of the 8086 CPU, 19 Pin assignments of 8086 microprocessor 20 2nd Examination 21 Internal architecture of the 8086microprocessor (registers) 22 Internal architecture of the 8086 microprocessor (memory segmentation & stack) Internal architecture of the 8086 microprocessor (memory segmentation & stack) Addressing modes of 8086 microprocessor with examples 23 24 Assembly Language Programming the 8086 Architecture. 25 The memory interface: read operation - Read bus cycles w/ timing, write operation - Write bus cycle w/ timing I/O Port Addressing, Instruction Pipelining 26 27 Cache Memory 28 Processor Performance Metrics 29 3rd Examination 30 رابعا :طرائق التدريس المعتمدة لتنفيذ المقرر تستعمل الطريقتين التاليتين من خالل الجمع بينهما: -1طريقة المحاضرة. -2طريقة المناقشة. وتستعمل الوسائل التعليمية التالية لتنفيذ الطريقتين أعاله: الحاسوب مع أجهزة العرض. المختبرات. السبورة. خامسا :توزع درجات المقرر وفق لواحد أو أكثر مما يأتي : النشاط النسبة المئوية امتحانات العملي خالل السنة ( ثالث امتحانات ) %10 امتحانات النظري خالل السنة (ثالث امتحانات ) %23 الواجبات العمليه %3 االمتحانات السريعة ()quizzes %4 امتحان العملي النهائي %20 امتحان النظري النهائي %40 المجموع الكلي %100 المصادر والمراجع:ًسادسا 1. J. L. Hennessy and D. A. Patterson, Computer Architecture : A Quantitative Approach, 4th edition, Morgan Kaufmann Publishers Inc., 2007. 2. H. El-Rewini and M. A. El-Barr, Fundamentals of computer organization and architecture”, John Wiley, 2005. 3. J. T. Streib, Guide to Assembly Language: A Concise Introduction, Springer-Verlag London Limited, 2011. 4. Sivarama P. Dandamudi. "Fundamentals of Computer Organization and Design". Springer-verlag Inc., New York, USA, 2003. 5. KIP R. IRVINE, "Assembly Language for x86 Processors", 6th edition, Prentice Hall, 2011. محمد عبد هللا ناصر.د : القسم.ر صالح مهدي صالح:اسم التدريسي التوقيع التوقيع )2-2(