CHAPTER 13: DESIGN DEVELOPMENT TOOLS SECTION 13.1: SIMULATION

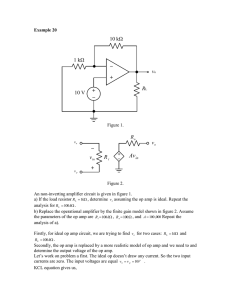

advertisement