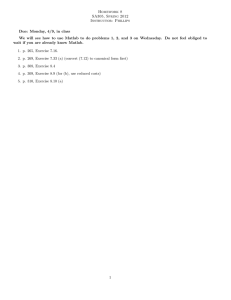

Analog Dialogue

advertisement