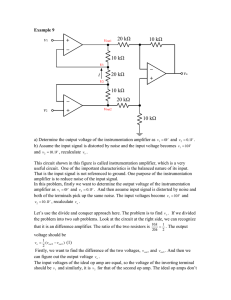

|

advertisement