Analog Dialogue

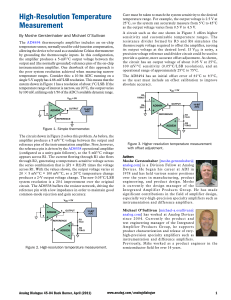

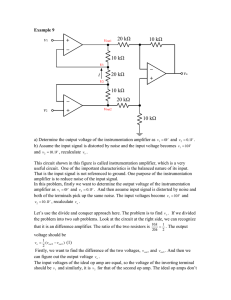

advertisement