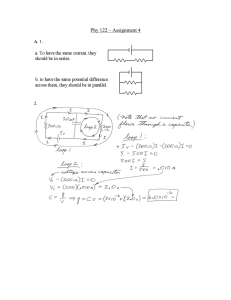

Controller Design Chapter 9

advertisement