EVAL-ADuC7026 User Guide UG-669

advertisement

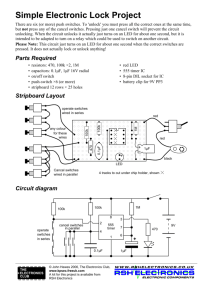

EVAL-ADuC7026 User Guide UG-669 One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com Evaluating the ADuC7026 MicroConverter FEATURES Full featured evaluation system for the ADuC7026 2-layer PCB (4” × 5” form factor) 9 V power supply regulated to 3.3 V on board 4-pin UART header to connect to RS-232 interface cable 20-pin standard JTAG connector Demonstration circuit 32.768 kHz watch crystal to drive the PLL clock ADR291 2.5 V external reference chip Reset/download/IRQ0 push-buttons Power indicator/general-purpose LEDs Access to all ADC inputs and DAC output from external header. All device ports are brought out to external header pins. Surface-mount and through-hole general-purpose prototype area External memory and latch footprint ADuC7026 evaluation board Serial download cable International power supply CD containing evaluation software ADuC7026 data sheet example code ADuC7026 evaluation board mIDAS-Link JTAG emulator USB cable Serial download cable International power supply CD containing evaluation software ADuC7026 data sheet example code GENERAL DESCRIPTION This user guide, which replaces AN-744, refers to revision B2 of the ADuC7026 MicroConverter® evaluation boards. Two models of the development kit are available: EVAL-ADuC7026QSZ is the QuickStart™ Development System; EVAL-ADuC7026QSPZ is the QuickStart Plus Development System. All references in this user guide to the physical orientation of components on the evaluation board are made with respect to a component-side view of the board with the prototype area appearing at the bottom of the board. The evaluation board is laid out to minimize coupling between the analog and digital sections of the board. To this end, the ground plane is split with the analog section on the left side and a digital plane on the right side of the board. The regulated 3.3 V power supply is routed directly to the digital section and is filtered before being routed into the analog section of the board. EVALUATION BOARD 05032-101 QUICKSTART DEVELOPMENT SYSTEM KIT CONTENTS QUICKSTART PLUS DEVELOPMENT SYSTEM KIT CONTENTS Figure 1. Typical Evaluation Board Rev. B | Page 1 of 16 UG-669 EVAL-ADuC7026 User Guide TABLE OF CONTENTS Features .............................................................................................. 1 S1-2 VOCM........................................................................................5 QuickStart Development System Kit Contents ............................ 1 S1-3 POT ........................................................................................5 QuickStart Plus Development System Kit Contents .................... 1 S1-4 ADC3 .....................................................................................5 General Description ......................................................................... 1 S1-5 VIN− ......................................................................................5 Evaluation Board .............................................................................. 1 S1-6 VIN+ ......................................................................................5 Revision History ............................................................................... 2 S1-7 ADC4 .....................................................................................5 Getting Started with the Evaluation Hardware ............................ 3 S1-8 LED.........................................................................................5 Power Supply ................................................................................. 3 External Connectors .........................................................................6 RS-232 Interface ........................................................................... 3 Analog I/O Connector J3 .............................................................6 Emulation Interface ...................................................................... 3 Power Supply Connector J5 .........................................................6 Crystal Circuit............................................................................... 3 Emulation Connector J4...............................................................6 External Reference (ADR291) .................................................... 3 Serial Interface Connector J1.......................................................6 Reset/Download/IRQ0 Push-buttons ........................................ 3 Digital I/O Connector J2 ..............................................................6 Power Indicator/General-Purpose LEDs .................................. 4 External Memory Interface ..............................................................8 Analog I/O Connections ............................................................. 4 Connections ...................................................................................8 General-Purpose Prototype Area ............................................... 4 Potentiometer Demonstration Circuit ........................................ 10 External Memory and Latch Footprint ..................................... 4 Schematic and Artwork ................................................................. 11 DIP Switch Link Options................................................................. 5 Bill of Materials ............................................................................... 13 S1-1 VREF ........................................................................................ 5 REVISION HISTORY 2/14—Rev. A to Rev. B Reorganized Layout (from AN-744 to UG-669) ............ Universal Added Figure 1; Renumbered Sequentially and Changes to General Description Section ........................................................... 1 Change to Figure 6 ......................................................................... 12 Changes to Table 5 .......................................................................... 13 2/07—Rev. 0 to Rev. A Reorganized Layout ............................................................ Universal Added Table 4 and changes to Figure 2 ......................................... 9 Changes to Figure 4 ........................................................................ 11 Changes to Table 5 .......................................................................... 13 2004—Revision 0: Initial Version Rev. B | Page 2 of 16 EVAL-ADuC7026 User Guide UG-669 GETTING STARTED WITH THE EVALUATION HARDWARE POWER SUPPLY CRYSTAL CIRCUIT Connect the 9 V power supply via the 2.1 mm input power socket (J5). The input connector is configured as a center negative, that is, as GND on the center pin and +9 V on the outer shield. The board is fitted with a 32.768 kHz crystal, from which the on-chip PLL circuit can generate a 41.78 MHz clock. EXTERNAL REFERENCE (ADR291) The external 2.5 V Reference Chip U2 has two functions. It is provided on the evaluation board to demonstrate the external reference option of the ADuC7026, but its main purpose is to generate the VOCM voltage of the differential amplifier if required. The 9 V supply is regulated via the Linear Voltage Regulator U5. The 3.3 V regulator output is used to drive the digital side of the board directly. The 3.3 V supply is also filtered and then used to supply the analog side of the board. When on, the LED (D3) indicates that a valid 3.3 V supply is being driven from the regulator circuit. All active components are decoupled with 0.1 µF at device supply pins to ground. RESET/DOWNLOAD/IRQ0 PUSH-BUTTONS A reset push-button is provided to allow the user to reset the part manually. When the button is pushed, the reset pin of the ADuC7026 is pulled to DGND. Because the reset pin on the ADuC7026 is Schmidt triggered internally, there is no need to use an external Schmidt trigger on this pin. RS-232 INTERFACE The ADuC7026 (U1) P1.1 and P1.0 lines are connected to the RS-232 interface cable via Connector J1. The interface cable generates the required level shifting to allow direct connection to a PC serial port. Ensure that the cable supplied is connected to the board correctly, that is, DVDD is connected to DVDD and DGND is connected to DGND. When pushed, the IRQ0 push-button switch drives P0.4/IRQ0 high. This can be used to initiate an external interrupt 0. To enter serial download mode, the user must pull the P0.0/BM pin low while reset is toggled. On the evaluation board, serial download mode can easily be initiated by holding down the serial download push-button (S2) while inserting and releasing the reset button (S3) as shown in Figure 2. Nonintrusive emulation and download are possible on the ADuC7026, via JTAG, by connecting a JTAG emulator to the J4 connector. (A) S3 AND S2 RELEASED S3 (RESET = 1) S2 (BM = 1) (B) PUSH S2 S3 (RESET = 1) (D) RELEASE S3 S3 (RESET = 1) S2 (BM = 0) (C) PUSH S3 S2 (BM = 0) S3 (RESET = 0) S2 (BM = 0) (E) RELEASE S2 S3 (RESET = 1) S2 (BM = 1) Figure 2. Entering Serial Download Mode on the Evaluation Board Rev. B | Page 3 of 16 05032-001 EMULATION INTERFACE UG-669 EVAL-ADuC7026 User Guide POWER INDICATOR/GENERAL-PURPOSE LEDS A power LED (D3) is used to indicate that a sufficient supply is available on the board. A general-purpose LED (D2) is directly connected to P4.2 of the ADuC7026. When P4.2 is cleared, the LED is turned on, and when P4.2 is set, the LED is turned off. ANALOG I/O CONNECTIONS All analog I/O connections are brought out on Header J3. DAC1 can be used to control the brightness of the LED D1, when connected via the S1 switch. GENERAL-PURPOSE PROTOTYPE AREA General-purpose prototype areas are provided at the bottom of the evaluation board for adding external components as required in the user’s application. AVDD, AGND, VDDIO, and DGND tracks are provided in the prototype area. EXTERNAL MEMORY AND LATCH FOOTPRINT ADC0 and ADC1 are buffered using an AD8606 to evaluate single-ended and pseudo differential mode. A potentiometer can be connected to ADC0 (buffered). ADC3 and ADC4 can be buffered with a single-ended to differential op amp on-board, with the AD8132 used to evaluate the ADC in fully differential mode. Footprints for a 32 k × 16 static RAM (CY7C1020CV33), a 64 k × 16 flash (AT29LV1024), and a16-bit latch are also on board. See the External Memory Interface section. ADC2 and ADC5 to ADC11 are not buffered. Be sure to follow the data sheet recommendations when connecting signals to these inputs. Rev. B | Page 4 of 16 EVAL-ADuC7026 User Guide UG-669 DIP SWITCH LINK OPTIONS S1-1 VREF S1-5 VIN− Function Function Connects the output of the 2.5 V external reference (ADR291) to the VREF pin (Pin 68) of the ADuC7026. Connects the −OUT pin of the single-ended to differential op amp (AD8132) to ADC3. S1-5 and S1-6 must be used together. When VIN− is in the on position, VIN+ must also be in the on position to use the differential op amp on Channel ADC3 and Channel ADC4. Use Slide S1-1 to the on position to connect the external reference to the ADuC7026. Slide S1-1 to the off position to use the internal 2.5 V reference or a different external reference on the VREF pin of Header J3. S1-2 VOCM Use Slide S1-5 to the on position to connect −OUT of the AD8132 to ADC3. Function Slide S1-5 to the off position to use ADC3 without the AD8132. Connects 1.67 V to the VOCM pin of the AD8132. No extra dc voltage is required on the board to use the ADC in differential mode. S1-6 VIN+ Function Use Slide S1-2 to the on position to connect VOCM of the differential amplifier to the 1.67 V divided output of the ADR291 reference. Connects the +OUT pin of the single-ended to differential op amp (AD8132) to ADC4. When VIN+ is in the on position, VIN− must also be in the on position to use the differential op amp on Channel ADC3 and Channel ADC4. Use Slide S1-2 to the off position to use a different voltage for VOCM by connecting a dc voltage to the VOCM pin of Header J3. Note that the VOCM value is dependent on the reference value, as shown in Table 1. Slide S1-6 to the on position to connect +OUT of the AD8132 to ADC4. Table 1. VOCM Range S1-7 ADC4 VREF 2.5 V 2.048 V 1.25 V VOCM Minimum 1.25 V 1.024 V 0.75 V VOCM Maximum 2.05 V 2.276 V 2.55 V Slide S1-6 to the off position to use ADC4 without the AD8132. Use Slide S1-7 to the on position to connect ADC4 of Header J3 directly to the ADC4 pin (Pin 1) of the ADuC7026. S1-3 POT Slide S1-7 to the off position to disconnect ADC4 of Header J3 from the ADC4 pin (Pin 1) of the ADuC7026. Function S1-8 LED Connects the potentiometer output to ADC0. This input is buffered by an AD8606. This is for demonstration purposes. Function Use Connects the DAC1 output to the green LED of the demonstration circuit, D1. Slide S1-3 to the on position to connect the potentiometer to the op amp of the ADC0 input channel. Use Slide S1-3 to the off position to use the ADC0 input on Header J3. S1-4 ADC3 Slide S1-8 to the on position to connect the DAC1 output to D1. Slide S1-8 to the off position to use the DAC1 output on Header J3. Function Brings out ADC3 (Pin 80) on Header J3. Use Slide S1-4 to the on position to connect ADC3 of Header J3 directly to the ADC3 pin (Pin 80) of the ADuC7026. Slide S1-4 to the off position to disconnect ADC3 of Header J3 from the ADC3 pin (Pin 80) of the ADuC7026. Rev. B | Page 5 of 16 UG-669 EVAL-ADuC7026 User Guide EXTERNAL CONNECTORS ANALOG I/O CONNECTOR J3 Table 2. Pin Functions for Analog I/O Connector J3 Connector J3 provides external connections for all ADC inputs, reference inputs and DAC outputs. The pinout of the connector is shown in Table 2. Pin No. J3-1 J3-2 J3-3 J3-4 J3-5 J3-6 J3-7 J3-8 J3-9 J3-10 J3-11 J3-12 J3-13 J3-14 J3-15 J3-16 J3-17 J3-18 J3-19 J3-20 J3-21 J3-22 J3-23 J3-24 POWER SUPPLY CONNECTOR J5 Connector J5 allows for the connection between the evaluation board and the 9 V power supply provided in the ADuC7026 development system. EMULATION CONNECTOR J4 Connector J4 provides a connection of the evaluation board to the PC via a USB cable and mIDAS link provided in the ADuC7026 QuickStart Plus development system only. SERIAL INTERFACE CONNECTOR J1 Connector J1 provides a simple connection of the evaluation board to the PC via a PC serial port cable provided with the ADuC7026 development system. DIGITAL I/O CONNECTOR J2 Connector J2 provides external connections for all GPIOs. The pinout of the connector is shown in Table 3. Rev. B | Page 6 of 16 Pin Description AVDD AGND VREF DACREF ADC0 ADC1 ADC2 ADC3 ADC4 ADC5 ADC6 ADC7 ADC8 ADC9 ADC10 ADC11 VDIFF VOCM DAC0 DAC1 DAC2 DAC3 ADCNEG AGND EVAL-ADuC7026 User Guide UG-669 Table 3. Pin Functions for Digital I/O Connector J2 Pin No. J2-1 J2-2 J2-3 J2-4 J2-5 J2-6 J2-7 J2-8 J2-9 J2-10 J2-11 J2-12 J2-13 J2-14 J2-15 J2-16 J2-17 J2-18 J2-19 J2-20 J2-21 Pin Description DGND P4.5 AD13/PLAO[13] P4.4 AD12/PLAO[12] P4.3 AD/11PLAO[11] P4.2 AD10/PLAO[10] P1.0 T1/SIN/SCL0/PLAI[0] P1.1 SOUT/SDA0/PLAI[1] P1.2 RTS/SCL1/PLAI[2] P1.3 CTS/SDA1/PLAI[3] P1.4 IRQ2/RI/CLK/PLAI[4] P1.5 IRQ3/DCD/MISO/PLAI[5] P4.1 AD9/PLAO[9] P4.0 AD8/PLAO[8] P1.6 DSR/MOSI/PLAI[6] P1.7 DTR/CSL/PLAO[0] P2.2 PWM0L/RS/PLAO[7] P2.1 PWM0H/WS/PLAO[6] P2.7 PWM1L/MS3 P3.7 PWMSYNC/AD7/PLAI[15] P3.6 PWMTRIP/AD6/PLAI[14] P0.7 ECLK/XCLK/SIN/PLAO[4] Pin No. J2-22 J2-23 J2-24 J2-25 J2-26 J2-27 J2-28 J2-29 J2-30 J2-31 J2-32 J2-33 J2-34 J2-35 J2-36 J2-37 J2-38 J2-39 J2-40 J2-41 J2-42 Rev. B | Page 7 of 16 Pin Description P2.0 CONVSTART/SOUT/PLAO[5] P0.5 IRQ1/ADCBUSY/MS0/PLAO[2] P0.4 IRQ0/PWMTRIP/MS1/PLAO[1] P3.5 PWM2L/AD5/PLAI[13] P3.4 PWM2H/AD4/PLAI[12] P2.6 PWM1H/MS2 P2.5 PWM0L/MS1 P0.3 TRST/A16/ADCBUSY P2.4 PWM0H/MS0 P3.3 PWM1L/AD3/PLAI[11] P3.2 PWM1H/AD2/PLAI[10] P3.1 PWM0L/AD1/PLAI[9] P3.0 PWM0H/AD0/PLAI[8] P0.2 PWM2L/BHE P0.6 T1/MRST/AE/PLAO[3] P0.0 CMP/MS2/PLAI[7] P4.7 AD15/PLAO[15] P4.6 AD14/PLAO[14] P2.3 AE P0.1 PWM2H/BLE DGND UG-669 EVAL-ADuC7026 User Guide EXTERNAL MEMORY INTERFACE A footprint for a 32 k × 16 SRAM, a 64 k × 16 flash, and a 16-bit D-latch are provided on board because address and data are multiplexed on the external bus. The memory footprints are for a CY7C1020CV33 and AT29LV1024. The latch footprint is for a 74LVT16373AGG. Note that you can use different versions of the CY7C1020CV33 memory, with different access times. Wait states can be added in the XMxPAR register to allow for interfacing to slower memory, if required. CONNECTIONS Table 4. Connection Description Controls RS, WS, and AE are the minimum control signals of any memory interface. MS0 and MS1, memory select signals, are connected to the CE of the SRAM and the flash, respectively, to enable the memory when necessary. BHE and BLE allows the high or low byte of the 16-bit SRAM to be selected. 16 bits of address data, (AD[15:0]), are directly connected from the ADuC7026 to the memory circuitry. 16 bits of address IO[16:1] are connected from the ADuC7026 to AD[15:0] of the memory devices. AD[0] addresses a byte. To address the 32 k of the SRAM only, 14-bit addresses are required. 15-bit addresses are required for the 64 k flash. Data Addresses Rev. B | Page 8 of 16 EVAL-ADuC7026 User Guide UG-669 AD[0:15] U6 AT29LV1024 VDDIO ADR[0:15] 27 MS1 47 46 44 43 41 40 38 37 36 35 33 32 30 29 27 26 1 24 25 48 7 18 31 42 AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 R23 0Ω AE VDDIO 1D0 1D1 1D2 1D3 1D4 1D5 1D6 1D7 2D0 2D1 2D2 2D3 2D4 2D5 2D6 2D7 1OE 2OE 2LE 1LE VCC VCC VCC VCC 1Q0 1Q1 1Q2 1Q3 1Q4 1Q5 1Q6 1Q7 2Q0 2Q1 2Q2 2Q3 2Q4 2Q5 2Q6 2Q7 GND GND GND GND GND GND GND GND 2 3 5 6 8 9 11 12 13 14 16 17 19 20 22 23 4 10 15 21 28 34 39 45 ADR0 ADR1 ADR2 ADR3 ADR4 ADR5 ADR6 ADR7 ADR8 ADR9 ADR10 ADR11 ADR12 ADR13 ADR14 ADR15 2 3 4 5 6 7 9 10 11 13 14 15 17 18 19 20 ADR0 ADR1 ADR2 ADR3 ADR4 ADR5 ADR6 ADR7 ADR8 ADR9 ADR10 ADR11 ADR12 ADR13 ADR14 ADR15 CE OE A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 O0 O1 O2 O3 O4 O5 O6 O7 O8 O9 O10 O11 O12 O13 O14 O15 47 RS 46 45 44 43 42 40 39 38 36 35 34 32 31 30 29 28 AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 U8 CY7C1020CV33-12 5 4 3 2 18 44 43 42 27 26 25 24 21 20 19 ADR0 ADR1 ADR2 ADR3 ADR4 ADR5 ADR6 ADR7 ADR8 ADR9 ADR10 ADR11 ADR12 ADR13 ADR14 MS0 RS WS BHE BLE VDDIO 12 VSS 37 VSS VCC WE VDDIO A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 6 41 CE 17 OE WE 40 39 BHE BLE IO1 IO2 IO3 IO4 IO5 IO6 IO7 IO8 IO9 IO10 IO11 IO12 IO13 IO14 IO15 IO16 7 8 9 10 13 14 15 16 29 30 31 32 35 36 37 38 11 VCC 33 VCC 12 VSS 34 VSS C26 C27 C28 C29 C30 C31 0.1µF 0.1µF 0.1µF 0.1µF 0.1µF 0.1µF 0.1µF U8 DECOUPLING CAPACITORS Figure 3. External Memory Connections Rev. B | Page 9 of 16 VDDIO VDDIO C25 U7 DECOUPLING CAPACITORS AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 U6 DECOUPLING CAPACITORS 05032-002 U7 74LVT16373ADGG 23 22 WS UG-669 EVAL-ADuC7026 User Guide POTENTIOMETER DEMONSTRATION CIRCUIT AVDD AVDD Note that the internal and external reference are 2.5 V, which gives an ADC input range of 0 V to 2.5 V in single-ended mode. The potentiometer can give a voltage between 0 V and AVDD = 3.3 V. ADC DAC APPLICATION CODE Figure 4. Circuit Diagram of the RTD Circuit Rev. B | Page 10 of 16 05032-003 By using the sample code in pot.c located in the code example folder on the accompanying CD, the variation in the potentiometer resistance can be seen on the output LED. ANALOG INTERFACE J3-1 J3-2 J3-3 J3-4 J3-5 J3-6 J3-7 J3-8 J3-9 J3-10 J3-11 J3-12 J3-13 J3-14 J3-15 J3-16 J3-17 J3-18 J3-19 J3-20 J3-21 J3-22 J3-23 J3-24 AVDD AGND VREF DACREF ADC0 ADC1 ADC2 ADC3 ADC4 ADC5 ADC6 ADC7 ADC8 ADC9 ADC10 ADC11 DIFF VOCM DAC0 DAC1 DAC2 DAC3 ADCNEG AGND AVDD + J4-1 J4-2 J4-3 J4-4 J4-5 J4-6 J4-7 J4-8 J4-9 J4Z10 J4-11 J4-12 J4-13 J4-14 J4-15 J4-16 J4-17 J4-18 J4-19 J4-20 0.1µF C2 N/C N/C TDO TCK TMS TDI TRST 0.1µF C4 4 GND ADR291E U2 VDDIO TRIM R4 49.9Ω 5 R7 24.9Ω R6 R5 R19 C22 10µF + 1.5Ω AVDD 348Ω 348Ω 10µF AVDD 0.1µF 348Ω R9 AD8132 U3 8 3 +IN 5 V+ 2 –OUT VOCM+OUT V– 1 4 –IN 6 R8 348Ω C6 C5 C3 0.1µF VDDIO R11 60.4Ω R10 60.4Ω DEMO CIRCUIT CW L1 R20 270Ω VDDIO 100kΩ R21 C1 JTAG CONNECTOR + R1 100kΩ C23 10µF + 1 C8 C7 22pF AVDD GND 3 OUT U5 SD 7 IN 2 16 15 14 13 12 11 10 9 R12 270Ω AVDD DEMO CIRCUIT D1 1 2 3 4 5 6 7 8 0.1µF C24 D4 VREF VOCM POT ADC3 IN– IN+ ADC4 LED 7 S2 BLE AE AD14 AD15 0Ω R14 0Ω R13 J5–3 J5–1 J5–4 J5–2 C9 U4–C 4 8 10nF V+ V– VDDIO C10 ADC4 ADC5 ADC6 ADC7 ADC8 ADC9 ADC10 GNDREF ADCNEG DAC0 DAC1 DAC2 DAC3 TMS TDI P0.1 P2.3 P4.6 P4.7 P0.0 VDDIO 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 10nF C9 AND C10 NOT POPULATED SERIAL DOWNLOAD AD8606ARZ R15 1kΩ – + 1 R3 200Ω AD8606ARZ U4–B – + U4–A POWER SUPPLIES 6 5 2 3 100Ω R2 D2 AVDD 470nF 22pF AVDD BHE S1 SW8DIP P4.2 0.1µF C12 C11 U1 ADUC7026 AD0 AD1 AD2 AD3 MS0 10µF 6 C13 470nF R18 10µF + MS1 VOUT 270Ω P1.2 P1.3 P1.4 P1.5 P4.1 P4.0 IOVDD IOGND P1.6 P1.7 P2.2 P2.1 P2.7 P3.7 P3.6 XCLKI XCLKO P0.7 P2.0 P0.5 0.1µF C14 RESET AD6 AD7 S3 R16 1kΩ VDDIO 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 AVDD WS RS +VIN 100kΩ R24 D3 Figure 5. Evaluation Board Schematic C19 R22 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 ADC3 ADC2 ADC1 ADC0 ADC11 DACVDD AVDD AVDD AGND AGND DACGND DACREF VREF REFGND P4.5 P4.4 P4.3 P4.2 P1.0 P1.1 P0.6 TCK TDO P0.2 IOGND IOVDD LVDD DGNG P3.0 P3.1 P3.2 P3.3 P2.4 P0.3 P2.5 P2.6 RST P3.4 P3.5 P0.4 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 Rev. B | Page 11 of 16 AD4 AD5 + C15 VDDIO C20 12pF VDDIO 0.1µF C16 32.768kHz Y1 DGND VDDIO VDDIO S4 IRQ0 R17 1kΩ C21 12pF C18 P3.5 P3.4 P2.6 P2.5 P0.3 P2.4 P3.3 P3.2 P3.1 P3.0 P0.2 P0.6 P0.0 P4.7 P4.6 P2.3 P0.1 DGND J2-25 J2-26 J2-27 J2-28 J2-29 J2-30 J2-31 J2-32 J2-33 J2-34 J2-35 J2-36 J2-37 J2-38 J2-39 J2-40 J2-41 J2–42 J2–24 P0.4 P1.6 P1.7 P2.2 P2.1 P2.7 P3.7 P3.6 P0.7 P2.0 P0.5 J2-14 J2-15 J2-16 J2-17 J2-18 J2-19 J2-20 J2-21 J2-22 J2-23 P4.5 P4.4 P4.3 P4.2 P1.0 P1.1 DGND P1.2 P1.3 P1.4 P1.5 P4.1 P4.0 J2-2 J2-3 J2-4 J2-5 J2-6 J2-7 J2-1 + 10µF J2-8 J2-9 J2-10 J2-11 J2-12 J2-13 0.1µF C17 UART VDDIO J1–1 J1–2 J1–3 J1–4 U1 BYPASS CAPACITORS 10µF AD8 AD9 AD10 AD11 AD12 AD13 2 DIGITAL INTERFACE AVDD EVAL-ADuC7026 User Guide UG-669 SCHEMATIC AND ARTWORK 05032–004 EVAL-ADuC7026 User Guide 05032-005 UG-669 Figure 6. Evaluation Board Silkscreen Rev. B | Page 12 of 16 EVAL-ADuC7026 User Guide UG-669 BILL OF MATERIALS Table 5. Component ADuC7026 Evaluation Board, Revision B2 PCB Standoff U1 U2 U3 U4 U5 U6 U7 U8 Y1 S1 S2, S3, S4 D1, D2, D3 D4 C1, C5, C13, C15, C18, C22, C23 C2 to C4, C6, C12, C14, C16, C17, C24 C7, C8 C9, C10 C11, C19 C20, C21 R1 R2 R3 R4 R5, R6, R8, R9 R7 R10, R11 R12, R18, R20 R13, R14, R23 R15, R16, R17 R19 R21, R22, R24 L1 J1 J2 J3 J4 J5 Qty 1 Part PCB-1 Description 2-sided, surface-mount PCB Order No. Mfg. Analog Devices 4 1 1 1 1 1 0 0 0 1 1 3 3 1 7 Standoff ADuC7026 ADR291 AD8132 AD8606 ADP3333 AT29LV1024 74LVT16373ADGG CY7C1020CV33-12 32.768 kHz SW\8DIP Push-button switch LED PRLL4002 10 µF Stick-on mounting feet MicroConverter (80-lead LQFP) Band gap reference Differential op amp Dual op amp, (8-pin SOIC) Fixed 3.3 V linear voltage regulator 64 k × 16 flash 16-bit D-latch 32 k × 16 static RAM Watch crystal 8-way DIP switch PCB-mounted push-button switch 1.8 mm miniature LED Diode Surface-mount tantalum capacitor, Taj-B case 148-922 ADuC7026CP ADR291ER AD8132ARM AD8606AR ADP3333ARM3.3 AT29LV1024 74LVT16373ADGG CY7C1020CV33-12 971-3220 GH7242-ND 177-807 359-9954 BAV103TPMSCT-ND 197-130 Farnell Analog Devices Analog Devices Analog Devices Analog Devices Analog Devices Not populated Not populated Not populated Farnell DigiKey Farnell Farnell DigiKey Farnell 10 0.1 µF Surface-mount ceramic capacitor, 0603 case 317-287 Farnell 2 2 2 2 1 22 pF 10 nF 470 nF 12 pF 10 kΩ potentiometer 100 Ω 200 Ω 49.9 Ω 348 Ω 24.9 Ω 60.4 Ω 270 Ω 0Ω 1 kΩ 1.5 Ω 100 kΩ Ferrite bead 4-pin header 42-pin header 42-pin header 20-pin header Power socket Surface-mount ceramic capacitor, 0603 case Surface-mount ceramic capacitor, 0603 case Surface-mount ceramic capacitor, 0603 case Surface-mount ceramic capacitor, 0603 case 0.25W, 4 series, (4 mm × 4 mm square) 722-005 301-9561 318-8851 721-979 TS53YJ 10K 20% TR (lead free) 933-2375 933-2758 311-49.9HRCT-ND 311-348HRCT-ND 311-24.9HRCT-ND 311-60.4HRCT-ND 933-0917 933-1662 933-0380 9331832 933-0402 952-6862 TSM-104-02-T-SH TSM-121-01-T-DV TSM-124-01-T-SV HTST-110-01-L-DV KLD-SMT2-0202-A Farnell Farnell Farnell Farnell Vishay 1 1 1 4 1 2 3 3 3 1 3 1 1 1 1 1 1 Surface-mount resistor, 0603 case Surface-mount resistor, 0603 case Surface-mount resistor, 0805 case Surface-mount resistor, 0603 case Surface-mount resistor, 0805 case Surface-mount resistor, 0805 case Surface-mount resistor, 0603 case Surface-mount resistor, 0603 case Surface-mount resistor, 0603 case Surface-mount resistor, 0603 case Surface-mount resistor, 0603 case Surface-mount inductor, 1206 case 4-pin, 90º single-row header 42-pin, straight single-row header 24-pin, straight single-row header 20-pin, connector PCB mounted socket (2 mm pin diameter) Rev. B | Page 13 of 16 Farnell Farnell DigiKey DigiKey DigiKey DigiKey Farnell Farnell Farnell Farnell Farnell Farnell Samtec Samtec Samtec Samtec Kycon UG-669 EVAL-ADuC7026 User Guide NOTES Rev. B | Page 14 of 16 EVAL-ADuC7026 User Guide UG-669 NOTES Rev. B | Page 15 of 16 UG-669 EVAL-ADuC7026 User Guide NOTES ESD Caution ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality. Legal Terms and Conditions By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc. (“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term “Third Party” includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER’S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed. ©2004–2014 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG05032-0-2/14(B) Rev. B | Page 16 of 16