Real-Time Scheduling - II ECE 455/555 Embedded System Design Wei Gao

advertisement

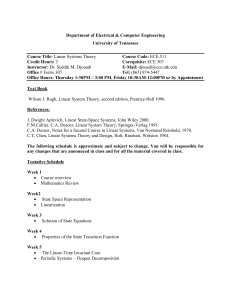

ECE 455/555

Embedded System Design

Real-Time Scheduling - II

Wei Gao

Fall 2015

1

Optimal Scheduling Algorithms

Rate Monotonic Scheduling (RMS)

Higher rate (=1/period) Higher priority

Optimal preemptive static priority scheduling algorithm

Earliest Deadline First (EDF)

Earlier absolute deadline Higher priority

Optimal preemptive dynamic priority scheduling algorithm

ECE 455/555 Embedded System Design

2

Relaxing Assumptions

Single processor.

All tasks are periodic.

Zero context switch time.

Relative deadline = period.

No priority inversion.

What if relative deadline < period?

ECE 455/555 Embedded System Design

3

Earliest Deadline First (EDF)

Earlier absolute deadline Higher

priority

Optimal preemptive dynamic priority

scheduling algorithm

CPU time demand analysis

To start, assume Di = Pi

CPU time demand in interval [0, L]

• Total execution time needed for completing all

jobs with deadlines no later than L

T1 T1 T1 T1 T1

T2

T3

L

C P (0, L) = ∑ Ci

i =1 Pi

T2

T2

T3

n

T4

• For one task: # of released jobs multiplying

execution time

• For all tasks: summation

ECE 455/555 Embedded System Design

0

L

4

Schedulable Condition

A set of periodic tasks is schedulable by

EDF if and only if for all L ≥ 0:

n

L

L ≥ ∑ Ci

i =1 Pi

Real CPU time >= demanded CPU time

There is always enough time to satisfy CPU

time demand at every time point.

When Di < Pi

L − Di

∀L ∈ D, L ≥ ∑

+ 1 Ci

Pi

i =1

T1 T1 T1 T1 T1

T2

T3

T2

T2

T3

n

T4

0

ECE 455/555 Embedded System Design

L

5

Relaxing Assumptions

Single processor.

All tasks are periodic.

Zero context switch time.

Relative deadline = period.

No priority inversion.

What if priority inversion exists?

ECE 455/555 Embedded System Design

6

Priority Inversion

A lower-priority task blocks a higher-priority task

from running.

Sources of priority inversion

Access shared resources guarded by semaphores

• Lower-priority task gets the resource first

Access non-preemptive subsystems

• Communication subsystems

• Storage

ECE 455/555 Embedded System Design

7

Priority Inversion

critical section

T1 blocked!

1

4

0

1

4

2

4

1

4

6

8

10

4

12

14

16

18

20

22

T1 tries to get the same semaphore

T4 preempted by T1

T4 acquires a semaphore

T4 starts to run

ECE 455/555 Embedded System Design

8

Unbounded Priority Inversion

critical section

T1 blocked by 4,2,3!

1

1

1

2

3

4

0

4

2

4

4

4

6

8

10

12

14

16

4

18

20

22

T1 tries to get the semaphore

ECE 455/555 Embedded System Design

9

What Happened to Mars Pathfinder?

July 4th, 1997 landing on the Mars

…But a few days into the mission, not long after Pathfinder started

gathering meteorological data, the spacecraft began

experiencing total system resets, each resulting in losses of

data…

Priority inversion

Bus management (high priority) is blocked by data gathering (low

priority) and long-running communications (medium priority)

Watchdog timer resets system after bus is blocked for some time

Real-World (Out of This World) Story:

http://research.microsoft.com/~mbj/Mars_Pathfinder/

Mars_Pathfinder.html

ECE 455/555 Embedded System Design

10

Solution: Priority Inheritance

Let the low-priority task inherit the priority of the

blocked high-priority task.

critical section

T1 only blocked by 4

1

1

1

3

2

4

0

4

2

4

4

4

6

8

10

12

14

16

18

20

22

T4 returns to priority 4 after the critical section

T1 tries to get semaphore so T4 inherits T1’s priority

ECE 455/555 Embedded System Design

11

Previous Assumptions

Single processor.

All tasks are periodic.

Zero context switch time.

Relative deadline = period. (relaxed)

No priority inversion. (relaxed)

What if we have multiple processors?

ECE 455/555 Embedded System Design

12

Multi-Processor Systems

Tight coupling among processors.

Communicate through shared memory and on-board

bus.

Scheduled by a common scheduler/OS.

Global scheduling

Partitioned scheduling

States of all processors available to each other.

ECE 455/555 Embedded System Design

13

Distributed Systems

Loose coupling among processors

Each processor has its own scheduler/OS

Costly to acquire states of other processors

Broad range of systems

Processor boards mounted on a VME bus

• VME: Versa Module European

Automobile: hundreds of processors connected through

Control Area Networks (CANs)

Air traffic control system on a wide area network

ECE 455/555 Embedded System Design

14

End-to-End Task Model

An (end-to-end) task is composed of

multiple subtasks running on multiple

processors

Message/event

Remote method invocation

Subtasks are subject to precedence

constraints

Task = a chain/tree/graph of subtasks

E.g. ship navigation

Sonar

Signal

processing

ECE 455/555 Embedded System Design

Obstacle

detection

Navigation

15

Notation

Ti = {Ti,1, Ti,2, … , Ti,n(i)}

n(i): the number of subtasks of Ti

Precedence constraint: Job Ji,j cannot be released

until Ji,j-1 is completed.

Task Ti

Sonar

Subtasks: Ti,1

Signal

processing

Obstacle

detection

Ti,2

Ti,3

ECE 455/555 Embedded System Design

Navigation

Ti,4

16

End-to-End Deadline

A task is subject to an end-to-end deadline

Response time of a particular

subtask is less important

How to meet end-to-end deadlines?

Sonar

ECE 455/555 Embedded System Design

Navigation

17

End-to-End Scheduling Framework

1.

2.

3.

4.

Task allocation

Synchronization protocol

Subdeadline assignment

Schedulability analysis

ECE 455/555 Embedded System Design

18

Summary

Priority inversion

Sources

Unbounded priority inversion

Priority inheritance protocol

Distributed real-time systems

End-to-end task model

End-to-end deadline

End-to-end scheduling framework

Task allocation

Synchronization protocol

Subdeadline assignment

Schedulability analysis

ECE 455/555 Embedded System Design

19