Recap from last class Hardware support Dynamic power management

advertisement

Recap from last class

Hardware support

CMOS power consumption and features

Clock gating

Supply shutdown

Dynamic voltage scaling

Dynamic power management

Energy conservation and performance

Adjusts power mode to adapt to workload variations

Baseline: greedy policy

Break-even time TBE

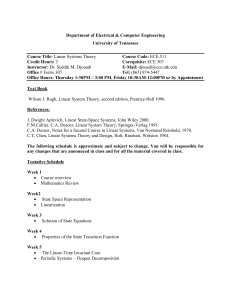

ECE 455/555 Embedded System Design

1

ECE 455/555

Embedded System Design

Power Management - II

Wei Gao

Fall 2015

2

Break-Even Time TBE

Definition

Minimum idle time required to compensate the cost of entering an

inactive state

• Cost: transition time and extra power

Enter an inactive state is beneficial only if idle time is longer

than the break-even time

Break-even time can be viewed as transition overhead

Ex. going to Hawaii is worthwhile only if vacation is long enough

Assumptions

Cannot delay workload to extend idle time

An ideal power manager (PM) knows how long the idle time is going to

be

ECE 455/555 Embedded System Design

3

Energy Saving Calculation

Given an idle period Tidle > TBE

ES(Tidle) = (Tidle - TTR)(POn - POFF) + TTR(POn – PTR)

• POn > PTR: total = idle saving + transition saving

• POn < PTR: total = idle saving - transition cost

Achievable power saving depends on workload!

Distribution of idle periods

ECE 455/555 Embedded System Design

4

Predictive Techniques

Don’t know how long the idle time will be?

Predict whether idle time Tidle > TBE based on history

Ex: someone takes break once an hour?

Predicted event: p = {Tidle > TBE}

Observed event: o

• Triggers state transition: RUN -> IDLE/SLEEP

ECE 455/555 Embedded System Design

5

Metrics of Prediction Quality

Safety: conditional probability Prob(p|o)

If an observed event happens, what’s the probability of Tidle > TBE?

Ideally, safety = 1.

Efficiency: Prob(o|p)

If Tidle > TBE, what’s the probability of successfully predicting it in

advance (e.g., o happens)?

Overprediction

State transition too much

High performance penalty poor safety

Underprediction

State transition not enough

Wastes energy poor efficiency

ECE 455/555 Embedded System Design

6

Fixed Timeout Policy

Enter inactive state when the system has been idle

for TTO sec.

o: Tidle > TTO

Wake up in response to activity

Assumption: If a system has been idle for TTO sec, it is

likely that it will continue to be idle for Tidle-TTO > TBE.

ECE 455/555 Embedded System Design

7

Selecting Best Timeout TTO

Increasing TTO improves safety, but reduces efficiency

at the same time

Safety: Pr(Tidle>TTO+TBE | Tidle > TTO)

Highly workload dependent

Karlin’s result: TTO = TBE

Energy consumption is at worst twice the energy

consumed by an ideal policy

ECE 455/555 Embedded System Design

8

Impact of Timeout Threshold

Safety and efficiency as functions

of timeout for the games workload

(break-even time is 160ms)

Power saving as a function of

timeout

ECE 455/555 Embedded System Design

9

Critiques on Fixed Timeout

Simple!

How to set timeout threshold?

Tradeoff between safety and efficiency

Works best when workload trace is available

Always waste energy before reaching the timeout

threshold

Solution: Predictive shutdown

Always incur performance penalty for wake up

Solution: Predictive wakeup

ECE 455/555 Embedded System Design

10

Possible Improvement

Predictive shutdown: shutdown immediately when

an idle period starts

Avoid wasting energy before reaching the timeout

threshold

More efficient, less safe

Predictive wakeup: wake up before the predicted idle

time expires, even if no new activity has occurred.

Avoid performance penalty for wake up

Less efficient, safer

ECE 455/555 Embedded System Design

11

Predictive Shutdown: Threshold-based

Policy

Observation: short active period tends to be followed

by a long idle period

If the preceding active period is less than a threshold,

the idle period is predicted to be longer than TBE.

Again, what is the right threshold?

Highly workload dependent

Require offline analysis

ECE 455/555 Embedded System Design

12

Critiques: History-based Predictors

Applicability and performance depend on short-term

correlation between past & future events

True in many workloads

Predictor fails when correlation is weak

Workload in many embedded systems are more

predictable than PCs

Periodic tasks

Workload known a priori

Specialized application

ECE 455/555 Embedded System Design

13

More

Stochastic control: based on statistical models (e.g.,

Markov chain)

Read this required paper

L. Benini, A. Bogliolo and G. De Micheli, "A Survey of

Design Techniques for System-Level Dynamic Power

Management,” IEEE Transactions on VLSI, pp. 299-316,

June 2000.

ECE 455/555 Embedded System Design

14

Outline

Hardware support

Power management policy

Power manager

Holistic approach

ECE 455/555 Embedded System Design

15

Power Manager

Power manager is usually implemented in software

(OS) for flexibility

Hardware and software co-design

Software implements policy

Hardware implements power change mechanisms

Need standard interfaces to deal with hardware

diversity

Different vendors

Different devices: processor, sensor, controller …

ECE 455/555 Embedded System Design

16

Advanced Configuration and Power

Interface (ACPI)

Open standard for power management services.

Proposed by Intel, Microsoft and Toshiba

applications

device

drivers

OS kernel

ACPI Driver

Hardware platform

devices, processor, chipset

power

management

ACPI drivers

1. Kernel requests

ACPI commands

2. ACPI messages

Kernel interrupts

ECE 455/555 Embedded System Design

17

ACPI System States

System components

Min Power

Global sleep states

High wake-up

latency

Global states

Processor states

Mechanical

off

Low latency

context loss

Soft off

OS reboot

Context loss

for CPU/cache

Sleeping

Low latency

No context loss

Device states

Working

Max Power

Used as contracts between hardware and OS vendors

ECE 455/555 Embedded System Design

18

ACPI Global Power States

G3: mechanical off – no power consumption

G2: soft off – restore requires full OS reboot

G1: sleeping state

S1: low wake-up latency with no loss of context

S2: low latency with loss of CPU/cache state

S3: low latency with loss of all state except memory

S4: lowest-power state with all devices off

G0: working state

ECE 455/555 Embedded System Design

19

Outline

Hardware support

Power management policy

Power manager

Holistic approach

ECE 455/555 Embedded System Design

20

Holistic View of Power Consumption

Instruction execution (CPU)

Cache (instruction, data)

Main memory

Other: non-volatile memory, display, network

interface, I/O devices

ECE 455/555 Embedded System Design

21

Sources of Energy Consumption

Relative energy per operation

Relative energy per operation (Catthoor et al):

33

30

20

20

9

10

1

3.6

4.4

0

16-bit

add

16-bit 8x128x16 8x128x16 External

multiply

SRAM

SRAM

I/O

read

write

access

16-bit

memory

transfer

Memory transfer is the most expensive operation

Biggest energy optimization comes from properly organizing memory

Energy consumption: memory > caches > registers

ECE 455/555 Embedded System Design

22

Memory Power Optimization

Memory controllers put idle memory modules into

low-power mode

Minimize the number of active memory modules

Data placement

• Allocate new memory pages only to active memory modules

Memory address mapping

• Map consecutive memory address to a single controller

Memory compression

• Compress data in multiple memory modules to one module

ECE 455/555 Embedded System Design

23

Cache Behavior

Cache behavior is important

Energy consumption has a sweet spot as cache size

changes:

cache too small: program thrashes, burning energy on

external memory accesses;

cache too large: cache itself burns too much power.

ECE 455/555 Embedded System Design

24

Optimization for Power

Reduce memory footprint

Reduce code size

Find correct cache size

Analyze cache behavior (size of working set)

Minimize memory and cache access

Use registers efficiently less cache access

Identify and eliminate cache conflicts less memory

access

Better performance More idle time More

power saving by power management

ECE 455/555 Embedded System Design

25

Summary

Dynamic power management policy

Workload-independent metrics for energy saving calculation

Predictive techniques

• Fixed timeout policy

• Predictive shutdown and wakeup

Power manager

Advanced Configuration and Power Interface (ACPI)

Holistic approach

Memory system

Cache behavior

ECE 455/555 Embedded System Design

26

Reading

Textbook: 3.7, 6.9

Required: Sections I, II, III.A, III.B, IV of

L. Benini, A. Bogliolo and G. De Micheli, "A Survey of

Design Techniques for System-Level Dynamic Power

Management,” IEEE Transactions on VLSI, pp. 299316, June 2000.

ECE 455/555 Embedded System Design

27