Midterm Review ECE 455/555 Embedded System Design Wei Gao

advertisement

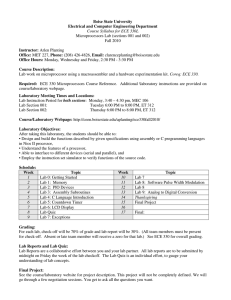

ECE 455/555

Embedded System Design

Midterm Review

Wei Gao

Fall 2015

1

Midterm Exam

When: next Monday (10/19) 5:30-7:30pm

Where: Min Kao 406

15% of your final grade

What about: Everything from the beginning of class

Closed-book, closed-notes, no laptop, no discussion

All included in class slides (as well as textbook, assigned

papers)

May have 1 or 2 programming questions

Make your answers short to include only key points

Sample questions posted on course website

ECE 455/555 Embedded System Design

2

Definition

Embedded system: any device that includes a

computer but is not itself a general-purpose

computer.

Application specific

The design is specialized and optimized for specific

application

Don’t need all the general-purpose bells and whistles

ECE 455/555 Embedded System Design

3

System Characteristics

Non-functional requirements

Real-time

Low power

Small memory footprint

Low cost

Short development cycles

Small teams

ECE 455/555 Embedded System Design

4

Real-Time

Hard real time: violating timing constraints causes

failure

Anti-lock Brake System

CD burner

Software modem

Soft real time: missing deadline results in degraded

performance

Online video

GPS map

Audio (MP3 player)?

ECE 455/555 Embedded System Design

5

Alternative Technology

Application-Specific Integrated Circuits (ASICs)

Microprocessors

Field-Programmable Gate Arrays (FPGAs)

Why should we use microprocessors?

ECE 455/555 Embedded System Design

6

ASIC

Ex: Digital baseband processing for cell phones

Pros

Performance: Fast!

Power: Fewer logic elements lead to low power

Cons

Development cost: Very high

• 2 million $ for starting production of a new ASIC

• Needs a long time and a large team

Reprogrammability: None!

• Single-purpose devices

• Difficult to upgrade systems

ECE 455/555 Embedded System Design

7

Microprocessors

Performance

Con: Programmable architecture is fundamentally slow!

• Fetch, decode instructions

Pro: Highly optimized architecture and manufacturing

• Pipelines; cache; clock frequency; circuit density; manufacturing

technology

Power

Processors perform poorly in terms of performance/watt!

Power management can alleviate the power problem.

Flexibility, development cost and time

Let software do the work!

ECE 455/555 Embedded System Design

8

FPGA

Programmable hardware

In the middle of ASIC and microprocessor

Power

• Hardware implementation: better performance/watt than

microprocessor

• Many overhead transistors: waste more power than ASIC

Reprogrammability

• Reprogammable: lower development cost than ASIC

• More difficult to program than microprocessor

More commonly used for prototyping

ECE 455/555 Embedded System Design

9

State of the Practice

Microprocessor is the dominant player

Reprogrammability and low development cost >> low

performance/watt

Optimization and power management have significantly

improved microprocessors’ performance

Microprocessor + ASIC is common

Ex: cell phone

FPGA is expected to improve

ECE 455/555 Embedded System Design

10

Design Challenges

Non-functional constraints

How do we meet deadlines?

• Faster hardware or better software?

How do we minimize power?

• Turn off unnecessary logic? Reduce memory accesses? Slow down

CPU?

Cost considerations

Trade-offs among constraints

Optimization & analysis are important!

ECE 455/555 Embedded System Design

11

Design Methodologies

requirements

specification

Top-down design

architecture

component

design

Bottom-up design

system

integration

ECE 455/555 Embedded System Design

12

GPS Map Requirement Form

name

purpose

inputs

outputs

functions

performance

manufacturing cost

power

physical size/weight

GPS moving map

consumer-grade

moving map for driving

power button, two

control buttons

back-lit LCD 400 X 600

5-receiver GPS; three

resolutions; displays

current lat/lon

updates screen within

0.25 sec of movement

$100 cost-of-goodssold

100 mW

no more than 2: X 6:,

12 oz.

ECE 455/555 Embedded System Design

13

Microprocessors

von Neumann

Same memory holds data, instructions.

A single set of address/data buses between CPU and

memory

Harvard

Separate memories for data and instructions.

Two sets of address/data buses between CPU and memory

ECE 455/555 Embedded System Design

14

von Neumann vs. Harvard

Harvard allows two simultaneous memory fetches.

Harvard architectures are widely used because

Most DSPs use Harvard for streaming data

The separation of program and data memories

• Greater memory bandwidth

• Higher performance for digital signal processing

Speed is gained at the expense of more complex electrical

circuitry.

Other examples: On chip cache of CPUs is divided

into an instruction cache and a data cache

ECE 455/555 Embedded System Design

15

RISC vs. CISC

Reduced Instruction Set Computer (RISC)

Compact, uniform instructions: facilitate pipelining

More lines of code: poor memory footprint

Allow effective compiler optimization

Complex Instruction Set Computer (CISC)

Many addressing modes and instructions;

High code density.

Often require manual optimization of assembly code for

embedded systems.

ECE 455/555 Embedded System Design

16

Busy-Wait I/O Programming

Simplest way to program I/O devices.

Devices are usually slower than CPU and require more cycles

CPU has to wait for device to finish before starting next one

Use peek instruction to test when device is finished

//send a string to device using Busy-Wait handshaking

current_char = mystring;

while (*current_char != ‘\0’) {

//send character to device (data register)

poke(OUT_CHAR,*current_char);

//wait for device to finish by checking its status

while (peek(OUT_STATUS) != 0);

//advance character pointer to next one

current_char++;

}

ECE 455/555 Embedded System Design

17

Interrupt-based I/O

Busy-wait is very inefficient.

CPU can’t do other work while testing device.

Hard to do simultaneous I/O.

Interrupts allow to change the flow of control in the CPU.

Call interrupt handler (i.e. device driver) to handle device.

CPU

PC

IR

interrupt request

interrupt ack

data/address

status

register

Device

mechanism

data

register

ECE 455/555 Embedded System Design

18

Generic Interrupt Mechanism

continue executing

next instruction

ignore

N

interrupt?

Y

N interrupt priority >

current priority?

Y

ack

bus error

Y

timeout?

N

Y

vector?

Y

call table[vector]

ECE 455/555 Embedded System Design

19

Microprocessor Bus

Bus is a set of wires and a protocol for the CPU to

communicate with memory and devices

Five major components to support reads and writes

Device 2

Device 1

a

CPU

n

Clock

R/W’

Address

Data ready’

Data

Memory

ECE 455/555 Embedded System Design

20

Typical Bus Access

Timing diagram syntax:

Constant value (0/1), stable, changing, unknown.

Clock

R/W’

Address

enable

Address

Data

Ready

data

read

ECE 455/555 Embedded System Design

write

time

21

Memory System and Caches

Memory is slower than CPU

CPU clock rates increase faster than memory

Caches are used to speed up memory

Cache is a small but fast memory that holds copies of the

contents of main memory

More expensive than main memory, but faster

Memory Management Units (MMU)

Memory size is not large enough for all application?

Provide a larger virtual memory than physical memory

ECE 455/555 Embedded System Design

22

Cache Organizations

How should we map memory to cache?

Fully-associative: any memory location can be stored

anywhere in the cache.

• Ideal, best cache hit rate but implementation is complex and slow

• Almost never implemented

Direct-mapped: each memory location maps onto exactly

one cache entry.

• Simplest, fastest but least flexible

• Easy to have conflicts

N-way set-associative: each memory location can go into

one of n sets.

• Compromised solution

ECE 455/555 Embedded System Design

23

Memory Management Unit

Memory size is not large enough for all applications?

Memory management unit (MMU)

Provides a larger virtual memory than physical memory

Translates logical addresses to physical addresses

logical

address

CPU

memory

management

unit

physical

address

ECE 455/555 Embedded System Design

main

memory

24

Memory Devices

Types of memory devices

RAM (Random-Access Memory)

• Address can be read in any order, unlike magnetic disk/tape

• Usually used for data storage

• DRAM vs. SRAM.

ROM (Read-Only Memory)

• Usually used or program storage

• Mask-programmed vs. field-programmable.

ECE 455/555 Embedded System Design

25

RAM (Random-Access Memory)

SRAM (Static RAM)

Faster, usually used for caches

Easier to integrate with logic.

Higher power consumption.

DRAM (Dynamic RAM)

Structurally simpler

• Only 1 transistor and 1 capacitor are required per bit, compared

with 6 transistors used in SRAM

Can reach very high density

Must be periodically refreshed

ECE 455/555 Embedded System Design

26

Typical I/O Devices

Timers and counters

Watchdog timer

Keyboards

Touchscreens

ECE 455/555 Embedded System Design

27

Embedded Computing Platform

Components that we have learned

Microprocessors, caches, memory, CPU bus, I/O devices,

interrupt mechanism

How to put them all together?

As an embedded computing platform

Architectures and components:

• Hardware

• Software

Debugging and testing.

ECE 455/555 Embedded System Design

28

Development and Debugging of

Embedded Systems

Development Environments

Use a host system to prepare software for target system:

Host should (1) load programs to the target; (2) start and

stop program execution on the target; and (3) debug the

program

CPU

host system

target

system

serial line

ECE 455/555 Embedded System Design

29

Hardware and Software Architectures

Hardware and software are intimately related:

Software doesn’t run without hardware;

How much hardware you need is determined by the

software requirements:

Speed;

Memory.

Special-purpose hardware often consumes much less

power.

ECE 455/555 Embedded System Design

30

C Implementation of State Machine

while (TRUE) {

switch (state) {

r==0/out2=1

case A: if (in1==1)

in1==1/x=a

A

B

{ x = a; state = B; }

else { x = b; state = D; }

r==1/out1=0

break;

in1==0/x=b

case B: if (r==0)

{ out2 = 1; state = B; }

else { out1 = 0; state = C; }

break;

case C: if (s==0)

{ out1 = 0; state = C; }

C

D

s==1/out1=1

else { out1 = 1; state = D; }

break;

s==0/out1=0

}

ECE 455/555 Embedded System Design

31

Debugging Embedded Systems

Challenges:

Target system may be hard to observe;

• e.g., only three LEDs on the motes

Target may be hard to control;

• e.g., packets may get lost in wireless communication

May be hard to generate realistic inputs;

• e.g., fire event, plume, etc

• Need to emulate the events from host systems by injecting packets

Setup sequence may be complex.

• e.g., need additional tools and environment

ECE 455/555 Embedded System Design

32

TinyOS System

Support concurrency: event-driven architecture

Modularity: application = scheduler + graph of components

Compiled into one executable

Efficiency: Get done quickly and sleep

Event/command = function calls

Fewer context switches: FIFO/non-preemptable scheduling

No kernel/application boundary: completely open-source

Main (includes Scheduler)

Application (User Components)

Actuating

Sensing

Communication

Communication

Hardware Abstractions

Modified from D. Culler et. Al., TinyOS boot camp presentation, Feb 2001

ECE 455/555 Embedded System Design

33

TinyOS Programming Model: nesC

Component model

An application consists of

Application

Component

D

wired components

Component

A

Application = graph of

components

Components are wired

through interfaces

Wiring specified by

configurations

configuration

Configuration can be

hierarchical

Component

C

Component

B

Component

F

Component

E

ECE 455/555 Embedded System Design

configuration

34

TinyOS Programming Model: nesC

Interface: events vs. commands

command needs to implemented by components

providing the interface

event needs to be handled by components using the

interface

Interface Receive

{

event message_t * Receive(message_t * msg, void * payload, uint8_t len);

command void * getPayload(message_t * msg, uint8_t * len);

command uint8_t payloadLength(message_t * msg);

}

ECE 455/555 Embedded System Design

35

Components Wiring

ECE 455/555 Embedded System Design

36

Android System Architecture

Middleware

ECE 455/555 Embedded System Design

37

Middleware

Software above the OS

Provides services to (user) software applications

beyond those available from the OS

Advantages of middleware

Separate less important functionalities out from OS kernel

• “micro”-kernel

Easier for developers to perform communication and I/O

• Better APIs

• More efficient resource management

• Easy debugging

ECE 455/555 Embedded System Design

38

Android Application Components

Activity: visual user interface

Service: runs in the background for an indefinite

period of time

Content provider

Makes a specific set of the application's data available to

other applications

Broadcast receivers:

System-wide event notification

• Screen turned on, radio on/off, battery low, etc.

ECE 455/555 Embedded System Design

39