Course Project Course project teams are formed Next milestone

advertisement

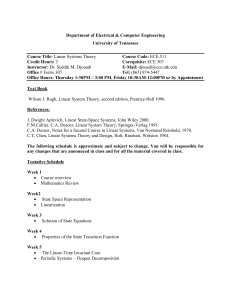

Course Project Course project teams are formed http://web.eecs.utk.edu/~weigao/ece351/spring2016/proj ect_team.html Next milestone Project proposal presentation 2/11 Thursday Submit your 1-page proposal document by 2/11 before class Submit your presentation slide by 2/11 before class Lab 1 is due next Tuesday 2/9 Let the TA check off your work at lab ECE 351 Digital Systems Design 1 Recap of last class VHDL operators Logic operators Numerical operators: mod rem Relational operators Shift operators: logical, arithmetic, rotate Concatenation operator Assignment operator Signal assignment Delayed assignments: inertial vs. transport delay ECE 351 Digital Systems Design 2 ECE 351 Digital Systems Design Structural VHDL Design - 1 Wei Gao Spring 2016 3 VHDL Design Methodology We can specify the functionality in an architecture in two ways Structural design: text based schematic, manual instantiation of another system • Re-presentation of the system architecture • Consists of components, signals, ports, etc • Wiring via signal assignments • Suitable for describing combinatorial logic Behavioral design: abstract description of functionality • Procedural description of system functionality • Consists of processes, structural system statements • Suitable for describing sequential logic ECE 351 Digital Systems Design 4 VHDL Components Functional blocks that already exist and are included into a higher level design “function calls” at the hardware level We need to know the entity declaration of the system we are calling We “declare” a component using the keyword “component” We declare the component in the architecture which indicates we wish to use it ECE 351 Digital Systems Design 5 Component Syntax component component-name port (signal-name : mode signal-type; signal-name : mode signal-type); end component; Exactly the same as the Entity declaration without the keyword is Let’s build this as a start… ECE 351 Digital Systems Design 6 Component Example Use these pre-existing entities "xor2" & "or2" entity xor2 is port (In1, In2 : in Out1 : out end entity xor2; entity or2 is Port mode port (In1, In2 : in Out1 : out STD_LOGIC; STD_LOGIC); Signal type STD_LOGIC; STD_LOGIC); end entity or2; ECE 351 Digital Systems Design 7 Component Declarations Now include the pre-existing entities "xor2" & "or2" into our "TOP" design entity TOP is port (A,B,C X end entity TOP; : in : out STD_LOGIC; STD_LOGIC); architecture TOP_arch of TOP is component xor2 port (In1, In2 : in STD_LOGIC; Out1 : out STD_LOGIC); end component; The port declarations should match component or2 port (In1, In2 : in STD_LOGIC; Out1 : out STD_LOGIC); end component; begin -- declaration of xor2 component -- declaration of or2 component ….. ECE 351 Digital Systems Design 8 Component Wiring Signals We want to interconnect components within an architecture, we need "signals" to do this Define signals within an architecture Internal "Signal" External “ports” Internal "Components" ECE 351 Digital Systems Design 9 Signal Syntax architecture TOP_arch of TOP is signal signal-name : signal-type; signal signal-name : signal-type; The signal declaration also needs to be included into the architecture ECE 351 Digital Systems Design 10 Signal Declaration architecture TOP_arch of TOP is signal node1 : STD_LOGIC; component xor2 port (In1, In2 : in Out1 : out end component; component or2 port (In1, In2 : in Out1 : out end component; begin How signals are connected to components?? STD_LOGIC; STD_LOGIC); STD_LOGIC; STD_LOGIC); -- declaration of xor2 component -- declaration of or2 component ….. node1 end architecture TOP_arch; ECE 351 Digital Systems Design 11 Component Instantiation After the "begin" keyword, we can start adding components and connecting signals We add components with "Component Instantiation“ Syntax label : component-name port map (port => signal, ……) ; label: a unique reference designator for that component component-name: same as being declared the signals with in the ( ) of the port map define how signals are connected to the ports of the instantiated component • Component instantiation = connecting signals to the component ports ECE 351 Digital Systems Design 12 Port Map There are two ways describe the "port map" of a component Positional Explicit Positional port map Signals are listed in the exact order as the components port order • ex) U1 : xor2 port map (A, B, node1); • The declaration of xor2 component specifies port In1, In2, Out1 Explicit port map Signals are explicitly linked to the port names using the "=>" notation (Port => Signal, Port => Signal, ….) • ex) U1 : xor2 port map (In1 => A, In2 => B, Out1 => node1); • Arbitrary order between signals and ports are allowed ECE 351 Digital Systems Design 13 Execution All components are executed CONCURRENTLY This mimics real hardware This is different from traditional program execution (i.e., C/C++) which is executed sequentially Because we are NOT writing code, we are describing hardware!!! ECE 351 Digital Systems Design 14 Let's put everything together architecture TOP_arch of TOP is signal node1 : STD_LOGIC; Internal signal U1 node1 component xor2 port (In1, In2 : in STD_LOGIC; Out1 : out STD_LOGIC); end component; component or2 port (In1, In2 : in Out1 : out end component; begin U2 STD_LOGIC; STD_LOGIC); U1 : xor2 port map (In1=>A, In2=>B, Out1=>node1); U2 : or2 port map (In1=>C, In2=>node1, Out1=>X); Component instantiation end architecture TOP_arch; ECE 351 Digital Systems Design 15 Generate Statement There are times when we want to instantiate a large number of the same component (ex. on a bus) VHDL has a "generate" statement that allows us to instantiate multiple components using a loop structure Syntax: label : for identifier in range generate component instantiation end generate; ECE 351 Digital Systems Design 16 Generate Statement Example: instantiate 8 inverters assuming X and Y are busses of equal width X, Y: bit vector begin Gen1 : for i in 1 to 8 generate U1 : INV1 port map ( In1=>X(i), Out1=>Y(i) ); end generate; ECE 351 Digital Systems Design 17 Concurrency The way that our designs are simulated is important in modeling real hardware behavior Components are executed concurrently (i.e., at the same time) Hard to be simulated VHDL gives us another method to describe concurrent logic behavior -> concurrent signal assignment Statement is executed by simulator whenever signals on right-hand-side change ECE 351 Digital Systems Design 18 Concurrent Signal Assignment (CSA) Another way of specifying architecture functionality besides using components architecture TOP_arch of TOP is signal node1 U1 : STD_LOGIC; node1 component xor2 port (In1, In2 : in STD_LOGIC; Out1 : out STD_LOGIC); end component; begin U2 U1 : xor2 port map (In1=>A, In2=>B, Out1=>node1); X <= node1 or C; end architecture TOP_arch; ECE 351 Digital Systems Design 19 Concurrent Signal Assignment Timing issues need to be considered When does C get to the OR gate relative to (A ⊕ B)? Could this cause a glitch on X? What about a delay in the actual value? node1 Solutions Ensure that all input signals change values synchronously Only assign the signal in certain circumstances ECE 351 Digital Systems Design 20 Delayed Signal Assignment sigout <= andout1 or andout2 after 5 ns; Output events are created based on input events This execution may schedule an event on the left-handside signal (even at a later time if specified) ECE 351 Digital Systems Design 21 Conditional Signal Assignments We can include conditional situations in a concurrent assignment Example X <= '1' when A='0' else '0'; Y <= '0' when A='0' and C='0' else '1'; X <= A when Sel='0' else B; Assign signals to other signals X and Y are evaluated concurrently Make sure to include every possible input condition, or else you haven't described the full operation of the circuit. ECE 351 Digital Systems Design 22 Selected Signal Assignment We can also use a technique that allows the listing of "choices" and "assignments” Still concurrently assigned Syntax: with expression select signal-name <= signal-value when choices, signal-value when choices, : signal-value when others; ECE 351 Digital Systems Design 23 Selected Signal Assignment Example: Describe the following Truth Table using Selected Signal Assignments: Input 000 001 010 011 100 101 110 111 X 0 1 1 0 1 1 0 0 Begin with Input select X<= '0' when "000", '1' when "001", '1' when "010", '0' when "011", '1' when "100", '1' when "101", '0' when "110", '0' when "111"; ECE 351 Digital Systems Design 24 Selected Signal Assignment We can shorten the description by using "others" for the 0's Using "|" delimited choices Input 000 001 010 011 100 101 110 111 X 0 1 1 0 1 1 0 0 Begin with Input select X<= '1' when "001" | "010" | "100" | "101", '0' when others; ECE 351 Digital Systems Design 25 Summary VHDL design methodology Structural vs. behavioral design Structural design: components Declaration syntax Component instantiation Generate statement Ensuring concurrency Concurrent signal assignment (CSA) • Conditional/delayed signal assignment • Selected signal assignment ECE 351 Digital Systems Design 26 Reading Textbook Section 5.1-5.3 ECE 351 Digital Systems Design 27