ADRF6720-EVALZ User Guide UG-689

advertisement

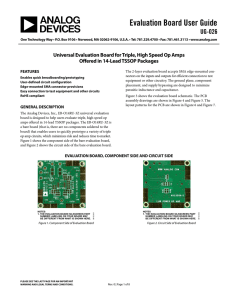

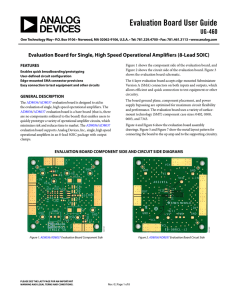

ADRF6720-EVALZ User Guide UG-689 One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com Evaluating the ADRF6720, a Wideband Quadrature Modulator with Integrated Fractional-N PLL and VCOs FEATURES phase-locked loop (PLL), and four low phase noise multicore voltage controlled oscillators (VCOs). Full-featured evaluation board for the ADRF6720 On-board USB for SPI control 3.3 V operation C# software interface for serial port control The ADRF6720 LO signal can be generated internally via the on-chip integer-N and fractional-N synthesizers, or externally via a high frequency, low phase noise LO signal. The internal integrated synthesizer enables LO coverage from 356.25 MHz to 2855 MHz using the multi-core VCOs. In the case of internal LO generation or external LO input, quadrature signals are generated with a divide-by-2 phase splitter. When the ADRF6720 is operated with an external 1 × LO input, a polyphase filter generates the quadrature inputs to the mixer. EVALUATION KIT CONTENTS ADRF6720 evaluation board USB cable EQUIPMENT NEEDED Analog signal sources and signal analyzer Power supplies (5 V/1 A) PC running Windows® 98 , Windows 2000, Windows ME, Windows XP, Windows Vista, or Windows 7 USB 2.0 port, recommended (USB 1.1 compatible) The ADRF6720 offers digital programmability for carrier feedthrough optimization, sideband suppression, HD3/IP3 optimization, and high-side or low-side LO injection. The ADRF6720 is fabricated using an advanced silicongermanium BiCMOS process. It is available in a 40 pin, RoHScompliant, 6 mm × 6 mm LFCSP package with an exposed paddle. This user guide describes the evaluation board for the ADRF6720, which provides all of the support circuitry required to operate the ADRF6720 in its various configurations and the application software used to interface with the device. SOFTWARE NEEDED ADRF6720 control software GENERAL DESCRIPTION The ADRF6720 is a wideband quadrature modulator with an integrated synthesizer ideally suited for 3G and 4G communication systems. The ADRF6720 consists of a high linearity broadband modulator, an integrated fractional-N The ADRF6720 data sheet, which provides additional information, should be consulted when working with this evaluation board. TYPICAL SETUP VPOS 40 I+ 3 I– 4 30 35 26 22 17 6 11 V2I LO NULLING DAC 27 ENOP 24 RFOUT 18 LOOUT+ ADRF6720 PHASE CORRECTION PHASE CORRECTION Q– LO NULLING DAC 8 V2I 9 LOCK_DET VPTAT 0° 90° POLYPHASE FILTER ÷1,÷2,÷4 ÷8 ÷4 PFD ÷2 REFIN 39 N = INT+ FRAC MOD SERIAL PORT INTERFACE LOOUT– 15 13 CSB SCLK SDIO LDO 2.5 V 31 DECL3 28 DECL2 7 10 16 20 23 25 29 37 38 36 CP GND Figure 1. Rev. 0 | Page 1 of 12 32 33 34 LOIN + LOIN– 5 12 DECL1 LDO VCO CHARGE PUMP VTUNE 2 14 ÷2 ×1 ×2 NIC 21 PLEASE SEE THE LAST PAGE FOR AN IMPORTANT WARNING AND LEGAL TERMS AND CONDITIONS. 19 ÷2 MUXOUT 1 12299-001 Q+ UG-689 ADRF6720-EVALZ User Guide TABLE OF CONTENTS Features .............................................................................................. 1 Baseband Inputs ............................................................................3 Evaluation Kit Contents ................................................................... 1 LO Input/Output ...........................................................................3 Equipment Needed ........................................................................... 1 RF (Modulator) Output ................................................................3 Software Needed ............................................................................... 1 Evaluation Board Control Software ................................................4 General Description ......................................................................... 1 Installing Evaluation Software and the Driver ..........................4 Typical Setup ..................................................................................... 1 Using ADRF6720 Evaluation Software ......................................4 Revision History ............................................................................... 2 Schematics and Artwork ..................................................................7 Evaluation Board Hardware ............................................................ 3 Ordering Information .................................................................... 10 Introduction .................................................................................. 3 Bill of Materials ........................................................................... 10 Power Supply ................................................................................. 3 REVISION HISTORY 5/14—Revision 0: Initial Version Rev. 0 | Page 2 of 12 ADRF6720-EVALZ User Guide UG-689 EVALUATION BOARD HARDWARE routed off chip to the SMA connector labeled LO_OUT+ and LO_OUT−. INTRODUCTION The ADRF6720 evaluation board provides all of the support circuitry required to operate the ADRF6720 in its various modes and configurations. Figure 2 shows the typical bench setup used to evaluate the performance of the ADRF6720. For internal LO configuration using the on-chip fractional-N synthesizer, apply a low phase noise reference signal to the REFIN connector. The PLL reference input can support a wide frequency range since the divide or multiplication blocks can be used to increase or decrease the reference frequency to the desired value before it is passed to the phase frequency detector (PFD). The integrated synthesizer enables continuous LO coverage from 356.25 MHz to 2855 MHz. POWER SUPPLY The ADRF6720 evaluation board requires a 3.3 V power supply. Connect the 3.3 V power terminals as like Figure 2. BASEBAND INPUTS For optimum performance using an external LO source, drive the LO inputs LOIN and LOIP differentially. The ADRF6720 evaluation board integrates footprints for both the Mini-Circuits TC1-1-43A+ balun and the Johanson 2500BL14M050T to satisfy the wide input frequency range of the external LO inputs. Unless an ac-coupled balun/transformer is used to generate the differential LO, the inputs must be ac-coupled. The input impedance of the differential LO signals is 50 Ω. Drive the baseband inputs (I+, I−, Q+, and Q−) from a differential source. Place a shunt 125 Ω external resistor across the I and Q inputs to match the differential 100 Ω impedance interface. The nominal drive level used in the evaluation of the ADRF6720 is 1 V p-p differential (or 500 mV p-p on each pin). All the baseband inputs must be externally dc biased at 0.5 V. LO INPUT/OUTPUT The ADRF6720 offers two alternatives for generating the differential LO input signal: externally via a high frequency low phase noise LO signal or internally via the on-chip fractional-N synthesizer. In either case, the differential LO signal can be RF (MODULATOR) OUTPUT The RF output is available at the RF_OUT SMA connector, which can drive a 50 Ω load. DIFFERENTIAL LO INPUT FOR EXTERNAL LO PLL REF INPUT FOR INTERNAL LO AMP OUTPUT I+ I– PLL REF INPUT RF OUTPUT Q– DAC OR BB GENERATOR Q+ 3.3V PWR GND USB PC CONTROL DIFFERENTIAL LO OUTPUT Figure 2. ADRF6720 Typical Measurement Setup Rev. 0 | Page 3 of 12 12299-002 BASEBAND INPUTS UG-689 ADRF6720-EVALZ User Guide EVALUATION BOARD CONTROL SOFTWARE The ADRF6720 evaluation board is configured with a USB friendly interface to allow programmability of the ADRF6720 registers. INSTALLING EVALUATION SOFTWARE AND THE DRIVER The following instructions describe how to install the ADRF6720 control software, as well as the Cypress Generic USB driver, onto a Windows computer running either a 32 or 64-bit operating system. Install the necessary software before plugging the USB cable to the computer. (The following instructions are specific for Windows XP, Windows Vista, and Windows 7. However, the software is compatible with Windows 98, Windows 2000, and Windows ME.) 1. 2. 3. 4. 5. Extract the ADRF6720_Control_SW_Rev0_0_3.zip file. Next, run the file ADRF6720_Rev0_0_3_install.exe from the extracted .zip file. An icon should appear on your desktop with the Analog Devices, Inc., logo, titled ADRF6720_Rev0_0_3. Once the installer is finished, install the USB driver. Plug the RFG USB adapter into the PC using a USB cable. In Windows XP, right click My Computer and select Properties > Device Manager. Then select the Hardware tab and Device Manager. In Windows Vista, right click My Computer and select Device Manager. In Windows 7, select Device Manager. In Device Manager, select the last category, Universal Serial Bus Controllers. There will be an entry that either has a yellow flag on it (for unknown device) or is labeled ADF4xxx USB Driver (if you have installed the previous ADRF6x0x or Analog Devices, Inc., Limerick PLL software). Right click this device and select update driver. Browse to select the directory where you unzip. Click Next to complete the driver installation successfully. In Windows 7, install the USB signed driver. Run ADI_RFG_Drivers_Win7.exe in the attached zip file. Windows 7 will then recognize the CyUSB driver as a signed driver. USING ADRF6720 EVALUATION SOFTWARE The ADRF6720 evaluation software offers a block diagram view of how the registers affect the major functional blocks of the ADRF6720. The main screen of the evaluation software is shown in Figure 3. Table 1 shows the functionality of the software main screen. Before reading or writing to the registers, validate the USB connection by reading the USB indicators at the lower left corner of the software. The DUT to GUI button reads the register values from the device and updates the user interface. An automatic write to the chip is initiated every time a register value is changed from the user interface. The PLL synthesizer blocks have some behind the scenes calculations where the user only needs to specify the PLL reference and desired LO frequency and the software calculates and sets the INT, FRAC, and MOD values accordingly. The green boxes require user input while the yellow boxes are read only. The Engineering tab as shown in Figure 4 allows specific reads and writes to the individual registers. The address and data fields must be input in decimal format. Rev. 0 | Page 4 of 12 ADRF6720-EVALZ User Guide UG-689 A I1 LO LEAKAGE NULLING G SIDEBAND SUPPRESSION NULLING I2 J I3 H OPTIMIZE THE LINEARITY(HD3,OIP3,..) INPUT PLL REFERENCE F3 F4 E PFD FREQ : AUTOMATICALLY CALCULATED F7 K F6 F2 INPUT DESIRED LO FREQUENCY F1 F5 SYNTH VALUES: AUTOMATICALLY CALCULATED L VCO FREQ : AUTOMATICALLY CALCULATED D 12299-003 C B Figure 3. Main Screen of the ADRF6720 Control Software Table 1. Main Screen Functionality Label A B C D E F1 to F7 G H Function Shows software version. When the USB driver is installed and USB block works correctly, it shows FX2 USB device found, connected. DUT to GUI button. Set automatically according to Label E selection. External LO: Check MOD_EN and uncheck VCO_LDO_EN, CP_EN, REF_BUF_EN, and VCO_EN. However, it is okay to enable all. Internal LO: Click Enable All to enable all blocks related to internal LO. Sets LO path. External LO: Set to 1XLO Path_EXT_1X_LO for Polyphase Filter Path in quadrature LO generation. Set to 2XLO Path_EXT_2X_LO with 2× External LO for Div 2 Phase Splitter Path in quadrature LO generation. Internal LO: Set it at 2XLO Path_INT_2X_VCO for Div 2 Phase Splitter Path in quadrature LO generation Set it at 1XLO Path_INT_1X_VCO for Polyphase Filter Path in quadrature LO generation Internal LO related. F1: Sets frequency and step size; press the Enter key to update. F2: VCO_SEL and VCO frequency are set up automatically by setting Label F1. VCO frequency is 2× to LO frequency. F3: Sets the PLL reference input and divider; ensures PFD frequency at the 11.4 MHz to 40 MHz. (It can be locked above 40 MHz.) F4: Used to optimize internal LO but not usually necessary to tune. F5: Used to optimize spur performance. F6: Selects NEG. F7: Fine tune control of the VTUNE temperature profile. Set VTUNE_DAC_SLOPE to 10 and VTUNE_DAC_OFFSET to 180. Set tunable balun over a frequency band (see Table 2). Set POLi and POLq to control setting for wanted signal at upper side or lower side to LO. POLi = POLq: Low-side LO injection when Q leads I POLi ≠ POLq: High-side LO injection when Q leads I Rev. 0 | Page 5 of 12 UG-689 Label I J K L ADRF6720-EVALZ User Guide Function LO leakage, sideband suppression, linearity optimization. I1: DCOFFI, DCOFFQ: control setting for LO leakage nulling. I2: I_LO, Q_LO: control setting for sideband suppression nulling. I3: MOD_RDAC, MOD_CDAC: optimize the linearity (harmonics, IMD) performance. Selects LO output path. LO_DRV1X_EN: Enables 1 × LO output path (after the quadrature divider) and enables LO output driver. LO_DRV2X_EN: Enables 2 × LO output path (before the quadrature divider) and enables LO output driver. DRVDIV2_EN :Select either 2× or 1× the frequency of the LO on 2 × LO output path ENOP MASK: enable/disable individual blocks. Programmable resistors for VCO LDO, set VCO_LDO_R4SEL(3) to 3 and for VCO_LDO_R2SEL(10) to 10. Table 2. Balun Settings BAL_COUT 0 0 0 0 0 0 0 0 0 0 0 0 0 3 Frequency Range (MHz) FRF > 1730 1550 < FRF < 1730 1380 < FRF < 1550 1250 < FRF < 1380 1170 < FRF < 1250 1100 < FRF < 1170 1020 < FRF < 1100 970 < FRF < 1020 930 < FRF < 970 890 < FRF < 930 840 < FRF < 890 820 < FRF < 840 740 < FRF < 820 680 < FRF < 740 12299-004 BAL_CIN 0 1 2 3 4 8 9 10 11 12 13 14 15 15 Figure 4. Engineering Tab of the ADRF6720 Control Software Rev. 0 | Page 6 of 12 Rev. 0 | Page 7 of 12 R14 Figure 5. Evaluation Board Schematic AGND 2 3 4 5 Q+ JOHNSON142-0701-851 1 AGND 2 3 4 5 AGND C79 3.3PF DNI AGND C78 2PF DNI C77 3.3PF DNI C76 3.3PF DNI AGND C75 2PF DNI 0 0 C88 3.3PF DNI AGND 0 C82 20PF DNI AGND R17 C87 6PF DNI 0 C81 2PF DNI 0 R2 0 AGND C86 3.3PF DNI R6 AGND 3P3V_F R24 R22 C1 0.1UF 0 C91 3.3PF DNI AGND 0 C85 20PF DNI AGND R36 R4 C80 20PF DNI R1 AGND AGND 0 0 C90 6PF DNI R33 R3 C84 2PF DNI C89 3.3PF DNI AGND AGND Y2 6 VCC 4 OUTPUT NC GND 1 3 38.4MEGHZ C83 20PF DNI AGND VCC_TCXO RED C41 3.3PF DNI AGND QJOHNSON142-0701-851 1 AGND 2 3 4 5 IJOHNSON142-0701-851 1 AGND 2 3 4 5 1 C36 0.1UF AGND I+ JOHNSON142-0701-851 1 0 0402 R7 127 AGND C2 100PF R5 127 AGND 2 3 4 5 1 0 R19 3P3V_F AGND 1 R27 2K AGND 10UF C3 AGND C7 0.1UF C A SML-210MTT86 CR1 0 MUXOUT_TP YEL R21 AGND C4 0.1UF 3P3V_F TYCO1-1478979-0 REF_IN R16 0 DNI AGND C5 100PF MUXOUT GND I+ IGND VPOS1 GND QQ+ GND C8 0.1UF C0402 AGND AGND C11 100PF C0402 AGND SDIO SCLK CSB C10 100PF 1 2 3 4 5 6 7 8 9 10 AGND AGND AGND R30 49.9 1000PF C12 AGND C6 0.1UF 3P3V_F CP AGND C9 100PF C14 VT 100PF C0402 100PF C0402 C15 PAD 40 39 38 37 36 35 34 33 32 31 AGND 100PF C0402 C74 100PF C0402 C73 AGND 4 3 T4 AGND 0 R0402 R43 0 R0402 R11 4 PRI T1 6 DNI TC1-1-43A+ AT224-1 3 SEC 1 DNI DNI AGND 1 0 R55 1 AGND 0 1 AGND AGND DNI R38 0 R0402 AGND R0402 R18 0 R62 49.9 R61 10K 3P3V_F AGND 3 2 S1 R32 R15 R0402 DNI AGND 5 4 3 2 R25 0 R0402 DNI AGND C42 0.5PF SLIDER AREA FOR 0.5PF CAP @2GHZ LO_OUT+ JOHNSON142-0701-851 1 AGND 5 4 3 2 C31 100PF AGND 5 4 3 2 C43 10UF C1206 RF_OUT VCC_RF C57 2700PF CP AGND SLIDER AREA FOR 1.5PF CAP U2 @2GHZ RFOUT 3 GND 2 4 ADL5320ARKZ C46 SOT-89 1.5PF AGND AGND AGND C45 22PF C0603 AGND C58 0.1UF R12 300 22PF C0402 5 4 3 2 AGND AMP_OUT JOHNSON142-0701-851 C47 1 15NH L7144 L8 2 1 5.6 R23 1 DNI C54 10UF AGND GND1 BLK 1 R39 AGND C55 10UF 0 0402 AGND 1 1 1 DNI C49 10UF AGND GND3 BLK AGND 1 AGND GND4 BLK AGND C34 10UF 3P3V_F VT VTUNE_TP RED DNI 3P3V_F RED 3P3V_F R77 0 C60 1500PF GND2 BLK VCC_RF RED VCC_RF AGND 1 C59 2700PF 820 R26 CUSTOMER BRD 20KHZ LOOP FILTER CONFIGURATION JOHNSON142-0701-851 C44 10000PF C0603 5 4 3 2 VPOS_AMP RED 1 RFIN 1 R0402 0 1 AGND AGND R40 C29 0.1UF C26 100PF LO_INJOHNSON142-0701-851 1 DNI AGND 5 4 3 2 LO_IN+ JOHNSON142-0701-851 1 C18 C0402 DNI LO_OUTJOHNSON142-0701-851 1 DNI AGND C56 10UF 3P3V_F R0402 DNI C17 C0402 DNI 0 R0402 0 R0402 C16 C0402 DNI C40 R34 C33 0.1UF C24 VCC_RF R20 1 0 AGND 09-03-201-02 AGND C50 10UF AGND C32 100PF R13 AGND 10UF C28 0.1UF DNI R37 0 0402 R0402 AGND VCC_VCO RED DNI C23 0.1UF C0402 AGND UNBAL_IN BAL_OUT2 GND_DC_FEED_RFGND GND NC_6 2 5 6 DNI 0 R0402 R82 TC1-1-43A+ AT224-1 4 6 PRI 0 R0402 3 1 DNI R81 SEC T3 C30 0.1UF AGND ENOP 3P3V_F BAL_OUT1 0 C27 100PF AGND AGND C25 100PF C21 100PF C0402 AGND AGND UNBAL_IN BAL_OUT2 GND_DC_FEED_RFGND GND NC_6 2 5 6 DNI 2500BL14M050T BAL_OUT1 R35 C22 0.1UF 4 3 T2 VCC_LO RED 2500BL14M050T AGND DNI ADRF6720ACPZ 30 29 28 27 26 25 24 23 22 21 U1 C19 100PF VPOS6 GND DECL2 ENOP VPOS5 GND RFOUT GND VPOS4 NC PAD VPOS8 REFIN GND GND CP VPOS7 LOIN+ LOINVTUNE DECL3 VPOS2 DECL1 SDIO SCLK CSB GND VPOS3 LOOUT+ LOOUTGND 11 12 13 14 15 16 17 18 19 20 3P3V_F ADRF6720-EVALZ User Guide UG-689 SCHEMATICS AND ARTWORK 12299-005 D1 DGND DGND C20 0.1UF 3V3_USB A C SML-210MTT86 R56 2K IO C48 0.1UF C51 1UF C35 0.1UF U3 R57 78.7K C37 0.1UF FB C52 1000PF C53 0.1UF DECOUPLING FOR U1 DGND DGND 7 IN1 OUT1 1 8 IN2 OUT2 2 6 SD_N FB 3 PAD GND PAD 5 ADP3334ACPZ C62 0.1UF R58 140K R59 2K WAKEUP RESETN SCL SDA C64 0.1UF IN IN IN IN C63 1UF AGND 0.1UF C66 DGND 0 R60 DGND DGND U5 8 VCC A0 A1 A2 5 SCL SDA WC_N GND 4 24LC64-I-SN DGND 1 2 3 6 7 C65 10PF DGND C38 0.1UF R64 100K R63 2K DGND DGND C39 0.1UF R66 100K DGND DGND 1 2 44 14 5 42 15 16 AGND C68 0.1UF DGND PB0_FD0 PB1_FD1 PB2_FD2 PB3_FD3 PB4_FD4 PB5_FD5 PB6_FD6 PB7_FD7 PD0_FD8 PD1_FD9 PD2_FD10 PD3_FD11 PD4_FD12 PD5_FD13 PD6_FD14 PD7_FD15 GND PAD OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT OUT PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PD0 PD1 PD2 PD3 PD4 PD5 PD6 PD7 PA3 PA4 PA5 PA6 IFCLK CLKOUT CTL0_FLAGA CTL1_FLAGB CTL2_FLAGC C69 22PF XTALOUT XTALIN 1 DM DP OUT OUT OUT OUT CASE 2 4 3 2K R8 PA7 PA0 PA1 PA2 Y1 24.000000MEGHZ E013815 JEDEC_TYPE=QFN56_8X8_PAD5_2X4_5 CY7C68013A-56LTXC 18 19 20 21 22 23 24 25 45 46 47 48 49 50 51 52 33 34 35 36 37 38 39 40 4 8 9 13 54 29 30 31 U6 XTALOUT DPLUS DMINUS IFCLK CLKOUT CTL0_FLAGA CTL1_FLAGB CTL2_FLAGC VCC DGND PA0_INT0_N PA1_INT1_N PA2_SLOE PA3_WU2 PA4_FIFOADR0 PA5_FIFOADR1 PA6_PKTEND PA7_FLAGD_SLCS_N RDY0_SLRD RDY1_SLWR WAKEUP RESERVED XTALIN RESET_N SCL SDA AVCC C67 10PF 11 17 27 32 43 55 5V_USB 3V3_USB 3 7 6 10 Rev. 0 | Page 8 of 12 12 26 28 41 53 56 Figure 6. USB Interface Circuitry on the Customer Evaluation Board PAD DGND CR2 GND PINS P4 DGND 897-43-005-00-100001 G1 G2 G3 G4 1 2 3 4 5 A C SML-210MTT86 DGND DGND 5V_USB DGND C70 22PF 0 R31 0 R28 0 R9 R67 1K DNI C71 330PF DNI R78 1K DNI C13 330PF DNI DGND R79 1K DNI DGND C72 330PF DNI SCLK SDIO CSB 1 2 3 4 5 6 7 8 9 10 TSW-105-08-G-D DNI PLACEHOLDER P3 UG-689 ADRF6720-EVALZ User Guide 12299-006 UG-689 12299-007 ADRF6720-EVALZ User Guide 12299-008 Figure 7. ADRF6720 Evaluation Board Top Figure 8. ADRF6720 Evaluation Board Bottom Rev. 0 | Page 9 of 12 UG-689 ADRF6720-EVALZ User Guide ORDERING INFORMATION BILL OF MATERIALS Table 3. Qty 1 3 Reference Designator 1 4 4 3P3V_F, VCC_TCXO, VPOS_AMP GND1 to GND4 MUXOUT_TP P4 I+, I−, Q+, Q−, LO_IN+, RF_OUT, AMP_OUT, LO_OUT+ REF_IN C1, C4, C6 to C8, C20, C22, C23, C28 to C30, C33, C35 to C39, C48, C53, C62, C64, C66, C68 C2, C5, C9 to C11, C14, C15, C19, C21, C25 to C27, C31, C32, C73, C74 C12 C3, C24, C50, C56 C34, C49, C54, C55 1 C42 1 C43 1 C44 3 1 1 2 1 2 1 1 2 C45, C69, C70 C46 C47 C51, C63 C52 C57, C59 C58 C60 C65, C67 1 24 1 2 1 L8 R1 to R4, R6, R9, C40, R13, R14, R17 to R21, R28, R31, R33 to R36, R39, R40, R55, R60 R12 R22, R24 R23 1 1 1 R26 R27 R30 2 R5, R7 4 1 R8, R56, R59, R63 R57 4 1 1 8 1 23 16 Description PCB (see Table 4) Connector PCB test point red Manufacturer Analog Devices Supplied Components Corporation Part Number 08-20_a03333c TP-104-01-02 Connector PCB test point black Connector PCB test point yellow Conn-PCB RECEPT mini-USB Type B SMT Conn-PCB COAX SMA end launch Components Corporation Components Corporation Mill-Max Johnson TP-104-01-00 TP-104-01-04 897-43-005-00-100001 142-0701-851 Conn-PCB SMA ST Cap cer X7R C0402, 10%, 16 V 0.1 µF Tyco Murata 1-1478979-0 GRM155R71C104KA88D Cap chip mono cer C0G C0402, 5%, 50 V 100 pF Murata GRM1555C1H101JD01D Cap cer C0G C0402, 5%, 50 V 1000 pF Cap cer X5R C0603, 20%, 6.3 V 10 µF Cap cer monolithic X5R, C0805, 10%, 16 V 10 µF Cap cer C0G, C0402, ±0.5 pF, 25 V 0.5 pF Cap cer monolithic X5R, C1206, 10%, 25 V 10 µF Cap monolithic cer X7R, C0603, 10%, 25 V 10000 pF Cap cer NP0, C0603, 5%, 50 V 22 PF Cap cer C0402, 0.25PF, 50 V 1.5 PF Cap cer C0402, 5%, 50 V 22 PF Cap mono cer X5R, C0603, 10%, 25 V 1 µF Cap cer C0G, C0603, 5%, 100 V 1000 pF Cap cer X7R, C0402, 5%, 50 V 2700 pF Cap cer X7R, C0603, 5%, 50 V 0.1 µF Cap cer X7R, C0402, 5%, 50 V 1500 pF Cap cer multilayer NP0, C0402, 5%, 50 V 10 pF Chip inductor L7144, 5% 15 nH Res film SMD R0402, 5%, 1/16 W 0 Ω Murata Murata Murata GRM1555C1H102JA01 GRM188R60J106ME47D GRM21BR61C106KE15L Kemet C0402C508D3GACTU Murata GRM31CR61E106KA12L Murata GRM188R71E103KA01D Phycomp (Yageo) Phycomp (Yageo) Phycomp (Yageo) Murata TDK Murata Murata Murata Phycomp (Yageo) Coilcraft Panasonic CC0603JRNP09BN220 0402CG159C9B200 0402CG220J9B200 GRM188R61E105KA12D C1608C0G2A102J GRM155R71H272JA01 GRM188R71H104JA93D GRM155R71H152JA01 CC0402JRNP09BN100 Res film SMD R0402, 5%, 1/16 W 300 Ω Res film SMD R0603, 1%, 1/16 W 0 Ω Res thick film chip, R0402, 5%, 1/10 W 5.6 Ω Res film SMD R0402, 5%, 1/16 W 820 Ω Res chip SMD R0402, 5%, 1/16 W 2 kΩ Res ultra-PREC ultra-reliability MF chip R0402, 0.1%, 1/16 W 49.9 Ω Res prec thick film chip R0402, 1%, 1/10 W 127 Ω Res film SMD R0603, 1%, 1/10 W 2 kΩ Res prec thick film chip R0603, 1%, 50 V, 1/10 W 78.7 kΩ Panasonic Multicomp Panasonic ERJ-2GEJ301X MC0603WG00000T5E-TC ERJ-2GEJ5R6X Panasonic Yageo SUSUMU ERJ-2GEJ821X RC0402JR-072KL RG1005P-49R9-B-T5 Panasonic ERJ-2RKF1270X Yageo-Phycomp Panasonic 9C06031A2001FKHFT ERJ-3EKF7872V Rev. 0 | Page 10 of 12 0603CS-15NXJLU ERJ-2GE0R00X ADRF6720-EVALZ User Guide Qty 1 Reference Designator R58 1 R61 1 R62 2 R64, R66 1 S1 3 2 1 D1, CR1, CR2 T1, T3 U1 1 U2 1 U3 1 1 U5 U6 1 Y1 1 Y2 UG-689 Description Res prec thick film chip R0603, 1%, 50 V, 1/10 W 140 kΩ Res prec thick film chip R0402, 1%, 1/16 W 10 kΩ Res prec thick film chip R0402, 1%, 1/16 W 49.9 Ω Res PREC thick film chip R0603, 1%, 50 V, 1/10 W 100 kΩ SW PCB mount slide, SWSECMA0903201 LED 570 NM WTR clr LED0805 SMD (green) XFMR RF SMT AT224-1 IC-ADI wideband quadrature MOD QFN40_6X6_PAD4_6X4_6 IC-ADI 400MHZ-2700MHZ driver RF amp SOT-89, 5 V IC-ADI high ACC. low IQ ADJ low drop reg QFN8_3X3_PAD1_75X1_45 IC 64KBIT EEPROM, SO8 IC HS USB peripheral,3 V-3.6 V, QFN56_8X8_PAD5_2X4_5 IC crystal SMD XTALNX3225 24.000000MEGHZ IC crystal OSC prelim, 3.3 V YSML98W79H35_B 38.4 MHz Manufacturer Panasonic Part Number ERJ-3EKF1403V Panasonic ERJ-2RKF1002X Panasonic ERJ-2RKF49R9X Panasonic ERJ-3EKF1003V SECMA 09-03-201-02 ROHM Mini-Circuits Analog Devices, Inc. SML-210MTT86 TC1-1-43A+ ADRF6720ACPZ Analog Devices, Inc. ADL5320ARKZ Analog Devices, Inc. ADP3334ACPZ Microchip Cypress Semiconductor 24LC64-I-SN CY7C68013A-56LTXC NDK NX3225SA-24.000000MHZ Rakon 509540 These components are part of the printed circuit board (PCB) or should not be installed. Table 4. ADRF6720 Evaluation Board Bill of Materials—Do Not Install Qty 3 3 8 4 4 2 2 1 11 3 2 4 1 Reference Designator C13, C71, C72 C16 to C18 C41, C76, C77, C79, C86, C88, C89, C91 C75, C78, C81, C84 C80,C82,C83,C85 C87, C90 LO_IN−, LO_OUT− P3 R11, R15, R16, R25, R32, R37, R38, R43, R77, R81, R82 R67, R78, R79 T2, T4 Description Cap cer X7R C0402, 10%, 50 V 330 pF Do not install (TBD_C0402) TBD0402 Cap cer C0G SMD C0402, ±0.25 pF, 50 V 3.3 pF Manufacturer1 Murata N/A Murata Part No. GRM155R71H331KA01D TBD0402 GJM1555C1H3R3CB01D Cap cer C0G SMD C0402, ±0.25 pF, 50 V 2 pF Cap mono cer C0G C0402, 5%, 50 V 20 pF Cap chip mono cer C0G C0402, ±0.1 pF, 50 V 6 pF Conn-PCB coax SMA end launch Conn-PCB HDR ST 10P Res film SMD R0402, 5%, 1/16 W 0 Ω Murata Murata Murata Johnson Samtec Panasonic GJM1555C1H2R0CB01D GRM1555C1H200JZ01D GRM1555C1H6R0BZ01 142-0701-851 TSW-105-08-G-D ERJ-2GE0R00X Res prec thick film chip R0402, 1%, 1/10 W 1K XFMR 2.5 GHz balun, T0603-6P ERJ-2RKF1001X 2500BL14M050T VCC_LO, VCC_RF, VCC_VCO, VTUNE_TP Conn-PCB test point red Panasonic Johanson Technology Components Corporation N/A = not applicable. Rev. 0 | Page 11 of 12 TP-104-01-02 UG-689 ADRF6720-EVALZ User Guide NOTES ESD Caution ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality. Legal Terms and Conditions By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc. (“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term “Third Party” includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER’S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed. ©2014 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG12299-0-5/14(0) Rev. 0 | Page 12 of 12