Dual, 16-Bit, 1130 MSPS, TxDAC+ Digital-to-Analog Converter AD9122-EP Enhanced Product

advertisement

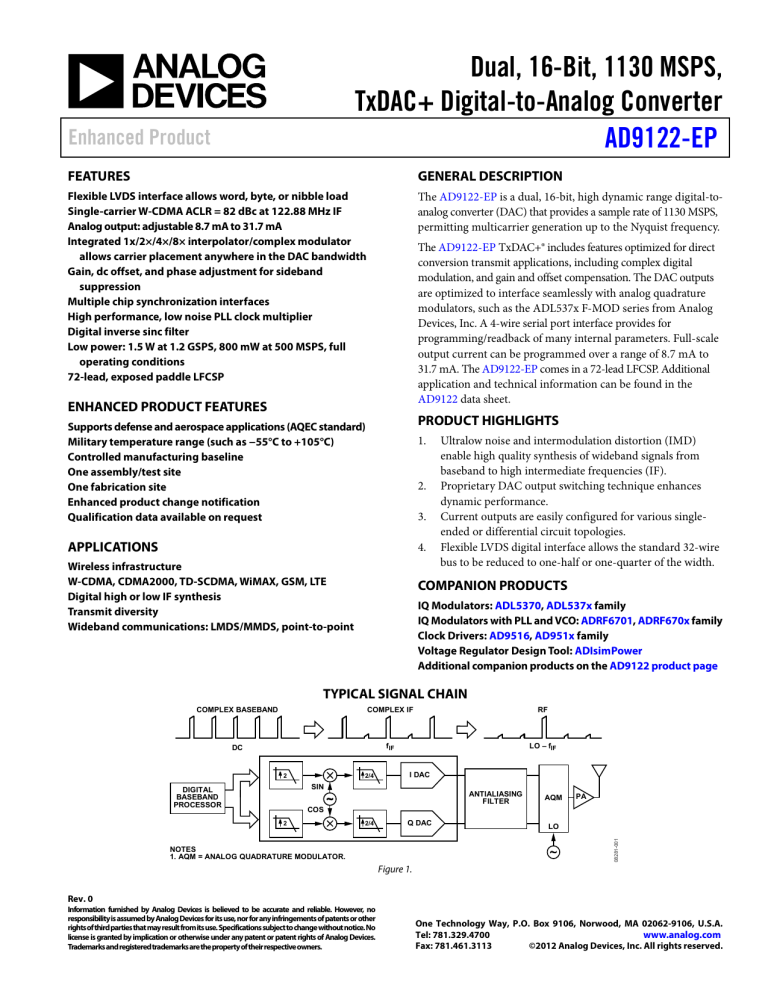

Dual, 16-Bit, 1130 MSPS, TxDAC+ Digital-to-Analog Converter AD9122-EP Enhanced Product FEATURES GENERAL DESCRIPTION Flexible LVDS interface allows word, byte, or nibble load Single-carrier W-CDMA ACLR = 82 dBc at 122.88 MHz IF Analog output: adjustable 8.7 mA to 31.7 mA Integrated 1x/2×/4×/8× interpolator/complex modulator allows carrier placement anywhere in the DAC bandwidth Gain, dc offset, and phase adjustment for sideband suppression Multiple chip synchronization interfaces High performance, low noise PLL clock multiplier Digital inverse sinc filter Low power: 1.5 W at 1.2 GSPS, 800 mW at 500 MSPS, full operating conditions 72-lead, exposed paddle LFCSP The AD9122-EP is a dual, 16-bit, high dynamic range digital-toanalog converter (DAC) that provides a sample rate of 1130 MSPS, permitting multicarrier generation up to the Nyquist frequency. The AD9122-EP TxDAC+® includes features optimized for direct conversion transmit applications, including complex digital modulation, and gain and offset compensation. The DAC outputs are optimized to interface seamlessly with analog quadrature modulators, such as the ADL537x F-MOD series from Analog Devices, Inc. A 4-wire serial port interface provides for programming/readback of many internal parameters. Full-scale output current can be programmed over a range of 8.7 mA to 31.7 mA. The AD9122-EP comes in a 72-lead LFCSP. Additional application and technical information can be found in the AD9122 data sheet. ENHANCED PRODUCT FEATURES PRODUCT HIGHLIGHTS Supports defense and aerospace applications (AQEC standard) Military temperature range (such as −55°C to +105°C) Controlled manufacturing baseline One assembly/test site One fabrication site Enhanced product change notification Qualification data available on request 1. 2. 3. APPLICATIONS 4. Wireless infrastructure W-CDMA, CDMA2000, TD-SCDMA, WiMAX, GSM, LTE Digital high or low IF synthesis Transmit diversity Wideband communications: LMDS/MMDS, point-to-point Ultralow noise and intermodulation distortion (IMD) enable high quality synthesis of wideband signals from baseband to high intermediate frequencies (IF). Proprietary DAC output switching technique enhances dynamic performance. Current outputs are easily configured for various singleended or differential circuit topologies. Flexible LVDS digital interface allows the standard 32-wire bus to be reduced to one-half or one-quarter of the width. COMPANION PRODUCTS IQ Modulators: ADL5370, ADL537x family IQ Modulators with PLL and VCO: ADRF6701, ADRF670x family Clock Drivers: AD9516, AD951x family Voltage Regulator Design Tool: ADIsimPower Additional companion products on the AD9122 product page TYPICAL SIGNAL CHAIN COMPLEX BASEBAND COMPLEX IF RF DC fIF LO – fIF 2 2/4 I DAC SIN DIGITAL BASEBAND PROCESSOR ANTIALIASING FILTER AQM PA COS 2/4 Q DAC LO 08281-001 2 NOTES 1. AQM = ANALOG QUADRATURE MODULATOR. Figure 1. Rev. 0 Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©2012 Analog Devices, Inc. All rights reserved. AD9122-EP Enhanced Product TABLE OF CONTENTS Features .............................................................................................. 1 Digital Specifications ....................................................................5 Enhanced Product Features ............................................................ 1 Digital Input Data Timing Specifications ..................................5 Applications ....................................................................................... 1 AC Specifications ..........................................................................6 General Description ......................................................................... 1 Absolute Maximum Ratings ............................................................8 Product Highlights ........................................................................... 1 Thermal Resistance .......................................................................8 Companion Products ....................................................................... 1 ESD Caution...................................................................................8 Typical Signal Chain......................................................................... 1 Pin Configuration and Function Descriptions..............................9 Revision History ............................................................................... 2 Outline Dimensions ....................................................................... 12 Functional Block Diagram .............................................................. 3 Ordering Guide .......................................................................... 12 Specifications..................................................................................... 4 DC Specifications ......................................................................... 4 REVISION HISTORY 8/12—Revision 0: Initial Version Rev. 0 | Page 2 of 12 Enhanced Product AD9122-EP FUNCTIONAL BLOCK DIAGRAM 16 IOUT1P DAC 1 AUX 16-BIT IOUT1N 16 fDATA /2 PRE MOD NCO AND MOD HB1 HB2 10 HB3 I OFFSET Q OFFSET INV SINC DAC_CLK 16 16 INVSINC_CLK INTP FACTOR HB3_CLK HB2_CLK MODE HB1_CLK FRAMEP/FRAMEN PHASE CORRECTION DCIP/DCIN 10 1.2G IOUT2P DAC 2 AUX 16-BIT IOUT2N GAIN 2 FIFO GAIN 1 DATA RECEIVER D15P/D15N D0P/D0N 1.2G 10 REF AND BIAS REFIO FSADJ INTERNAL CLOCK TIMING AND CONTROL LOGIC DAC CLK_SEL PLL CONTROL SERIAL INPUT/OUTPUT PORT POWER-ON RESET MULTICHIP SYNCHRONIZATION DAC_CLK 1 CLOCK MULTIPLIER (2× TO 16×) CLK RCVR DACCLKP DACCLKN CLK RCVR REFCLKP REFCLKN 08281-002 IRQ RESET CS SCLK SDO 0 SYNC PLL_LOCK SDIO PROGRAMMING REGISTERS Figure 2. Rev. 0 | Page 3 of 12 AD9122-EP Enhanced Product SPECIFICATIONS DC SPECIFICATIONS TMIN to TMAX, AVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, IFS = 20 mA, maximum sample rate, unless otherwise noted. Table 1. Parameter RESOLUTION ACCURACY Differential Nonlinearity (DNL) Integral Nonlinearity (INL) MAIN DAC OUTPUTS Offset Error Gain Error (with Internal Reference) Full-Scale Output Current 1 Output Compliance Range Power Supply Rejection Ratio, AVDD33 Output Resistance Gain DAC Monotonicity Settling Time to Within ±0.5 LSB MAIN DAC TEMPERATURE DRIFT Offset Gain Reference Voltage REFERENCE Internal Reference Voltage Output Resistance ANALOG SUPPLY VOLTAGES AVDD33 CVDD18 DIGITAL SUPPLY VOLTAGES DVDD18 IOVDD POWER CONSUMPTION 2× Mode, fDAC = 491.22 MSPS, IF = 10 MHz, PLL Off 2× Mode, fDAC = 491.22 MSPS, IF = 10 MHz, PLL On 8× Mode, fDAC = 800 MSPS, IF = 10 MHz, PLL Off AVDD33 CVDD18 DVDD18 Power-Down Mode (Register 0x01 = 0xF0) POWER-UP TIME OPERATING RANGE 1 Min Typ 16 Max ±2.1 ±3.7 −0.001 −4.6 8.66 −1.0 −0.3 0 ±2 19.6 Unit Bits LSB LSB +0.001 +4.6 31.66 +1.0 +0.3 10 Guaranteed 20 % FSR % FSR mA V % FSR/V MΩ ns 0.04 100 30 ppm/°C ppm/°C ppm/°C 1.2 5 V kΩ 3.13 1.71 3.3 1.8 3.47 1.89 V V 1.71 1.71 1.8 1.8/3.3 1.89 3.47 V V 1259 57 90 505 18.8 −55 834 913 1135 55 85 444 6.5 260 +25 mW mW mW mA mA mA mW ms °C Based on a 10 kΩ external resistor between FSADJ and AVSS. Rev. 0 | Page 4 of 12 +105 Enhanced Product AD9122-EP DIGITAL SPECIFICATIONS TMIN to TMAX, AVDD33 = 3.3 V, IOVDD = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, IFS = 20 mA, maximum sample rate, unless otherwise noted. Table 2. Parameter CMOS INPUT LOGIC LEVEL Input VIN Logic High Input VIN Logic Low CMOS OUTPUT LOGIC LEVEL Output VOUT Logic High Output VOUT Logic Low LVDS RECEIVER INPUTS 1 Input Voltage Range, VIA or VIB Input Differential Threshold, VIDTH Input Differential Hysteresis, VIDTHH to VIDTHL Receiver Differential Input Impedance, RIN LVDS Input Rate DAC CLOCK INPUT (DACCLKP, DACCLKN) Differential Peak-to-Peak Voltage Common-Mode Voltage Maximum Clock Rate REFCLK INPUT (REFCLKP, REFCLKN) Differential Peak-to-Peak Voltage Common-Mode Voltage REFCLK Frequency (PLL Mode) REFCLK Frequency (SYNC Mode) Test Conditions/Comments Min IOVDD = 1.8 V IOVDD = 2.5 V IOVDD = 3.3 V IOVDD = 1.8 V IOVDD = 2.5 V, 3.3 V 1.2 1.6 2.0 IOVDD = 1.8 V IOVDD = 2.5 V IOVDD = 3.3 V IOVDD = 1.8 V, 2.5 V, 3.3 V Applies to data, DCI, and FRAME inputs 1.4 1.8 2.4 825 −100 Max Unit 0.6 0.8 V V V V V 0.4 V V V V 1675 +100 mV mV mV 120 Ω 500 1.25 2000 mV V MHz 500 1.25 2000 mV V MHz MHz 20 80 See Table 5 100 Self-biased input, ac-coupled 1230 100 1 GHz ≤ fVCO ≤ 2.1 GHz See the Multichip Synchronization section of the AD9122 data sheet for conditions SERIAL PORT INTERFACE Maximum Clock Rate (SCLK) Minimum Pulse Width High (tPWH) Minimum Pulse Width Low (tPWL) Setup Time, SDIO to SCLK (tDS) Hold Time, SDIO to SCLK (tDH) Data Valid, SDO to SCLK (tDV) Setup Time, CS to SCLK (tDCSB) 1 Typ 600 600 40 12.5 12.5 2.1 0.75 2.85 1.4 LVDS receiver is compliant with the IEEE 1596 reduced range link, unless otherwise noted. DIGITAL INPUT DATA TIMING SPECIFICATIONS Table 3. Parameter LATENCY (DACCLK CYCLES) 1× Interpolation (With or Without Modulation) 2× Interpolation (With or Without Modulation) 4× Interpolation (With or Without Modulation) 8× Interpolation (With or Without Modulation) Inverse Sinc Fine Modulation 15.625 0 Value Unit 64 135 292 608 20 8 Cycles Cycles Cycles Cycles Cycles Cycles Rev. 0 | Page 5 of 12 MHz ns ns ns ns ns ns AD9122-EP Enhanced Product AC SPECIFICATIONS TMIN to TMAX, AVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, IFS = 20 mA, maximum sample rate, unless otherwise noted. Table 4. Parameter SPURIOUS-FREE DYNAMIC RANGE (SFDR) fDAC = 100 MSPS, fOUT = 20 MHz fDAC = 200 MSPS, fOUT = 50 MHz fDAC = 400 MSPS, fOUT = 70 MHz fDAC = 800 MSPS, fOUT = 70 MHz TWO-TONE INTERMODULATION DISTORTION (IMD) fDAC = 200 MSPS, fOUT = 50 MHz fDAC = 400 MSPS, fOUT = 60 MHz fDAC = 400 MSPS, fOUT = 80 MHz fDAC = 800 MSPS, fOUT = 100 MHz NOISE SPECTRAL DENSITY (NSD), EIGHT-TONE, 500 kHz TONE SPACING fDAC = 200 MSPS, fOUT = 80 MHz fDAC = 400 MSPS, fOUT = 80 MHz fDAC = 800 MSPS, fOUT = 80 MHz W-CDMA ADJACENT CHANNEL LEAKAGE RATIO (ACLR), SINGLE-CARRIER fDAC = 491.52 MSPS, fOUT = 10 MHz fDAC = 491.52 MSPS, fOUT = 122.88 MHz fDAC = 983.04 MSPS, fOUT = 122.88 MHz W-CDMA SECOND ACLR, SINGLE-CARRIER fDAC = 491.52 MSPS, fOUT = 10 MHz fDAC = 491.52 MSPS, fOUT = 122.88 MHz fDAC = 983.04 MSPS, fOUT = 122.88 MHz Min Typ Max Unit 78 80 69 72 dBc dBc dBc dBc 84 86 84 81 dBc dBc dBc dBc −162 −163 −164 dBm/Hz dBm/Hz dBm/Hz 84 82 83 dBc dBc dBc 88 86 88 dBc dBc dBc Table 5. Maximum Rate (MSPS) with DVDD and CVDD Supply Regulation Bus Width Nibble (4 Bits) Byte (8 Bits) Word (16 Bits) Interpolation Factor 1× 2× 4× 8× 1× 2× 4× 8× 1× 2× (HB1) 2× (HB2) 4× 8× 1.8 V ± 5% 1000 1000 1000 1000 1000 1000 1000 500 1000 800 1000 500 250 fINTERFACE (MSPS) DVDD18, CVDD18 = 1.8 V ± 2% 1.9 V ± 2% 1100 1130 1100 1130 1100 1130 1100 1130 1100 1130 1100 1130 1100 1130 550 565 1100 1130 900 900 1100 1130 550 565 275 282.5 Rev. 0 | Page 6 of 12 1.8 V ± 5% 125 250 500 1000 250 500 1000 1000 500 800 1000 1000 1000 fDAC (MSPS) DVDD18, CVDD18 = 1.8 V ± 2% 1.9 V ± 2% 137.5 141.25 275 282.5 550 565 1100 1130 275 282.5 550 565 1100 1130 1100 1130 550 565 900 900 1100 1130 1100 1130 1100 1130 Enhanced Product AD9122-EP The setup (tS) and hold (tH) times, with respect to the edges, are shown in Figure 3. The minimum setup and hold times are shown in Table 6. tDATA tDATA DCI SAMPLING INTERVAL SAMPLING INTERVAL tS tS tH tH 08281-146 DATA Figure 3. Timing Diagram for Input Data Port Table 6. Data to DCI Setup and Hold Times DCI Delay Register 0x16, Bits[1:0] 00 01 10 11 Minimum Setup Time, tS (ns) −0.01 −0.19 −0.38 −0.44 Minimum Hold Time, tH (ns) 0.65 0.95 1.22 1.38 Sampling Interval (ns) 0.64 0.76 0.84 0.94 The data interface timing can be verified by using the sample error detection (SED) circuitry. See the Interface Timing Validation section in the AD9122 data sheet for more information. Rev. 0 | Page 7 of 12 AD9122-EP Enhanced Product ABSOLUTE MAXIMUM RATINGS THERMAL RESISTANCE Table 7. Parameter AVDD33 to AVSS, EPAD, CVSS, DVSS IOVDD to AVSS, EPAD, CVSS, DVSS DVDD18, CVDD18 to AVSS, EPAD, CVSS, DVSS AVSS to EPAD, CVSS, DVSS EPAD to AVSS, CVSS, DVSS CVSS to AVSS, EPAD, DVSS DVSS to AVSS, EPAD, CVSS FSADJ, REFIO, IOUT1P, IOUT1N, IOUT2P, IOUT2N to AVSS D[15:0]P, D[15:0]N, FRAMEP, FRAMEN, DCIP, DCIN to EPAD, DVSS DACCLKP, DACCLKN, REFCLKP, REFCLKN to CVSS RESET, IRQ, CS, SCLK, SDIO, SDO to EPAD, DVSS Junction Temperature Storage Temperature Range The exposed pad (EPAD) of the 72-lead LFCSP must be soldered to the ground plane (AVSS). The EPAD provides an electrical, thermal, and mechanical connection to the board. Rating −0.3 V to +3.6 V −0.3 V to +3.6 V −0.3 V to +2.1 V −0.3 V to +0.3 V −0.3 V to +0.3 V −0.3 V to +0.3 V −0.3 V to +0.3 V −0.3 V to AVDD33 + 0.3 V Typical θJA, θJB, and θJC values are specified for a 4-layer board in still air. Airflow increases heat dissipation, effectively reducing θJA and θJB. Table 8. Thermal Resistance Package 72-Lead LFCSP −0.3 V to DVDD18 + 0.3 V −0.3 V to CVDD18 + 0.3 V ESD CAUTION −0.3 V to IOVDD + 0.3 V 125°C −65°C to +150°C Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Rev. 0 | Page 8 of 12 θJA 20.7 θJB 10.9 θJC 1.1 Unit °C/W Conditions EPAD soldered to ground plane Enhanced Product AD9122-EP 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 CVDD18 CVDD18 REFCLKP REFCLKN AVDD33 IOUT1P IOUT1N AVDD33 AVSS FSADJ REFIO AVSS AVDD33 IOUT2N IOUT2P AVDD33 AVSS NC PIN CONFIGURATION AND FUNCTION DESCRIPTIONS 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 PIN 1 INDICATOR AD9122 TOP VIEW (Not to Scale) 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 RESET CS SCLK SDIO SDO DVDD18 D0N D0P D1N D1P DVSS DVDD18 D2N D2P D3N D3P D4N D4P NOTES 1. EXPOSED PAD (EPAD) MUST BE SOLDERED TO THE GROUND PLANE (AVSS). THE EPAD PROVIDES AN ELECTRICAL, THERMAL, AND MECHANICAL CONNECTION TO THE BOARD. 2. NC = NO CONNECT. DO NOT CONNECT TO THIS PIN. 08281-003 D11P D11N D10P D10N D9P D9N D8P D8N DCIP DCIN DVDD18 DVSS D7P D7N D6P D6N D5P D5N 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 CVDD18 DACCLKP DACCLKN CVSS FRAMEP FRAMEN IRQ D15P D15N NC IOVDD DVDD18 D14P D14N D13P D13N D12P D12N Figure 4. Pin Configuration Table 9. Pin Function Descriptions Pin No. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 Mnemonic CVDD18 DACCLKP DACCLKN CVSS FRAMEP FRAMEN IRQ D15P D15N NC IOVDD DVDD18 D14P D14N D13P D13N D12P D12N D11P D11N D10P D10N D9P D9N Description 1.8 V Clock Supply. Supplies clock receivers, clock distribution, and PLL circuitry. DAC Clock Input, Positive. DAC Clock Input, Negative. Clock Supply Common. Frame Input, Positive. This pin must be tied to DVSS if not used. Frame Input, Negative. This pin must be tied to DVDD18 if not used. Interrupt Request. Open-drain, active low output. Connect an external pull-up to IOVDD through a 10 kΩ resistor. Data Bit 15 (MSB), Positive. Data Bit 15 (MSB), Negative. No Connect. Do not connect to this pin. Supply Pin for Serial Port I/O Pins, RESET, and IRQ. 1.8 V to 3.3 V can be supplied to this pin. 1.8 V Digital Supply. Supplies power to digital core and digital data ports. Data Bit 14, Positive. Data Bit 14, Negative. Data Bit 13, Positive. Data Bit 13, Negative. Data Bit 12, Positive. Data Bit 12, Negative. Data Bit 11, Positive. Data Bit 11, Negative. Data Bit 10, Positive. Data Bit 10, Negative. Data Bit 9, Positive. Data Bit 9, Negative. Rev. 0 | Page 9 of 12 AD9122-EP Pin No. 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 Mnemonic D8P D8N DCIP DCIN DVDD18 DVSS D7P D7N D6P D6N D5P D5N D4P D4N D3P D3N D2P D2N DVDD18 DVSS D1P D1N D0P D0N DVDD18 SDO SDIO SCLK CS RESET NC AVSS AVDD33 IOUT2P IOUT2N AVDD33 AVSS REFIO FSADJ AVSS AVDD33 IOUT1N IOUT1P AVDD33 REFCLKN REFCLKP CVDD18 CVDD18 EPAD Enhanced Product Description Data Bit 8, Positive. Data Bit 8, Negative. Data Clock Input, Positive. Data Clock Input, Negative. 1.8 V Digital Supply. Supplies power to digital core and digital data ports. Digital Common. Data Bit 7, Positive. Data Bit 7, Negative. Data Bit 6, Positive. Data Bit 6, Negative. Data Bit 5, Positive. Data Bit 5, Negative. Data Bit 4, Positive. Data Bit 4, Negative. Data Bit 3, Positive. Data Bit 3, Negative. Data Bit 2, Positive. Data Bit 2, Negative. 1.8 V Digital Supply. Supplies power to digital core and digital data ports. Digital Common. Data Bit 1, Positive. Data Bit 1, Negative. Data Bit 0 (LSB), Positive. Data Bit 0 (LSB), Negative. 1.8 V Digital Supply. Supplies power to digital core and digital data ports. Serial Port Data Output (CMOS Levels with Respect to IOVDD). Serial Port Data Input/Output (CMOS Levels with Respect to IOVDD). Serial Port Clock Input (CMOS Levels with Respect to IOVDD). Serial Port Chip Select, Active Low (CMOS Levels with Respect to IOVDD). Reset, Active Low (CMOS Levels with Respect to IOVDD). No Connect. Do not connect to this pin. Analog Supply Common. 3.3 V Analog Supply. Q DAC Positive Current Output. Q DAC Negative Current Output. 3.3 V Analog Supply. Analog Supply Common. Voltage Reference. Nominally 1.2 V output. Should be decoupled to AVSS. Full-Scale Current Output Adjust. Place a 10 kΩ resistor from this pin to AVSS. Analog Supply Common. 3.3 V Analog Supply. I DAC Negative Current Output. I DAC Positive Current Output. 3.3 V Analog Supply. PLL Reference Clock Input, Negative. This pin has a secondary function as a synchronization input. PLL Reference Clock Input, Positive. This pin has a secondary function as a synchronization input. 1.8 V Clock Supply. Supplies clock receivers, clock distribution, and PLL circuitry. 1.8 V Clock Supply. Supplies clock receivers, clock distribution, and PLL circuitry. The exposed pad (EPAD) must be soldered to the ground plane (AVSS). The EPAD provides an electrical, thermal, and mechanical connection to the board. Rev. 0 | Page 10 of 12 Enhanced Product AD9122-EP Table 22A is unique to the AD9122-EP. Refer to the Digital Datapath section of the AD9122 data sheet for further information. All other tables, which have been omitted, can be found in the AD9122 data sheet. Table 22A. Summary of Data Rates and Bandwidths vs. Interpolation Modes (DVDD18, CVDD18 = 1.9 V ± 2%) Bus Width Nibble (4 Bits) Byte (8 Bits) Word (16 Bits) HB3 0 0 0 0 1 1 0 0 0 0 1 1 0 0 0 0 1 1 Filter Modes HB2 HB1 0 0 0 1 1 0 1 1 1 0 1 1 0 0 0 1 1 0 1 1 1 0 1 1 0 0 0 1 1 0 1 1 1 0 1 1 fBUS (Mbps) 1130 1130 1130 1130 1130 1130 1130 1130 1130 1130 1130 565 1130 900 1130 565 565 282.5 fDATA (Mbps) 141.25 141.25 141.25 141.25 141.25 141.25 282.5 282.5 282.5 282.5 282.5 141.25 565 450 565 282.5 282.5 141.25 Rev. 0 | Page 11 of 12 Real Signal Bandwidth (MHz) 69 55 34.5 55 34.5 55 188 110 69 110 69 55 275 180 138 110 69 55 fDAC (MHz) 141.25 282.5 282.5 565 565 1130 282.5 565 565 1130 1130 1130 565 900 1130 1130 1130 1130 AD9122-EP Enhanced Product OUTLINE DIMENSIONS 10.00 BSC SQ 0.60 0.42 0.24 0.60 0.42 0.24 55 54 72 1 PIN 1 INDICATOR PIN 1 INDICATOR 9.75 BSC SQ 0.50 BSC 6.15 6.00 SQ 5.85 EXPOSED PAD (BOTTOM VIEW) 0.50 0.40 0.30 1.00 0.85 0.80 SEATING PLANE 0.80 MAX 0.65 TYP 12° MAX 19 8.50 REF 0.05 MAX 0.02 NOM COPLANARITY 0.08 0.20 REF 0.30 0.23 0.18 18 37 36 FOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONS SECTION OF THIS DATA SHEET. COMPLIANT TO JEDEC STANDARDS MO-220-VNND-4 052809-A TOP VIEW Figure 5. 72-Lead Lead Frame Chip Scale Package [LFCSP_VQ] 10 mm × 10 mm Body, Very Thin Quad (CP-72-7) Dimensions shown in millimeters ORDERING GUIDE Model 1 AD9122SCPZ-EP AD9122SCPZ-EP-RL 1 Temperature Range −55°C to +105°C −55°C to +105°C Package Description 72-Lead Lead Frame Chip Scale Package [LFCSP_VQ] 72-Lead Lead Frame Chip Scale Package [LFCSP_VQ] Z = RoHS Compliant Part. ©2012 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D10784-0-8/12(0) Rev. 0 | Page 12 of 12 Package Option CP-72-7 CP-72-7