Evaluation Board for Dual VGA and ADC EVAL-AD8332/AD9238 FEATURES

advertisement

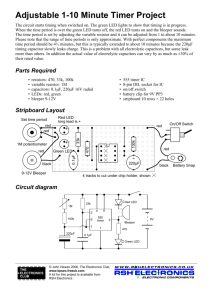

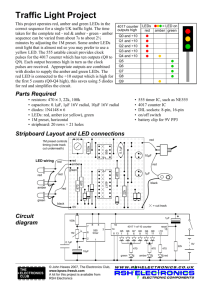

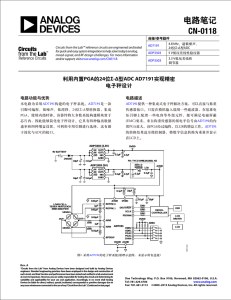

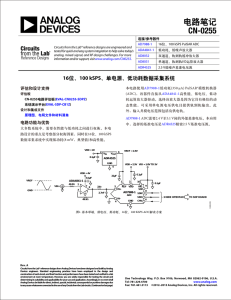

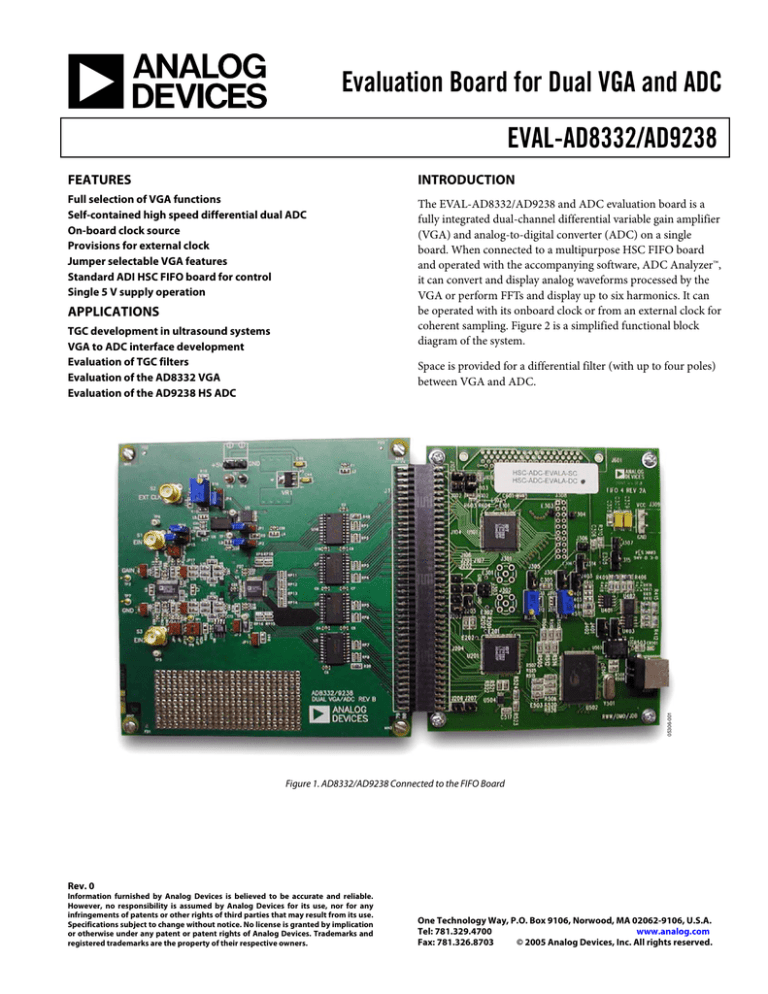

Evaluation Board for Dual VGA and ADC EVAL-AD8332/AD9238 FEATURES INTRODUCTION Full selection of VGA functions Self-contained high speed differential dual ADC On-board clock source Provisions for external clock Jumper selectable VGA features Standard ADI HSC FIFO board for control Single 5 V supply operation The EVAL-AD8332/AD9238 and ADC evaluation board is a fully integrated dual-channel differential variable gain amplifier (VGA) and analog-to-digital converter (ADC) on a single board. When connected to a multipurpose HSC FIFO board and operated with the accompanying software, ADC Analyzer™, it can convert and display analog waveforms processed by the VGA or perform FFTs and display up to six harmonics. It can be operated with its onboard clock or from an external clock for coherent sampling. Figure 2 is a simplified functional block diagram of the system. APPLICATIONS TGC development in ultrasound systems VGA to ADC interface development Evaluation of TGC filters Evaluation of the AD8332 VGA Evaluation of the AD9238 HS ADC 05306-001 Space is provided for a differential filter (with up to four poles) between VGA and ADC. Figure 1. AD8332/AD9238 Connected to the FIFO Board Rev. 0 Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved. EVAL-AD8332/AD9238 TABLE OF CONTENTS General Description ......................................................................... 3 Printed Board Layout..................................................................... 12 Operation........................................................................................... 7 Ordering Information.................................................................... 18 Equipment Needed....................................................................... 7 Ordering Guide .......................................................................... 19 Initial SetUp .................................................................................. 7 ESD Caution................................................................................ 19 Initializing Analyzer Menus........................................................ 9 REVISION HISTORY 1/05—Revision 0: Initial Version Rev. 0 | Page 2 of 20 EVAL-AD8332/AD9238 GENERAL DESCRIPTION Figure 3 is a schematic of the VGA section of the board. There are several user options available for the AD8332. The input impedance is determined by the value of the feedback (RFBn) resistors. Although the default input impedance is 50 Ω, other impedances are obtained replacing the surface mount resistors with the appropriate values (consult the AD8332 data sheet for reference). Removing the feedback resistor results in the open circuit input impedance of 6 kΩ. As a rule of thumb, the value of the resistor is 5.5 × the desired matching impedance. Figure 4 is the ADC and clock schematic and the power subcircuit The AD8332 operates from a single 5 V supply, while a 3.3 V LDO (VR1) provides power for the ADC, clock, and digital interface circuitry. Power pins on the devices are decoupled using ferrite beads. The on-board clock frequency is 20 MHz; thus, the software must be set up with a windowing function to optimize noncoherent sampling. An SMA connector, S2, is provided for an external clock if coherent sampling is desired. The jumper, JP4, must be moved to its upper position. Trimpot R16 can be used to center the clock offset. If R9 and R10 are removed, the two channels of the AD9238 can be operated with independent clocks. Consult the AD9238 data sheet for additional operating details. Figure 5 is a schematic of the interface circuit. Note that the FIFO evaluation board is available for a parallel port, which uses a standard printer cable, and for a USB. Many new laptop computers have only USB ports, while older laptops have parallel ports but not USB interfaces. Be sure to select the version that will interface with your computer. For input frequencies from 1 MHz to 5 MHz, the 20 MHz onboard clock provides for adequate sampling despite noncoherency with the input signal, as long as windowing is enabled. (Windowing is an option offered in ADC Analyzer, which ensures that whole integers of the input waveform are sampled.) For the examples shown in this data sheet, the input signal was 1 MHz and the Hanning window option was selected. For coherent sampling, synchronized external generators are required for clock and signal inputs. Refer to the FIFO board data sheet for further information. The signal generator shown in Figure 6 is a general-purpose instrument found on the benches of many labs. Harmonic distortion, although sufficiently low for most applications, can nonetheless be higher than that generated in either the AD8332 or AD9238. To reduce this level at the input, a low pass filter at the frequency of interest may be required. STANDARD PRINTER CABLE AD8332 AD9238 A/D VGA VOH VOL I/O REGISTER TIMING AND CONTROL VOH 20MHz CLOCK Figure 2. Simplified Block Diagram Rev. 0 | Page 3 of 20 05306-002 VOL EVAL-AD8332/AD9238 1 LMD2 TP5 C50 0.1µF S3 EIN2 C49 0.1µF L12 120nH FB 2 INH2 INH1 TP6 L13 C60 120nH FB 0.1µF 27 S1 EIN1 C79 22 pF 3 5VLNA VPS2 TB1 5V VPS1 C74 1nF C41 0.1µF RFB2 274Ω + TB2 GND C70 0.1µF AD8332ARU 5V TP4 (BLACK) 28 C80 22pF CFB2 18nF TP3 (RED) LMD1 L7 120nH FB CFB1 18nF 5VLNA RFB1 274Ω 4 C46 1µF 26 25 LON2 LON1 LOP2 LOP1 5 5VGA 24 L6 120nH FB C51 0.1µF 5VLNA 6 C53 0.1µF C42 0.1µF 23 COM2 C59 0.1µF COM1 0.1µF 7 VREF 3 7 22 VIP2 VIP1 VIN2 VIN1 U8 AD8541 2 21 8 4 JP13 VCM1 C71 1nF C48 0.1µF JP14 C78 1nF VCM1 9 VCM2 R22 1kΩ VCM1 5VGA 10 TP7 GND C69 0.1µF C83 1nF JP8 18 CLMP ENB VOH2 VOH1 17 C66 VIN – B L20 (0Ω) C67 C55 0.1µF L10 120nH FB JP12 L18 (0Ω) JP7 R26 100Ω COMPONENTS IN GRAY ARE NOT INSTALLED R24 100Ω R27 100Ω L11 120nH FB ENABLE JP16 DISABLE C68 1nF C54 0.1µF LO GAIN 5VGA 12 OPTIONAL 4 POLE LOW PASS FILTER L19 L17 (0Ω) (0Ω) JP15 HILO 11 R3 (RCLMP) HI GAIN 19 GAIN TP2 GAIN VIN + B C43 0.1µF C77 1nF VCM 16 13 VOL2 VOL1 COM VPSV 14 L9 120nH FB 15 5VGA C45 0.1µF C85 1nF L8 120nF FB JP9 C58 0.1µF C56 0.1µF Rev. 0 | Page 4 of 20 L1 (0Ω) JP17 L15 (0Ω) VIN + A C64 C65 L14 (0Ω) R25 100Ω JP10 Figure 3. Schematic—VGA OPTIONAL 4 POLE LOW PASS FILTER L16 (0Ω) VIN – A 05306-003 R23 2kΩ 20 EVAL-AD8332/AD9238 L5 120nH FB 3.3VCLK L4 120nH FB 3.3VADDIG TAB L3 120nH FB + 3.3VADDIG C36 0.1µF C18 1nF C32 C34 0.1µF 10µF 6.3V + C16 R21 1.5kΩ 0.1µF R8 33Ω VIN – B C52 10nF MX_SEL AVDD PDWN_A 61 60 OEB_A REFB_A OTRA_A SENSE REFB_B REFT_B AVDD 13 AGND 14 VIN–_B 15 16 AGND AVDD C19 1nF 54 53 DRGND 51 50 49 DNC TP12 JP4 1 4 VDD OE 3 20MHz 3 GND INT 2 U6 SG-636PCE 12 EXT 2 U5 74VHC04 4 3 U5 74VHC04 1 2 R9 0Ω D1_B TP13 1 U5 74VHC04 5 6 U5 74VHC04 9 8 JP1 DATA CLK INV 48 U5 74VHC04 10 C24 1nF U5 74VHC04 D4_B D5_B Figure 4. Schematic—ADC Rev. 0 | Page 5 of 20 D0_A D0_A DNC DNC 42 DNC DNC DNC 41 DNC DRVDD D0_B DRGND D1_B OTRB_B 40 25 C13 1nF C14 0.1µF + C11 10µF 6.3V 39 26 D2_B D11_B(MSB) OTR_B 38 D11_B 37 D10_B D10_B 36 DRVDD D3_B D1_A D1_A 29 C26 0.1µF D2_A D2_A 28 2 3.3VADDIG COMPONENTS IN GRAY ARE NOT INSTALLED D2_B D3_A D3_A 24 27 D4_A D4_A 23 DRGND DEL SPARES D0_B D5_A D5_A 43 OEB_B DNC D6_A D6_A 44 PDWN_B ADCLK D7_A D7_A 22 ADCLK C25 1nF 45 DFS C86 0.1µF C23 0.1µF DRVDD 46 DCS 21 3.3VADDIG 52 47 CLK_B R41 4.7kΩ D8_A D8_A 19 20 D9_A D9_A 18 JP11 D10_A D10_A 55 11 R19 499Ω R20 4.7kΩ D11_A 56 10 C15 1nF 3.3VADDIG OTR_A VREF D11_A(MSB) C39 0.1µF R15 0Ω 57 9 C12 10µF 6.3V R14 4.7kΩ 58 7 + N ADCLK 59 REFT_A VIN+_B C20 0.1µF R16 5kΩ + 11 AGND 17 R18 499Ω JP3 13 SH_REF 8 R7 33Ω 3.3VCLK 3.3VCLK VIN–_A R11 100Ω JP2 SHARED REF Y R10 63 0Ω 62 6 C40 0.1µF C62 18pF VIN + B C47 10µF 6.3V CLK_A 12 R13 1.5kΩ R17 49.9Ω VIN+_A 5 C37 0.1µF S2 C63 EXT CLOCK 0.1µF AVDD 4 TP9 VREF 3.3VDVDD C38 0.1µF C1 0.1µF AGND 3 C17 0.1µF C33 10µF 6.3V C35 0.1µF C29 0.1µF L2 120nH FB R4 1.5kΩ 64 1 C61 18pF R6 33Ω R12 1.5kΩ + 2 VIN – A C30 0.1µF OUT C2 10µF 6.3V R5 33Ω VIN + A C31 0.1µF C21 1nF D9_B D9_B 35 30 D3_B D8_B D8_B 34 31 D4_B D7_B D7_B 33 32 D5_B D6_B D6_B 05306-004 1 2 3 IN OUT GND + C20 0.1µF U1 A/D CONVERTER AD9238 3.3VAVDD VR1 ADP3339AKC-3.3 C44 1µF 5V + EVAL-AD8332/AD9238 1 G1 19 OTR_A D11_A D10_A D9_A D8_A D7_A D6_A 22 × 4 8 2 7 3 3 6 4 4 5 5 1 2 RP9 2 22 × 4 8 RP10 7 3 6 8 4 5 9 1 6 7 G2 GND A1 Y1 A2 Y2 A3 Y3 A4 Y4 A5 Y5 3.3VDVDD 20 VCC 10 C3 0.1µF + 18 C28 10µF 6.3V D5_A D4_A D3_A D2_A D1_A D0_A DNC DNC 1 22 × 4 RP11 8 7 3 3 6 4 4 5 2 5 22 × 4 8 RP12 7 3 6 8 4 5 9 2 1 6 7 3 7 5 2 16 3 6 8 7 15 4 5 10 9 8 12 11 7 14 13 12 3 6 16 U10 11 A8 74VHC541 Y8 4 5 18 8 20 7 22 3 6 24 4 5 26 8 28 7 30 3 6 32 31 4 5 34 33 36 35 38 37 40 39 A6 Y6 A7 Y7 G2 2 1 4 6 1 22 × 4 2 RP2 G1 19 RP1 2 8 17 14 1 22 × 4 2 RP3 3.3VDVDD 1 1 22 × 4 20 VCC Y1 A2 Y2 A3 Y3 A4 Y4 A5 Y5 A6 Y6 C10 0.1µF 10 GND A1 C76 10µF 6.3V + C8 0.1µF 1 22 × 4 2 RP4 18 17 16 15 HEADER UP MALE NO SHROUD DATACLKA 13 15 17 19 21 23 25 27 29 SAM080UPM 14 13 12 U7 11 A8 74VHC541 Y8 A7 Y7 3.3VDVDD OTR_B D11_B D10_B D9_B D8_B D7_B D6_B D5_B 2 RP13 19 8 7 2 3 6 3 4 5 4 8 5 7 6 3 6 7 4 5 8 1 22 × 4 8 9 1 22 × 4 2 RP14 VCC G2 GND A1 Y1 A2 Y2 20 C7 0.1µF + 10 C9 1µF + C27 10µF 6.3V 18 D4_B D3_B D2_B D1_B D0_B DNC DNC 2 7 6 3 4 5 4 1 22 × 4 8 5 RP16 7 6 3 6 7 4 5 8 2 9 DATACLK 47 3 6 50 49 15 4 5 52 51 14 1 22 × 4 8 54 13 2 RP6 7 56 12 3 6 58 U2 11 A8 74VHC541 Y8 4 5 60 A3 Y3 A4 Y4 A5 Y5 A6 Y6 A7 Y7 G2 3 45 48 2 G1 2 43 46 16 RP15 19 RP5 8 41 44 17 3.3VDVDD 1 1 22 × 4 42 C4 C5 C6 C75 0.1µF 0.1µF 0.1µF 10µF 20 VCC + 6.3V 10 GND A1 Y1 A2 Y2 A3 Y3 A4 Y4 A5 Y5 A6 Y6 1 22 × 4 8 62 2 RP7 7 64 3 6 66 4 5 68 53 55 57 59 61 63 65 67 1 22 × 4 8 70 2 RP8 7 72 71 3 6 74 73 4 5 76 75 78 77 80 79 18 17 16 69 SAM080UPM 15 14 13 12 U3 11 A8 74VHC541 Y8 A7 7 R39 22Ω Y7 Figure 5. Schematic—Interface Rev. 0 | Page 6 of 20 05306-005 1 22 × 4 G1 HEADER UP MALE NO SHROUD 1 EVAL-AD8332/AD9238 OPERATION EQUIPMENT NEEDED Power supplies—5 V and 3.3 V dc; high speed ADC FIFO evaluation kit; personal computer running Windows 95 or later, analog signal source and low pass filter; and reference supply for Vgain. INITIAL SETUP Table 1 lists the jumper and test-point functions for the VGA and ADC. Because the FIFO board functions as a universal interface for multiple ADC part numbers, it must be configured by jumpers specific for the AD9238. Jumper configurations for printer cable and USB versions are shown separately in Table 2 and Table 3. For a more detailed description of the jumper functions, consult the FIFO data sheet HSC-ADC-EVAL- SC/HSC-ADC-EVAL-DC (or the EVAL-A version), both of which are found on the Analog Devices website. Figure 6 illustrates the setup for operation. The EVAL-AD8332/ AD9238 is connected to either an HSC-ADC-EVAL-DC or HSC-ADC-EVALA-DC by mating 80 pin headers. The FIFO board connects to a personal computer using a standard parallel port printer cable or USB cable. A mouse is highly recommended if a laptop computer is used. A CD ROM of ADC Analyzer, an interactive program that operates the converters and processes the recovered data, is provided with both FIFOs. Refer to the FIFO data sheet for details on loading and operating the software. The system requires +5 V and +3 V 0.5 A supplies. Table 1. AD8332/AD9238 Jumpers Jumper 1 2 3 4 7 8 9 10 11 13 14 15 16 Function Data clock—delayed or inverted Select shared reference (Yes or No) Duty cycle stabilizer Select internal or external clock DC couple low output of Channel 2 DC couple high output of Channel 2 DC couple high output of Channel 1 DC couple low output of Channel 1 Data format—inserted twos complement; removed offset binary Connects VCM input of Channel 1 to VCM input of Channel 2 Connects optional VCM amplifier to VCM inputs High or low gain select Enable or disable the AD8332 Configuration Left position (inverted) Left position (Yes) Not inserted Internal selected (toward bottom of board) Not inserted Not inserted Not inserted Not inserted Not inserted Not inserted Not inserted High gain Enable Table 2. FIFO Board Jumper List—Printer Cable (Ref) Jumper 1 2 3 4 5 6 7 8 9 10 11 Configuration Unused Unused Installed Upper position Position 3 Position 3 Lower position Installed Installed Installed Installed Jumper 12 13 14 15 16 17 18 19 20 21 22 Configuration Installed Installed Installed Installed Right position Unused Left position Installed Installed Installed Unused Jumper 23 24 25 26 27 28 29 30 31 32 Rev. 0 | Page 7 of 20 Configuration Unused Installed Unused Unused Unused Unused Unused Unused Installed Left position Jumper 33 34 35 36 37 38 39 40 41 42 Configuration Lower position Installed Installed Installed Installed Installed Installed Installed Installed Installed EVAL-AD8332/AD9238 Table 3. FIFO Jumper List—USB Interface (Ref) Configuration Unused Unused Installed Installed Unused Unused Unused Jumper 202 203 205 206 207 303 304 Configuration Unused Installed Installed Unused Unused Unused Position 3 Jumper 305 306 307 310 311 312 FUNCTION GENERATOR TYPICAL SETTING: 1 MHz, 1V p-p Configuration Position 3 Unused Unused Installed Installed Installed Jumper 313 314 315 401 402 403 Configuration Installed Position 3 Position 1 Position 1 Position 3 Position 1 POWER SUPPLY PRECISION VOLTAGE REFERENCE TYPICAL GAIN SETTING: 1V DC WINDOWS BASED PC WITH PARALLEL-PORT PRINTER CONNECTOR ATTENUATOR: FOR SINGLE CHANNEL SET TO 35dB 5V 3.3V LPF 1 LPF 2 (OPTIONAL) SIGNAL INPUT(S) STANDARD PRINTER CABLE SIGNAL SPLITTER. REQUIRED ONLY FOR 2 CHANNEL DRIVE FROM THE SAME SOURCE. AD8332 INPUTS CANNOT BE DIRECTLY CONNECTED INPUT TO ADC SHOULD BE APPROXIMATELY 2V p-p Figure 6. Test Interconnections Rev. 0 | Page 8 of 20 05306-006 Jumper 101 102 103 105 106 107 201 EVAL-AD8332/AD9238 INITIALIZING ANALYZER MENUS After the power and cabling have been set up, the system is ready for initialization. A 1 MHz sine wave input signal is recommended for this trial run. As a sanity check, observe the waveform prior to digitization by probing JP12 and/or JP17 with a differential probe. Adjust generator and attenuator settings for just under 2 V p-p to the ADC. Analyzer displays both channels at once. To view a single VGA channel, remove the input signal from the unused input of the AD8332. For a first test, it’s a good idea to capture a waveform in time domain. Left-click the Time Domain button (Figure 8), and the display appears as in Figure 9. Initiate ADC Analyzer on the computer. When prompted for a configuration file, select AD9238. This file will later require modification and will be saved as AD8332 + AD9238. Figure 8. Time Domain Button 05306-009 Before FFT or time domain information can be displayed correctly, you must configure the software for the hardware and the clock frequency in use. In the upper left toolbar, left-click the Config button, then FFT (the configuration data applies to both the time domain and FFT displays.) In the Encode Frequency (MSPS) box, adjust the MSPS to 20 if the on-board 20 MHz clock is used; otherwise enter the clock frequency of the external clock source being used. In the Averages dialog box, type 10. Clear the Twos Complement check box. Be sure to enter the same Encode Frequency (MSPS) setting to Channel A and Channel B. See Figure 7 for a display of the FFT configuration setup. Save the revised configuration as a new file—i.e., AD8332 + AD9238. Figure 9. Initial Time Domain Display 05306-010 05306-007 The plot appears as a solid red rectangle. This is because it is displaying each of the 16 k samples. To crop the display and observe only a few cycles, left-click and drag the cursor horizontally over a small portion of the waveform. Right-click within the dialog box and a menu drops down. Right-click the upper H-Zoom option, and the display appears as in Figure 10. Figure 7. FFT Configuration Menu Figure 10. Time Domain Waveform Rev. 0 | Page 9 of 20 EVAL-AD8332/AD9238 that is used for the 1 MHz waveforms. A splitter must be used if both LNA channels are driven. Figure 12 and Figure 13 are individual channel FFTs, a useful tool to observe channel isolation. 05306-011 There are six optional FFT displays: single, sequential-single, average, sequential-average, two-tone and sequential-twotone. Figure 11 is a display of an FFT performed on both channels of the AD8332 using the same 1 MHz input signal Figure 11. FFT, Both Channels Rev. 0 | Page 10 of 20 05306-012 EVAL-AD8332/AD9238 05306-013 Figure 12. FFT, Channel 1 Figure 13. FFT, Channel 2 Rev. 0 | Page 11 of 20 EVAL-AD8332/AD9238 PRINTED BOARD LAYOUT 05306-014 Figure 14 through Figure 17 are the copper patterns for the board. Figure 14. Component Side Copper Rev. 0 | Page 12 of 20 05306-015 EVAL-AD8332/AD9238 Figure 15. Layer 2 Copper Rev. 0 | Page 13 of 20 05306-016 EVAL-AD8332/AD9238 Figure 16. Layer 3 Copper Rev. 0 | Page 14 of 20 05306-017 EVAL-AD8332/AD9238 Figure 17. Wiring Side Copper Rev. 0 | Page 15 of 20 05306-018 EVAL-AD8332/AD9238 Figure 18. Component Side Silkscreen Rev. 0 | Page 16 of 20 05306-019 EVAL-AD8332/AD9238 Figure 19. Wiring Side Silkscreen Rev. 0 | Page 17 of 20 EVAL-AD8332/AD9238 ORDERING INFORMATION Table 4. Parts List Qty. 46 Name Capacitor Description 0.1 μF 16 V 0603 Ceramic Tantalum 1 μF 16 V A size 10 nF, 6.3 V, 0201 18 pF, 5%, NPO, 0603 22 pF 50 V 5% 0603 18 nF, 0603 80 Ckt RA Male, 0.1” ctr, 2 row 3 pin, 0.1” ctr 2 pin, 0.1” ctr 5% 1/10 W 0805 0 Ω 120 nH, 0805 1% 1/10 W 0805 1.5k Ω 5% 1/10 W 0805 33 Ω 0 Ω, 5%, 1/10 W, 0805 100 Ω, 5%, 1/10 W, 0805 5% 1/10 W 0805 4.7 kΩ 10 kΩ 3/8" SQ 49.9 Ω, 1%, 1/10 W, 0805 499 Ω, 1%, 1/10 W, 0805 1% 1/10 W 0805 1.5 kΩ 22 Ω, 5 %, 1/10 W, 0805 1% 1/10 W 0805 274 Ω 22 Ω Resistor SMA Female PC Mount Block Split Vector Loop, 0.093” dia., Red Loop, 0.093” dia., Black Loop, 0.038” dia., White ADC, 12 bit dual, 65 MSPS Oct. Buffer Dual VGA Hex Inv 20 MHZ 3.3 V Pos. Volt Reg. SOT-223 Reference Designator C1, 3–10, 14, 16, 17, 20, 22, 24, 26, 29–32, 35–43, 45, 48–51, 53–56, 58–60, 63, 69, 70, 72, 86 C2, 11, 12, 27, 28, 33, 34, 47, 75, 76 C13, 15, 18, 19, 21, 23, 25, 68, 74, 77, 78, 83, 85 C44, 46 C52, 57 C61, 62 C79, 80 CFB1, 2 J1 JP1, 2, 4, 15, 16 JP3, 5, 6, 11, 12, 17 Insert in positions L1, 14–20 L2–13 R4, 12, 13, 21 R5–8 R9, 10 (8 @ positions L1, 14–20) R11, 24–27 R14, 20, 41 R16 R17 R18, 19 R4, 12, 13, 21 R39, 40 RFB1, RFB2 RN1–16 S1, 2, 3 TB1 TP1, 2, 7, 8 TP3 TP4 TP5, 6, 9, 12, 13 U1 U2, 3, 7, 10 U4 U5 U6 VR1 10 12 Capacitor Capacitor Tantalum 10 μF 6.3 V A size 1 nF 50 V 0603 2 2 2 2 2 1 5 6 8 12 4 4 10 5 3 1 1 2 4 2 2 16 3 1 4 1 1 5 1 4 1 1 1 1 1 4 4 5 1 Capacitor Capacitor Capacitor Capacitor Capacitor Header Header Header Resistor Ferrite Bead Resistor Resistor Resistor Resistor Resistor Trimmer Resistor Resistor Resistor Resistor Resistor Network Connector Terminal Test Pin Test Pin Test Pin Test Pin IC IC IC IC Clock IC, Volt Reg. PC Board Hardware Hardware Jumper Standoff 4–40 x 1/2” alum. Screw 4–40 x 1/4” SS Mini-jump jumper Socket conn. strip Install at JP1, 2, 4, 15, 16 Part of TB1 Rev. 0 | Page 18 of 20 Manufacturer Kemet Manufacturer Part No. C0603C104K4RAC Panasonic Panasonic ECS-T0JY106R ECU-V1H102KBV Kemet Panasonic Panasonic Panasonic Panasonic Molex Molex Mill Max Panasonic Murata Panasonic Panasonic Panasonic Panasonic Panasonic BOURNS Panasonic Panasonic Panasonic Panasonic Panasonic CTS Linx Wieland Vector Bisco Bisco Bisco Analog Devices Fairchild Analog Devices Fairchild Epson Analog Devices T491A105K016AS ECJ-ZEB0J103K ECJ-1VC1H180J ECJ-1VC1H220J ECJ-1VB1E183K 10-89-1806 22-10-2031 400-10-002-10-001 ERJ-6ENF0.0 BLM21BB750SN1 ERJ-6ENF1501V ERJ-6GEYJ330V ERJ-6GEY0R00V ERJ-6GEYJ101V ERJ-6GEYJ472V 3299W-103 6ENF49R9V ERJ-6ENF4990V ERJ-6ENF1501V ERJ-6GEYJ220V ERJ-6ENF2740V 742C083220JTR CONREVSMA001 25.602.2253.0 K24A TP-104-01-02 TP-104-01-00 TP-105-01-09 AD9238BST-65 74VHC541M AD8332ARU 74VHC04MTCX SG-636PCE 20.0000MC0 ADP3339AKC-3.3 FCI Wieland 65474-001 Z5.530.0225.0 EVAL-AD8332/AD9238 ORDERING GUIDE Model EVAL-AD8332/AD9238 Description Evaluation Board ESD CAUTION ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality. Rev. 0 | Page 19 of 20 EVAL-AD8332/AD9238 NOTES © 2005 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. EB05306–0–1/05(0) Rev. 0 | Page 20 of 20