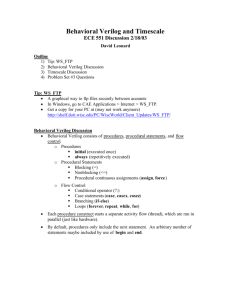

DRAFT Summary of Key Verilog Features (IEEE 1364) Module Three-State Multioutput Primitives

advertisement

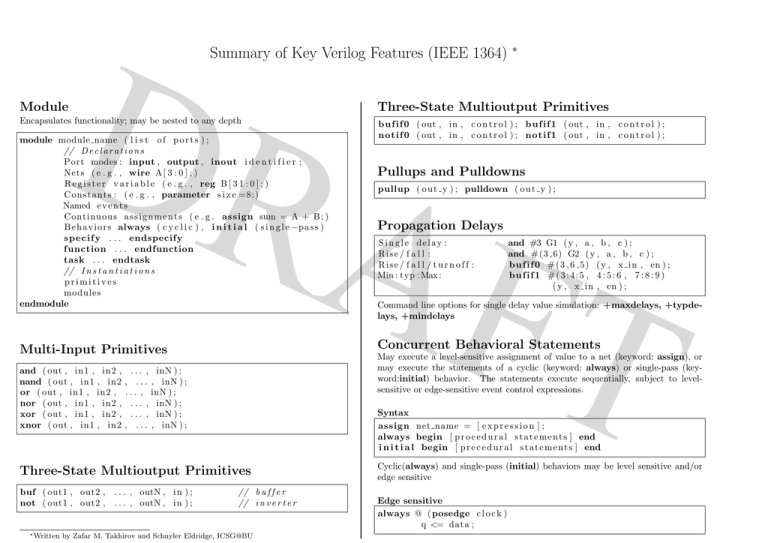

Summary of Key Verilog Features (IEEE 1364)

DR

∗

Module

Three-State Multioutput Primitives

Encapsulates functionality; may be nested to any depth

b u f i f 0 ( out , in , c o n t r o l ) ; b u f i f 1 ( out , in , c o n t r o l ) ;

n oti f0 ( out , in , c o n t r o l ) ; n oti f1 ( out , in , c o n t r o l ) ;

module module name ( l i s t o f p o r t s ) ;

// D e c l a r a t i o n s

Port modes : input , output , inout i d e n t i f i e r ;

Nets ( e . g . , wire A [ 3 : 0 ] ; )

R e g i s t e r v a r i a b l e ( e . g . , reg B [ 3 1 : 0 ] ; )

C on s t an t s : ( e . g . , parameter s i z e =8;)

Named e v e n t s

Continuous a s s i g n m e n t s ( e . g . assign sum = A + B ; )

B e h a v i o r s always ( c y c l i c ) , i n i t i a l ( s i n g l e −p a s s )

sp eci fy . . . endspecify

function . . . endfunction

task . . . endtask

// I n s t a n t i a t i o n s

primitives

modules

endmodule

AF

Single delay :

Rise / f a l l :

Rise / f a l l / t u r n o f f :

Min : typ : Max :

and #3 G1 ( y , a , b , c ) ;

and #(3 ,6) G2 ( y , a , b , c ) ;

b u f i f 0 # ( 3 , 6 , 5 ) ( y , x i n , en ) ;

bufif1 #(3:4:5 , 4 : 5 : 6 , 7 : 8 : 9 )

( y , x i n , en ) ;

T

Command line options for single delay value simulation: +maxdelays, +typdelays, +mindelays

Syntax

assign net name = [ e x p r e s s i o n ] ;

always begin [ p r o c e d u r a l s t a t e m e n t s ] end

i n i t i a l begin [ p r e c e d u r a l s t a t e m e n t s ] end

Three-State Multioutput Primitives

∗ Written

Propagation Delays

May execute a level-sensitive assignment of value to a net (keyword: assign), or

may execute the statements of a cyclic (keyword: always) or single-pass (keyword:initial) behavior. The statements execute sequentially, subject to levelsensitive or edge-sensitive event control expressions.

. . . , inN ) ;

, . . . , inN ) ;

. . . , inN ) ;

. . . , inN ) ;

. . . , inN ) ;

, . . . , inN ) ;

buf ( out1 , out2 , . . . , outN , i n ) ;

not ( out1 , out2 , . . . , outN , i n ) ;

pullup ( o u t y ) ; pulldown ( o u t y ) ;

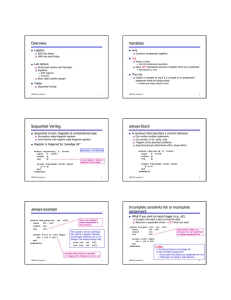

Concurrent Behavioral Statements

Multi-Input Primitives

and ( out , in1 , in2 ,

nand ( out , in1 , in2

or ( out , in1 , in2 ,

nor ( out , in1 , in2 ,

xor ( out , in1 , in2 ,

xnor ( out , in1 , in2

Pullups and Pulldowns

// b u f f e r

// i n v e r t e r

by Zafar M. Takhirov and Schuyler Eldridge, ICSG@BU

Cyclic(always) and single-pass (initial) behaviors may be level sensitive and/or

edge sensitive

Edge sensitive

always @ ( posedge c l o c k )

q <= data ;

Assignments

Level sensitive

always @ ( e n a b l e or data )

q <= data ;

DR

Data Types: Nets and Registers

Nets: Establish structural connectivity between instantiated primitives and/or

modules; may be target of a continuous assignment; e.g., wire, tri, wand, wor.

Value is determined during simulation by the driver of the net; e.g., a primitive or

a continuous assignment.

Example:

wire Y = A + B ;

Procedural Statements

Operators

AF

Registers: Store information and retain value until reassigned.

Value is determined by an assignment made by a procedural statement.

Value is retained until a new assignment is made; e.g., reg, integer, real, realtime, time.

Example:

always @ ( p o s e g e c l o c k )

i f ( r e s e t ) q o u t <= 0 ;

e l s e q o u t <= d a t a i n ;

Continuous: Continuously assigns the value of an expression to a net.

Procedural (Blocking): Uses the = operator; executes statements sequentially;

a statement cannot execute until the preceding statement completes execution.

Value is assigned immediately.

Procedural (Nonblocking): Uses the ¡= operator; executes statements concurrently, independent of the order in which they are listed. Values are assigned

concurrently.

Procedural (Continuous):

assign ... deassign overrides procedural assignments to a net.

force ... release overrides all other assignments to a net or a register

Describe logic abstractly; statements execute sequentially to assign value to variables.

i f ( e x p r e s s i o n i s t r u e ) statement 1 ; else statement 2 ;

case ( c a s e e x p r e s s i o n )

case item 0 : statement 0 ;

c a s e i t e m 1 : begin

statement 1 0 ;

statement 1 1 ;

end

default : s t a t e m e n t ;

endcase

f or ( c o n d i t i o n s ) s t a t e m e n t ;

repeat c o n s t a n t e x p r e s s i o n s t a t e m e n t ;

while ( e x p r e s s i o n i s t r u e ) s t a t e m e n t ;

forever s t a t e m e n t ;

fork s t a t e m e n t s j o i n // e x e c u t e i n p a r a l l e l

{} {{}}

+-*/

%

>≥<≤

!

&&

||

==

!=

===

!==

∼

&

concatenation

arithmetic

modulus

relational

logical negation

logical and

logical or

logical equality

logical inequality

case equality

case inequality

bitwise negation

bitwise and

|

ˆ

ˆ∼ or ∼ˆ

&

&

|

∼|

ˆ

ˆ∼ or ∼ˆ

?:

or

Specify Block

bitwise or

bitwise exclusive-or

bitwise equivalence

reduction and

reduction nand

reduction or

reduction nor

reduction exclusive-or

reduction exclusive-nor

left shift

right shift

conditional

event or

T

Example: Module Path Delays

sp eci fy

// specparam d e c l a r a t i o n s ( min : t y p : max)

specparam t r = 3 : 4 : 5 , t f = 4 : 5 : 6 ;

( (A, B) ∗> Y) = ( t r , t f ) ;

// f u l l

( Bus 1 => Bus 1 ) = ( t r , t f ) ; // p a r a l l e l

i f ( s t a t e == S0 ) ( a , b ∗> y ) = 2 ;

// s t a t e dep

( posedge c l k => ( y −: d i n ) ) = ( 3 , 4 ) ;

// e d g e

endspecify

Example: Timing Checks

sp eci fy

specparam t s e t u p = 3 : 4 : 5 , t h o l d = 4 : 5 : 6 ;

$ s e t u p ( data , posedge c l o c k , t s e t u p ) ;

$ h o l d ( posedge c l o c k , data , t h o l d ) ;

endspecify

Memory

end

Declares an array of words.

endcase

DR

Example: Memory declaration and readout

module m e m o r y r e a d d i s p l a y ( ) ;

reg [ 3 1 : 0 ] mem array [ 1 : 1 0 2 4 ] ;

integer k ;

i n i t i a l begin

// r ead c o n t e n t s o f mem array from

// a f i l e i n hex f o r m a t

$readmemh ( ” mem contents . dat ” , mem array ) ;

// d i s p l a y c o n t e n t s o f mem array

f or ( k = 1 ; k <= 1 0 2 4 ; k = k + 1 )

$display ( ”word[%d]=%h” , k ,

mem array [ k ] ) ;

end

endmodule

Concurrency and Race Conditions

always @ ( posedge c l o c k ) a = b ;

always @ ( posedge c l o c k ) b = a ;

always @ ( posedge c l o c k ) a <= b ;

always @ ( posedge c l o c k ) b <= a ;

Use the procedural assignment operator (=) in level-sensitive behaviors and the

nonblocking assignment operator (<=) in edge-sensitive behaviors to avoid race

conditions in sequential machines.

v a l u e = adder ( a , b ) ;

...

function [ 4 : 0 ] adder ;

input [ 3 : 0 ] a , b ;

adder = a + b ;

endfunction

Tasks

Example:

adder ( sum , a , b ) ;

...

task adder ;

output [ 4 : 0 ] sum ;

input [ 3 : 0 ] a , b ;

sum = a + b ;

endtask

T

Selected Compiler Directives

Example (without race):

always @ ( posedge c l o c k )

s t a t e <= n e x t s t a t e ;

always @ ( s t a t e or i n p u t s )

case ( s t a t e )

s t a t e 0 : begin n e x t s t a t e = s t a t e 5 ;

Example:

May invoke other tasks and other functions.

May contain delay control(#), event control (@), and wait.

May have zero or more arguments having mode input, output, inout.

Passes values by its arguments.

Use nonblocking assignment operator (<=) to eliminate race conditions; assignments are independent of the order of the behaviors and the order of the statements.

Example:

May invoke another function; may not invoke a task. Executes with zero delay

time.

May not contain delay control (#), event control (@), or wait.

Must have at least one input argument.

May not have output or input arguments.

Function name serves as a placeholder for a single returned value.

AF

Indeterminate outcomes result from race conditions when multiple behaviors use

the procedural assignment operator (=) to reference (read) and assign value to teh

same variable at the same time.

Example (with race):

Functions

‘ d e f i n e width = 1 6 ;

‘include . . . / p r o j e c t h e a d e r . v

‘timescale = 100 ns /1 ns // t i m e u n i t s / p r e c i s i o n

‘ i f d e f . . . ‘else . . . ‘endif

...

Example:

// t e r m i n a t e s i m u l a t i o n a f t e r 1000 time u n i t s :

#1000 $ f i n i s h ;

module o r m o d e l ( y , a , b ) ;

output y ;

input a , b ;

‘ifdef cont assign

// u s e s c o n t i n u o u s a s s i g n m e n t

assign y = a | b ;

‘else

or G1 ( y , a , b ) ; // u s e s p r i m i t i v e

‘endif

endmodule

DR

end

Simulation Output

Parameter Redefinition

In-line (instance-based)

AF

$display ( ” s t r i n g o f i n f o %d” , v a r i a b l e ) ;

integer K;

i n i t i a l K = $fopen ( ” o u t p u t f i l e ” ) ;

always @ ( e v e n t c o n t r o l e x p r e s s i o n ) // dump d a t a

begin

$fdisplay (K, ”%h” ’ , data [ 7 : 0 ] ) ;

...

$fclose ( ” o u t p u t f i l e ” ) ;

$monitor ( $time , ” o u t 1=%b , o u t 2=%b” , out 1 , o u t 2 ) ;

$monitor (K, ” s o m e v a l u e=%h” , a d d r e s s [ 1 5 : 0 ] ) ;

$monitoron ;

$monitoroff ;

end

Simulation Data Control

i n i t i a l begin

// dump s i m u l a t i o n d a t a i n t o my data . dump :

$ d u m p f i l e ( ” my data . dump” ) ;

// dump a l l s i g n a l s :

$dumpvars ;

// dump v a r i a b l e s i n module t o p :

$dumpvars ( 1 , top ) ;

// dump v a r i a b l e s 2 l e v e l s b e l o w t o p . mod1 :

$dumpvars ( 2 , top . mod1 ) ;

// s t o p dump a f t e r 1000 time u n i t s :

#1000 $dumpoff ;

// s t a r t / r e s t a r t dump a f t e r 500 time u n i t s :

#500 $dumpon ;

// s u s p e n d s i m u l a t i o n :

$stop ;

module Something ( ) ;

parameter s i z e = 4 ;

parameter width = 8 ;

...

endmodule

...

Something #(8 ,32) M1 ( ) ;

...

Indirect (hierarchical dereferencing):

module Annotate ( ) ;

...

defparam . Something . width = 1 6 ;

...

endmodule

T

Constructs to Avoid in Synthesis

•

•

•

•

•

•

•

•

•

•

•

•

•

•

time, real, realtime variables

named event

triand, trior, tri0, tri1 nets

vector ranges for integers

single-pass (initial) behavior

assign ... deassign procedural continuous assignment

force ... release procedural continuous assignment

fork ... join block (parallel activity flow)

defparam parameter substitution

Operators: Modulus(%) and Division(/), except for division by 2

===, !===

Primitives: pullup, pulldown, tranif0, tranif1, rtran, rtranif0, rtranif1

Hierarchical pathnames

Compiler directives

This material is used while creating the current document:

1. IEEE 1364 Verilog-2001 Standard description.

2. ”Advanced Digital Design with the Verilog HDL” by Michael D.

Ciletti