128-Channel Digital X-Ray Analog Front End AD8488 Data Sheet

advertisement

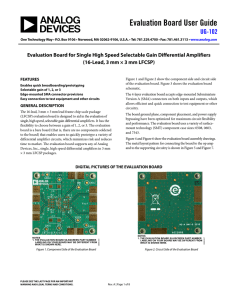

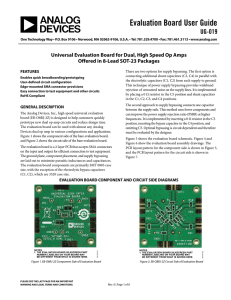

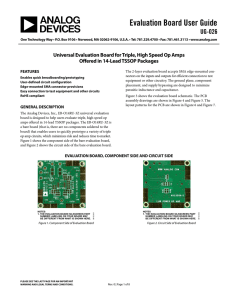

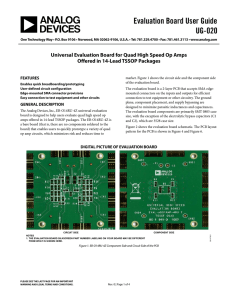

128-Channel Digital X-Ray Analog Front End AD8488 Data Sheet FEATURES GENERAL DESCRIPTION 128 integrator channels Correlated double sample error correction (CDS) Corrects for VOS and LF noise Power consumption per channel Normal: 11 mW Low power: 4 mW Low input leakage current: −1.5 pA typical Low input referred noise (QNI): 993 e−rms typical Linearity error: 0.03% typical Compact 17 mm × 17 mm BGA Selectable filter time constants 4 selectable input charge ranges 10 selectable gain ranges The AD8488 is a 128-channel, analog front end (AFE) designed for use in high performance digital X-ray systems. The analog channels consist of an integrator followed by a gain selectable single-ended to low impedance differential output. The analog channel converts the charge acquired by X-ray or photodiode detectors to a voltage. The channels are composed of CMOS transistors, using typical high input impedance CMOS gates. The integrators generate charge dependent voltages using a range of selectable capacitance values that accommodate a broad range of input charge values. The integrators are followed by single-ended input to differential output voltage amplifiers where offset and low frequency noise voltages are subtracted from the input voltages. A 128:1 channel differential MUX follows the buffers and drives the analog output buffer. Switch drivers and certain digital timing functions are included, and all are mounted on a 255-lead BGA substrate. Charge conversion for all 128 channels is simultaneous followed by a sequential voltage output read of the channels using a 7-bit address code. The sequence occurs twice, sampling all 128 channels. Logic control inputs, CS_A and CS_B, select the lower and upper 64 blocks of the channel addresses. APPLICATION High performance digital X-ray systems Medical X-ray Security (baggage scanner) systems The AD8488 is packaged in a 17 mm × 17 mm, 255-lead, RoHScompliant ball grid array (BGA). The operating temperature range is 0°C to 85°C ambient. FUNCTIONAL BLOCK DIAGRAM OUTPUT BUFFER CHARGE CONVERSION AMPLIFIER 128 CHANNELS DIFFERENTIAL OUTPUT MULTIPLEXER IN0:127 LPF GAIN AMPLIFIER 128 TIMING AND CONTROL 7 MUX SELECTOR CONTROL REGISTER CK_ENb CLK 09801-001 CONTROL SIGNALS TST RSTB 7 WRB 2 FSEL0, FSEL1 4 TST0 TO TST6 CSB_a, CSB_b CF1SEL0, CF1SEL1 2 TIMING SIGNALS GNSEL0 TO GNSEL3 HOLD GRST IRST PWR VREF OUTHI OUTLO 128:1 ANALOG INPUTS CK_ENa INT INT Figure 1. Rev. A Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©2012 Analog Devices, Inc. All rights reserved. AD8488 Data Sheet TABLE OF CONTENTS Features ...................................................................................................1 Typical Performance Characteristics ................................................ 11 Application .............................................................................................1 Theory of Operation ........................................................................... 13 General Description ..............................................................................1 Overview .......................................................................................... 13 Functional Block Diagram ...................................................................1 Analog Amplifier ........................................................................ 13 Table of Contents ...................................................................................2 Troubleshooting Channels ......................................................... 13 Revision History ....................................................................................2 Timing Signals ................................................................................. 14 Specifications..........................................................................................3 Timing Notes ............................................................................... 14 Absolute Maximum Ratings .................................................................5 Applications Information ................................................................... 15 Thermal Data .....................................................................................5 Control Register Bit Maps .............................................................. 15 Thermal Characterization ................................................................5 Timing Diagrams ............................................................................ 17 ESD Caution .......................................................................................5 Outline Dimensions ............................................................................ 18 Pin Configuration and Function Descriptions ..................................6 Ordering Guide ............................................................................... 18 Signal Mnemonics .................................................................................9 REVISION HISTORY 6/12—Revision A: Initial Version Rev. A| Page 2 of 20 Data Sheet AD8488 SPECIFICATIONS Default test conditions, unless otherwise specified: VDD = 5 V, VCC = 5 V, LPF resistor (R1) = 130 kΩ, base panel temperature = 30°C, Pin PWR = logic low, G = 1 V/V, CH = 0.5 pF, and CPANEL = 38 pF. Table 1. Parameter INPUT LEAKAGE CURRENT CHARGE CONVERSION RATE 1 GAIN CHARACTERISTICS Accuracy 2 CF1 = 7 pF Gain Step Error vs. Temperature 3 MAXIMUM INPUT CHARGE Test Conditions/Comments See Figure 16 CF1 = 0.45 pF CF1 = 0.9 pF CF1 = 3.5 pF CF1 = 7 pF G=1 G=2 G=3 G=4 G=5 G=6 G=7 G=8 G=9 G = 10 Linear to 7 pC input charge Min −10 Typ −1.5 Max +10 Unit pA/channel 1.7 0.85 0.21 0.10 2.3 1.1 0.28 0.14 2.9 1.4 0.36 0.18 V/pC V/pC V/pC V/pC 0.98 1.96 2.94 3.92 4.9 5.88 6.86 7.84 8.82 9.8 1 2 3 4 5 6 7 8 9 10 1 0.003 1.02 2.04 3.06 4.08 5.1 6.12 7.14 8.16 9.18 10.2 V/V V/V V/V V/V V/V V/V V/V V/V V/V V/V V/V %/°C CF1 = 0.45 pF CF1 = 0.9 pF CF1 = 3.5 pF CF1 = 7 pF CLOCK Frequency Rise and Fall Time LOGIC INTERFACE Input High Input Low Leakage Current POWER SUPPLY Analog Supply Voltage (AVDD) Quiescent Current (AIDD) Current in Low Power Mode Power Consumption Normal Low Power Digital Supply Voltage (DVDD) Quiescent Current (DIDD) REFERENCE VOLTAGE VREF 0.45 0.9 3.5 7 1 pC pC pC pC 15 6 MHz ns 14.5e−6 1.15 1 V V µA 5 285 90 5.25 350 100 V mA mA WR, CF1SELx, FSELx, GNSELx, HOLD, GRST, IRST, TSTx, CK_ENx, PWR, CS_A, CS_B 3.25 4.75 230 65 Pin PWR logic low Pin PWR logic high Pin PWR logic low Pin PWR logic high 11 4 4.75 5 2 2.048 Rev. A | Page 3 of 20 mW/channel mW/channel 5.25 10 V mA V AD8488 Data Sheet Parameter OUTPUT VOLTAGE OUTHIGH OUTLOW Test Conditions/Comments INPUT REFERRED NOISE 4 Normal Low Power PANEL CAPACITANCE LINEARITY ERROR 5 Normal Low Power OPERATING TEMPERATURE CF1 = 0.9 pF, G = 10 CPANEL = 38 pF CPANEL = 61 pF Min Typ Max Unit 2.0 2.0 V V 993 2000 80 e−rms e−rms pF 85 % + LSB % + LSB °C 0 CF1 = 0.9 pF, G = 5 0.03 + 1 0.2 + 8.2 Ambient, normal and low power 0 Defined as the output voltage divided by the input charge (number of electrons in this case) with the gain amp setting (G = 1). This includes the gain error of the gain amp. Each gain at G = 2, G = 4, G = 8, and G = 10 is calculated as the ratio of each output voltage to that at G = 1. Each measurement corresponds to the selection of each gain setting capacitor. 3 Gain deviation over temperature. 4 The output noise voltage is measured and converted into the input referred noise electrons. 5 It is defined as the deviation from a best fit line, including the origin. The output voltage is measured with five different input conditions. 1 2 Rev. A | Page 4 of 20 Data Sheet AD8488 ABSOLUTE MAXIMUM RATINGS THERMAL CHARACTERIZATION Table 2. Parameter Voltage Supply (AVDD, DVDD) Charge Input IN0 to IN127 Reference (VREF, VREF_ESD) Logic Inputs Maximum Junction Temperature Storage Temperature Range Input Charge to Integrator Channels Rating Table 3. Thermal Resistance—Normal Operation (1.4 W) 5.5 V −0.3 V to VREF + 0.3 V 5.5 V −0.3 V to +5.5 V 125°C −30°C to +150°C 20 pC Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. THERMAL DATA ΨJB is the junction-to-board thermal characterization parameter with a unit of °C/W. The ΨJB of the package is based on modeling and calculation using a 4-layer board. The JESD51-12, Guidelines for Reporting and Using Package Thermal Information, states that thermal characterization parameters are not the same as thermal resistances. ΨJB measures the component power flowing through multiple thermal paths rather than a single path, as in thermal resistance, θJB. Therefore, ΨJB thermal paths include convection from the top of the package as well as radiation from the package, factors that make ΨJB more useful in real-world applications. Maximum junction temperature (TJ) is calculated from the board temperature (TB) and power dissipation (PD) using the formula Airflow Velocity (m/sec) 0 1 3 Ambient 85°C 50°C 25°C 85°C 50°C 25°C 85°C 50°C 25°C θJA 18.6 19.7 20.6 15.8 16.1 16.4 13.8 14.0 14.2 ΨJT 0.20 0.17 0.16 0.32 0.30 0.29 0.54 0.53 0.52 ΨJB 8.3 8.3 8.3 8.2 8.2 8.2 7.7 7.7 7.7 θJC 4.4 4.4 4.4 4.4 4.4 4.4 4.4 4.4 4.4 Unit °C/W °C/W °C/W °C/W °C/W °C/W °C/W °C/W °C/W Table 4. Thermal Resistance—Low Power Operation (0.5 W) Airflow Velocity (m/sec) 0 1 3 Ambient 85°C 50°C 25°C 85°C 50°C 25°C 85°C 50°C 25°C θJA 19.0 20.2 21.2 15.7 16.2 16.4 13.8 14.1 14.2 ΨJT 0.19 0.16 0.15 0.31 0.29 0.28 0.54 0.52 0.51 ΨJB 8.3 8.3 8.3 8.1 8.1 8.1 7.8 7.8 7.8 θJC 4.4 4.4 4.4 4.4 4.4 4.4 4.4 4.4 4.4 Unit °C/W °C/W °C/W °C/W °C/W °C/W °C/W °C/W °C/W Note that the thermal numbers are simulated per JEDEC JESD51-9 on a 4-layer printed circuit board size = 101.5 mm × 114.5 mm. ESD CAUTION TJ = TB + (PD × ΨJB) Refer to JESD51-8 and JESD51-12 for more detailed information about ΨJB. Rev. A | Page 5 of 20 AD8488 Data Sheet PIN CONFIGURATION AND FUNCTION DESCRIPTIONS A1 BALL PAD CORNER NOTE: E12 AND M12 ARE NC ON THE BGA BUT MUST BE CONNECTED TO GROUND ON THE PCB KEY A AVDD B AGND C DGND D DVDD E I/O F DIG I/O G NC H J K L M N P R 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 TOP VIEW Figure 2. 255-Ball CSP_BGA Ball Configuration (Top View) Rev. A | Page 6 of 20 16 09801-002 T Data Sheet AD8488 A1 BALL PAD CORNER NOTE: E12 AND M12 ARE NC ON THE BGA BUT MUST BE CONNECTED TO GROUND ON THE PCB A B C D E F KEY G AVDD H AGND J DGND K L DVDD M I/O N DIG I/O NC P R 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 BOTTOM VIEW 09801-003 T Figure 3. 255-Ball CSP_BGA Ball Configuration (Bottom View) Table 5. Pin Function Descriptions Mnemonic AGND AVDD Pin No. See Table 6 and Table 7 F6, F7, F8, F9, F10, G6, G11, H6, H11, H12, J6, J11, K6, K11, L6, L8, L9, L10, L11 D15 E14 F14 N14 M15 B15, C15 I/O O I Description Analog Power Ground (0 V). Analog Supply Voltage (5 V). I I I I I I F16, G15, G16, H15, H16, J15, J16, K15, K16, L16 B16, C16, D16, E16, F15, L15, M16, N16, P16, R16 R14, T14 A14, B14, C14, D14 O I I I GRST H14 I HOLD T16 I Clock for Mux Operation. Clock Gate for Channel 0 to Channel 63. Clock Gate for Channel 64 to Channel 127. Logic Level to Enable Channel 0 to Channel 63. Logic Level to Enable Channel 64 to Channel 127. Binary Coded Logic Pins to Select One of Four Values of Integrator Capacitor CF1 (see Table 9). Digital Ground (0 V). Power Supply for Digital Circuit (5 V). Filter Time Constant Select (see Table 10). Gain Select for the Gain Amp. Select one of four hold capacitors. The four values are arranged in one of ten parallel options to establish ten gain values (see Table 11). Gain Amp Reset. Closes the switch across Integrator Capacitor CF2 setting the output of the gain amplifier to zero. Gain Amp Hold. Connect the hold capacitor to the signal chain. CLK CK_ENa CK_ENb CS_A CS_B CF1SEL0, CF1SEL1 DGND DVDD FSEL0, FSEL1 GNSEL0 to GNSEL3 Rev. A | Page 7 of 20 AD8488 Data Sheet Mnemonic IN0 to IN127 IRST Pin No. See Table 6 and Table 7 E15 I/O I I NC OUTLOW OUTHIGH PWR A13, A15, B13, C13, D13, E10, E12, E13, F11, F13, G13, H13, J12, J13, K13, L13, M12, M13, N13, P13, R13, T13 F12 G12 P14 Description Analog Inputs. Integrator Reset. Closes a switch across the integration capacitor, CF1, to set the output to zero. No connect. Connect these pins to GND on the PCB. O O I RST TST_MODE A16 J14 I I TST0 to TST6 VREF VREF_ESD WR T15, R15, P15, N15, M14, L14, K14 L12 K12 G14 I I I I Inverting Analog Output (Negative) of the Differential Output. Noninverting Analog Output (Positive) of the Differential Output. Normal state is logic low; reduces analog bias current by approximately 80% when high. Reset Gray Mode Counter for Mux. Test Mode Enable. This control line is used together with the TST0 to TST6 address bits to test or debug a system by continuously selecting a channel. Channel Address Select Bits When in Test Mode (see Table 8). Reference Input for Analog Circuit (2.048 V). ESD Reference. Connect to VREF (2.048 V). Write Digital Instruction Word to the AFE. Rev. A | Page 8 of 20 Data Sheet AD8488 SIGNAL MNEMONICS Table 6. 255-Ball CSP_BGA Ball Assignment (Numerically by Ball Number) Ball A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 Signal IN108 IN107 IN106 IN80 IN84 IN110 IN111 IN112 IN115 IN119 IN124 NC GNSEL3 NC RST IN103 IN102 IN101 IN100 IN99 IN98 IN105 IN104 IN113 IN116 IN120 IN125 NC GNSEL2 CF1SEL1 DVDD IN97 IN96 IN95 IN94 IN93 IN92 IN81 IN74 IN114 IN117 IN121 IN127 NC Ball C14 C15 C16 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 E1 E2 E3 E4 E5 E6 E7 E8 E9 E10 E11 E12 E13 E14 E15 E16 F1 F2 F3 F4 F5 F6 F7 F8 F9 Signal GNSEL1 CF1SEL0 DVDD IN91 IN90 IN89 IN88 IN87 IN86 IN85 IN83 IN118 IN109 IN123 IN126 NC GNSEL0 CLK DVDD IN75 IN69 IN68 IN82 AGND AGND AGND AGND AGND NC IN122 NC NC CK_ENa IRST DVDD IN79 IN78 IN77 IN76 AGND AVDD AVDD AVDD AVDD Ball F10 F11 F12 F13 F14 F15 F16 G1 G2 G3 G4 G5 G6 G7 G8 G9 G10 G11 G12 G13 G14 G15 G16 H1 H2 H3 H4 H5 H6 H7 H8 H9 H10 H11 H12 H13 H14 H15 H16 J1 J2 J3 J4 J5 Signal AVDD NC OUTLOW NC CK_ENb DVDD DGND IN73 IN72 IN71 IN70 AGND AVDD AGND AGND AGND AGND AVDD OUTHIGH NC WR DGND DGND IN67 IN66 IN65 IN64 AGND AVDD AGND AGND AGND AGND AVDD AVDD NC GRST DGND DGND IN63 IN62 IN61 IN60 AGND Ball J6 J7 J8 J9 J10 J11 J12 J13 J14 J15 J16 K1 K2 K3 K4 K5 K6 K7 K8 K9 K10 K11 K12 K13 K14 K15 K16 L1 L2 L3 L4 L5 L6 L7 L8 L9 L10 L11 L12 L13 L14 L15 L16 M1 Rev. A | Page 9 of 20 Signal AVDD AGND AGND AGND AGND AVDD NC NC TST_MODE DGND DGND IN59 IN58 IN57 IN56 AGND AVDD AGND AGND AGND AGND AVDD VREF_ESD NC TST6 DGND DGND IN55 IN54 IN53 IN52 AGND AVDD AGND AVDD AVDD AVDD AVDD VREF NC TST5 DVDD DGND IN47 Ball M2 M3 M4 M5 M6 M7 M8 M9 M10 M11 M12 M13 M14 M15 M16 N1 N2 N3 N4 N5 N6 N7 N8 N9 N10 N11 N12 N13 N14 N15 N16 P1 P2 P3 P4 P5 P6 P7 P8 P9 P10 P11 P12 P13 Signal IN50 IN49 IN48 AGND AGND AGND AGND AGND AGND AGND NC NC TST4 CS_B DVDD IN41 IN46 IN45 IN44 IN43 IN42 IN51 IN32 IN40 IN33 IN0 IN9 NC CS_A TST3 DVDD IN31 IN39 IN37 IN38 IN36 IN35 IN34 IN24 IN14 IN12 IN1 IN7 NC Ball P14 P15 P16 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 R14 R15 R16 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 Signal PWR TST2 DVDD IN25 IN26 IN27 IN28 IN29 IN30 IN23 IN22 IN15 IN11 IN5 IN6 NC FSEL0 TST1 DVDD IN19 IN18 IN17 IN8 IN16 IN20 IN21 IN13 IN10 IN4 IN2 IN3 NC FSEL1 TST0 HOLD AD8488 Data Sheet Table 7. 255-Ball CSP_BGA Ball Assignment (Alphabetically by Signal) Signal AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AGND AVDD AVDD AVDD AVDD AVDD AVDD AVDD AVDD AVDD Ball E5 E6 E7 E8 E9 F5 G5 G7 G8 G9 G10 H5 H7 H8 H9 H10 J5 J7 J8 J9 J10 K5 K7 K8 K9 K10 L5 L7 M5 M6 M7 M8 M9 M10 M11 F6 F7 F8 F9 F10 G6 G11 H6 H11 Signal AVDD AVDD AVDD AVDD AVDD AVDD AVDD AVDD AVDD AVDD CLK CK_ENa CK_ENb CS_A CS_B CF1SEL0 CF1SEL1 DGND DGND DGND DGND DGND DGND DGND DGND DGND DGND DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD FSEL0 FSEL1 GRST GNSEL0 GNSEL1 GNSEL2 GNSEL3 Ball H12 J6 J11 K6 K11 L6 L8 L9 L10 L11 D15 E14 F14 N14 M15 C15 B15 F16 G15 G16 H15 H16 J15 J16 K15 K16 L16 B16 C16 D16 E16 F15 L15 M16 N16 P16 R16 R14 T14 H14 D14 C14 B14 A14 Signal HOLD IN0 IN1 IN2 IN3 IN4 IN5 IN6 IN7 IN8 IN9 IN10 IN11 IN12 IN13 IN14 IN15 IN16 IN17 IN18 IN19 IN20 IN21 IN22 IN23 IN24 IN25 IN26 IN27 IN28 IN29 IN30 IN31 IN32 IN33 IN34 IN35 IN36 IN37 IN38 IN39 IN40 IN41 IN42 Ball T16 N11 P11 T11 T12 T10 R11 R12 P12 T4 N12 T9 R10 P10 T8 P9 R9 T5 T3 T2 T1 T6 T7 R8 R7 P8 R1 R2 R3 R4 R5 R6 P1 N8 N10 P7 P6 P5 P3 P4 P2 N9 N1 N6 Signal IN43 IN44 IN45 IN46 IN47 IN48 IN49 IN50 IN51 IN52 IN53 IN54 IN55 IN56 IN57 IN58 IN59 IN60 IN61 IN62 IN63 IN64 IN65 IN66 IN67 IN68 IN69 IN70 IN71 IN72 IN73 IN74 IN75 IN76 IN77 IN78 IN79 IN80 IN81 IN82 IN83 IN84 IN85 IN86 Rev. A | Page 10 of 20 Ball N5 N4 N3 N2 M1 M4 M3 M2 N7 L4 L3 L2 L1 K4 K3 K2 K1 J4 J3 J2 J1 H4 H3 H2 H1 E3 E2 G4 G3 G2 G1 C8 E1 F4 F3 F2 F1 A5 C7 E4 D8 A6 D7 D6 Signal IN87 IN88 IN89 IN90 IN91 IN92 IN93 IN94 IN95 IN96 IN97 IN98 IN99 IN100 IN101 IN102 IN103 IN104 IN105 IN106 IN107 IN108 IN109 IN110 IN111 IN112 IN113 IN114 IN115 IN116 IN117 IN118 IN119 IN120 IN121 IN122 IN123 IN124 IN125 IN126 IN127 IRST NC NC Ball D5 D4 D3 D2 D1 C6 C5 C4 C3 C2 C1 B6 B5 B4 B3 B2 B1 B8 B7 A4 A3 A2 D10 A7 A8 A9 B9 C9 A10 B10 C10 D9 A11 B11 C11 E11 D11 A12 B12 D12 C12 E15 A13 A15 Signal NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC NC OUTLOW OUTHIGH PWR RST TST_MODE TST0 TST1 TST2 TST3 TST4 TST5 TST6 VREF VREF_ESD WR Ball B13 C13 D13 E10 E12 E13 F11 F13 G13 H13 J12 J13 K13 L13 M12 M13 N13 P13 R13 T13 F12 G12 P14 A16 J14 T15 R15 P15 N15 M14 L14 K14 L12 K12 G14 Data Sheet AD8488 TYPICAL PERFORMANCE CHARACTERISTICS 500 G = 1V/V 450 TCASE = 30°C CPANEL = 38pF VOUT = –104mV 400 0.02 350 0.01 0 –0.01 300 250 CF1 = 0.9pF 200 –0.02 150 –0.03 100 –0.04 50 –0.05 0 10 20 30 40 50 60 70 80 90 CHANNEL NUMBER 100 110 120 130 CF1 = 0.45pF CF1 = 7pF 0 0 10 20 30 40 CF1 = 3.5pF 50 60 70 80 90 100 110 120 130 CHANNEL NUMBER 09801-007 CCR (nV/e–) G = 5V/V CF1 = 0.9pF 0.04 T CASE = 30°C CPANEL = 38pF 0.03 09801-004 LINEARITY ERROR (%) 0.05 Figure 7. CCR vs. Channel for Four Values of CF1 Figure 4. Linearity Error vs. Channel G = 10 CF1 = 0.9pF = 40°C T 1400 CCASE = 38pF PANEL 1300 1300 1200 1100 1000 900 G = 10 1250 CF1 = 0.9pF CPANEL = 38pF 1200 1150 1100 1050 1000 950 900 0 10 20 30 40 50 60 70 80 90 CHANNEL NUMBER 100 110 120 130 09801-005 800 800 TYPICAL NOISE: AVERAGE OF 128 CHANNELS 850 Figure 5. Input Referred Noise (QNI) vs. Channel, CPANEL = 38 pF, TCASE = 40°C 0 10 20 30 40 TEMPERATURE (°C) 50 60 09801-008 INPUT REFERRED NOISE [QNI] (e–rms) INPUT REFERRED NOISE – QNI (e–rms) 1500 Figure 8. Input Referred Noise (QNI) vs. Temperature 12 0.004 11 0.003 GAIN = 10 10 0.002 9 CF1 = 0.9pF TCASE = 30°C CPANEL = 38pF VOUT = –104mV 7 6 5 GAIN = 4 4 0 –0.001 0 10 20 30 40 50 60 70 80 90 100 110 120 130 CHANNEL NUMBER G = 10V/V TEMPERATURE CF1 = 0.9 pF SPAN = 0°C TO 60°C T –0.003 CASE 0°C TO 20°C CPANEL = 38pF 0°C TO 40°C 0°C TO 60°C VOUT = –104mV –0.004 0 10 20 30 40 50 60 70 80 90 100 110 120 130 CHANNEL NUMBER Figure 9. Gain Drift vs. Channel for Various Temperature Spans Figure 6. Gain vs. Channel for Four Values of Gain Rev. A | Page 11 of 20 09801-009 GAIN = 2 2 1 0.001 –0.002 3 09801-006 GAIN (V/V) 8 GAIN DRIFT (%/°C) GAIN = 8 AD8488 Data Sheet 0.10 0.12 PERCENT OF OUTPUT STEP (%) 0.08 0.06 0.04 0.02 0 –0.02 –0.04 –0.06 0.04 0.02 0 –0.02 –0.04 –0.06 –0.08 50 60 70 80 90 100 110 120 130 CHANNEL NUMBER –0.10 0 10 20 30 40 50 60 70 80 90 100 110 120 130 CHANNEL NUMBER Figure 13. Crosstalk from All Nonadjacent Channels as Measured by the Percent of Output Step for Each Channel Figure 10. Adjacent Channel Crosstalk as Measured by the Percent of Output Step for Each Channel 5 340 G = 10V/V CF1 = 0.9pF 4 T CASE = 30°C CPANEL = 38pF 3 IAVDD NORMAL POWER LOW POWER 300 320 280 SUPPLY CURRENT (mA) ANALOG INPUT LEAKAGE (pA) G = 5V/V CF1 = 0.9pF 0.08 T CASE = 30°C FSEL = 160k 0.06 VIN = 0 TO –4.16mV 09801-013 G = 5V/V –0.08 CF1 = 0.9pF TCASE = 30°C –0.10 FSEL = 160k VIN = 0 TO –4.16mV –0.12 0 10 20 30 40 09801-010 PERCENTAGE OF OUTPUT STEP (%) 0.10 2 1 0 –1 –2 260 240 220 200 180 160 140 120 –3 100 –4 20 30 40 50 60 70 80 90 100 110 120 130 CHANNEL NUMBER 60 0 Figure 11. Input Leakage vs. Channel DIFFERENTIAL OFFSET VOLTAGE (mV) VOS (mV) 2 0 –2 –4 –6 –10 20 30 40 50 60 70 80 90 100 110 120 130 CHANNEL NUMBER 09801-012 –8 10 30 40 TCASE (°C) 50 60 65 –5.5 CF1 = 0.45pF CF1 = 7.0pF CF1 = 3.5pF CF1 = 0.9pF 4 0 20 Figure 14. Supply Current vs. Temperature (TCASE) 10 G = 1V/V 8 TCASE = 30°C CPANEL = 38pF V = 0V 6 IN 10 09801-014 10 G = 10V/V –5.6 CF1 = 7 pF TCASE = 30°C –5.7 CPANEL = 38pF VIN = 0V –5.8 –5.9 –6.0 –6.1 –6.2 –6.3 –6.4 –6.5 Figure 12. Differential Offset Voltage vs. Channel for Four Values of CF1 0 10 20 30 40 TEMPERATURE (°C) 50 Figure 15. Differential Offset Voltage vs. Temperature Rev. A | Page 12 of 20 60 09801-015 0 09801-011 –5 80 Data Sheet AD8488 THEORY OF OPERATION OVERVIEW The AD8488 is a 128-channel AFE intended for interfacing thin film transistor (TFT) detector panel arrays in various digital X-ray applications (see Figure 1). The device includes a 128 dual stage, charge conversion amplifiers, internal timing, and control circuitry, a 128:1 differential output multiplexer, and an analog output buffer. Only the detector panel and a minimal amount of analog circuitry are required to complete a 128-channel analog X-ray interface. The AD8488 AFE is packaged in a compact, 17 mm × 17 mm, 255-lead BGA. Analog Amplifier The AD8488 analog inputs are suitable for ac or dc connection to 128 X-ray detector panel outputs. The analog amplifier consists of two stages: an integrator followed by a correlated double sampling gain amplifier. Figure 16 is a simplified block diagram showing the basic elements of an analog channel. The characteristic CMOS high gate impedance of the integrator minimizes source loading. Prior to sampling a gate line, all 128 mux analog channels are initialized with RST, as shown in Figure 17. During the 6.1 µs GRST period, the gain amplifier acquires the reference level (2.048 V) and any low frequency ambient noise. Just prior to gate sampling, both op amps are unlocked and the feedback capacitors, CF1 and CF2, are connected. When a TFT gate line is activated (reference the bottom signal, TFT_GATE, in Figure 17), the charge of each detector cell is applied simultaneously to all 128 MOSFET integrator circuits, which begin to ramp over a 12 µs interval. As seen in Figure 16, the op amps are biased at the reference voltage, plus offset and low frequency noise error voltages. Together, the resultant differential output voltage comprises the CDS or correlated double sampled composite. Following the sampling period, the pixel charges are stored, and the charge is held for the next 133 clock cycles while the 128 channels are muxed and sampled sequentially. As the channels are selected in sequence, their outputs are applied to a dual channel, high precision, current feedback, high frequency op amp. The AD8488 was designed to drive an ADC such as the AD9244 differential input high speed converter. The mux channels are enabled and selected by the timing inputs, CK_ENa and CK_ENb. These two signals gate the clock and internal counter that actually selects the mux channel. The multiplexers must be read sequentially as one interprets from the CK_ENa and CK_ENb lines in Figure 17. The read time for each channel is 1 clock cycle. The timing signals, GATED CLKa and GATED CLKb, are developed internally and are shown in Figure 17 for reference only. Troubleshooting Channels Using the TST_MODE enable pin, individual channels are accessible for troubleshooting. Referring to Table 8, the channel address follows two initialization words, 0x01 and 0x02, while the enable pin, TST_MODE, is asserted high. SWIRST SWGRST CF1 (×4) GNSEL0 TO GNSEL3 CH (×4) CF2 = 0.5pF INTEGRATOR SWHOLD R1 (×4) GAIN AMPLIFIER – R1 (×4) CM + – IN0 TO IN127 TO MUX + SWHOLD CF2 = 0.5pF GNSEL0 CH (×4) TO GNSEL3 SWGRST CFx: FEEDBACK CAPACITOR CH: HOLD CAPACITOR Figure 16. Block Diagram of an Integrator Channel Rev. A | Page 13 of 20 09801-017 VREF AD8488 Data Sheet TIMING SIGNALS Timing Notes Figure 17 is the gate line timing diagram. The gate line sequence requires 405 clock cycles for channel integration and the sequential transfer to an ADC. The timing signals, IRST, GRST, and HOLD, control the integration, gain, and hold switches, respectively, and define the timing intervals required by each of the integrator channels. These signals may be generated by an FPGA, ROM, or similar device. Refer to Figure 17 and the following timing notes: The balance of the signals shown in Figure 16 are user discretionary and encoded according to Table 8 through Table 11 for select gain, hold capacitor values, low-pass filter values, and mux output channels for troubleshooting. 1. 2. The CLK frequency can range from 1 MHz to 15 MHz. RST must be low (active) for the first half clock of the gate line cycle. tGRST must be ≥ 6.1 µs. tINT must be ≥ 12 µs. The CK_ENa and CK_ENb intervals must be exactly 67 clocks. The time can be longer if tCLK exceeds 67 ns. The tIRST interval must be exactly 130 CLKs. 3. 4. 5. 6. 1 GATE LINE: tGATE (27ms) (WITH 15MHz CLOCK; SEE NOTE 4) 18.1µs tREAD (133 CLKS) RST tIRST (130 CLKS) IRST tGRST ≥ 6.1µs GRST ≥6µs HOLD tINT (12µs) tCLK (SEE NOTE 1) ≥ 67ns tCLK (SEE NOTE 1) CLK tDELAY3 (SEE NOTE 3) tDELAY2 (SEE NOTE2) CK_ENa 67 CLKS GATED CLKa tDELAY2 (SEE NOTE 2) tDELAY3 (SEE NOTE 3) CK_ENb 67 CLKS GATED CLKb (SEE NOTE 5) NOTES 1. IN THIS EXAMPLE tCLK = 67ns (15MHz). 2. ¼ CLK < tDELAY2 < ½ CLK. 3. 0 CLK < tDELAY3 < ¼ CLK. 4. tGATE = tGRST + tINT + tREAD = 27µs. 5. ALL LOGIC LEVELS EXCEPT RST ARE ACTIVE HIGH. 6. SHOWN AS ACTIVE HIGH – CHARGE IS TRANSFERRED TO ALL CHANNELS DURING THIS INTERVAL. Figure 17. Gate Line Timing Diagram Rev. A | Page 14 of 20 09801-018 TFT_GATE Data Sheet AD8488 APPLICATIONS INFORMATION CONTROL REGISTER BIT MAPS Table 8. Mux Switch Test Register Address Bits, Addresses Valid When TST = High TST6 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 TST5 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 TST4 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 TST3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 TST2 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 TST1 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 Rev. A | Page 15 of 20 TST0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 71 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 Selects Channel None −2 −1 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 AD8488 TST6 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 Data Sheet TST5 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 TST4 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 TST3 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 TST2 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 TST1 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 TST0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Selects Channel 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 Table 9. Integrator Capacitor Content (CSEL0 and CSEL1) CF1SEL1 0 0 1 1 CF1SEL0 0 1 0 1 CF1 (pF) 0.45 0.9 3.5 7.0 Table 10. Low-Pass Filter Time Constant—Resistor Selection Address Bits (FSEL0 and FSEL1) FSEL1 0 0 1 1 FSEL0 0 1 0 1 R1 (kΩ) 195 130 65 0 Time Constant (µs) 1.5 1.0 0.5 0 Table 11. Gain Selection (Gain Amp/GNSEL0 to GNSEL3; CF2 = 0.5 pF) GNSEL3 (CH3 = 1.5 pF) 0 0 0 0 0 0 0 0 1 1 1 GNSEL2 (CH2 = 2 pF) 0 0 0 0 1 1 1 1 1 1 1 GNSEL1 (CH = 1 pF) 0 0 1 1 0 0 1 1 0 1 1 Rev. A | Page 16 of 20 GNSEL0 (CH = 0.5 pF) 0 1 0 1 0 1 0 1 1 0 1 Total CH (pF) 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 Gain 0 1 2 3 4 5 6 7 8 9 10 Data Sheet AD8488 TIMING DIAGRAMS CS_A, CS_B t1 t2 t4 t3 WR t5 t6 NOTES 1. TIMING DIAGRAM TO WRITE A STATIC SIGNAL TO CHANNEL 0 TO CHANNEL 63 OR CHANNEL 64 TO CHANNEL127. 2. CS_A LOW OR CS_B LOW SELECTS CHANNEL 0 TO CHANNEL 63 OR CHANNEL 64 TO CHANNEL 127. WRITE DATA BY SEQUENCING WR LOW, THEN HIGH. 09801-019 DATA Figure 18. Input Register Timing Diagram tCLK CLK MUX-CH001 TO MUX-CH003 tDELAY7 001 tDELAY8 002 003 ADC INPUT ADC SAMPLE MUX-CH001 SAMPLE SETTLES ADC SAMPLE ADC SAMPLE MUX-CH002 MUX-CH003 2. TIME DELAY SAMPLES (REFERENCE, INTERNAL ONLY): MIN. TYP. MAX. tDELAY 7: 5.3ns 6.6ns 7.8ns tDELAY 8: 1.2ns 1.4ns 1.7ns 3. tA IS SYNCHRONOUS WITH ADC TIMING. Figure 19. Timing Diagram—AD8488 to ADC Rev. A | Page 17 of 20 09801-020 NOTES 1. ADC SAMPLES OCCUR WHEN MUX-CH001 TO MUX-CH003 IS HIGH, JUST PRIOR TO THE FALLING EDGE. SAMPLE MUST BE COMPLETE BEFORE HIGH TO LOW TRANSITION. AD8488 Data Sheet OUTLINE DIMENSIONS A1 BALL CORNER 17.20 17.00 SQ 16.80 16 14 15 12 13 10 11 6 8 9 7 4 5 3 1.00 BSC *2.20 2.00 1.80 1 A B C D E F G H J K L M N P R T 15.00 BSC SQ 1.00 REF TOP VIEW A1 BALL CORNER 2 BOTTOM VIEW DETAIL A DETAIL A *1.60 1.50 1.40 0.40 MIN 0.70 COPLANARITY 0.60 0.20 0.50 BALL DIAMETER *COMPLIANT TO JEDEC STANDARDS MS-034-AAF-1 WITH EXCEPTION TO PACKAGE HEIGHT AND THICKNESS. 092409-A SEATING PLANE Figure 20. 255-Ball Chip-Scale Package Ball Grid Array [CSP_BGA] (BC-255-1) Dimensions shown in millimeters ORDERING GUIDE Model 1 AD8488KBCZ 1 Temperature Range 0°C to +85°C Package Description 255-Ball CSP_BGA Z = RoHS Compliant Part. Rev. A | Page 18 of 20 Package Option BC-255-1 Data Sheet AD8488 NOTES Rev. A | Page 19 of 20 AD8488 Data Sheet NOTES ©2012 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D09801-0-6/12(A) Rev. A | Page 20 of 20