Low Distortion, High Speed Rail-to-Rail Input/Output Amplifier AD8028-KGD-CHIP Known Good Die

advertisement

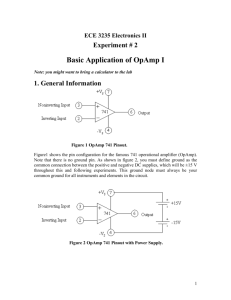

Low Distortion, High Speed Rail-to-Rail Input/Output Amplifier AD8028-KGD-CHIP Known Good Die FEATURES High speed 190 MHz, –3 dB bandwidth (G = +1) 100 V/µs slew rate Low distortion 120 dBc @ 1 MHz SFDR 80 dBc @ 5 MHz SFDR Selectable input crossover threshold Low noise 4.3 nV/√Hz 1.6 pA/√Hz Low offset voltage: 900 µV max Low power: 6.5 mA/amplifier supply current Disable mode Wide supply range: 2.7 V to 12 V Known good die (KGD): these die are fully guaranteed to data sheet specifications Many rail-to-rail input amplifiers have an input stage that switches from one differential pair to another as the input signal crosses a threshold voltage, which causes distortion. The AD8028-KGDCHIP has a unique feature that allows the user to select the input crossover threshold voltage through the SELECT pin. This feature controls the voltage at which the complementary transistor input pairs switch. The AD8028-KGD-CHIP also has intrinsically low crossover distortion. With its wide supply voltage range (2.7 V to 12 V) and wide bandwidth (190 MHz), the AD8028-KGD-CHIP amplifier is designed to work in a variety of applications where speed and performance are needed on low supply voltages. The AD8028-KGD-CHIP has a disable mode that is controlled via the SELECT pin. The AD8028-KGD-CHIP is rated to work over the industrial temperature range of –40°C to +125°C. Additional application and technical information can be found in the AD8028 data sheet. APPLICATIONS Filters ADC drivers Level shifting Buffering Professional video Low voltage instrumentation GENERAL DESCRIPTION The AD8028-KGD-CHIP1 is a high speed amplifier with rail-torail input and output that operates on low supply voltages and is optimized for high performance and wide dynamic signal range. The AD8028-KGD-CHIP has low noise (4.3 nV/√Hz, 1.6 pA/√Hz) and low distortion (120 dBc at 1 MHz). In applications that use a fraction of or the entire input dynamic range and require low distortion, the AD8028-KGD-CHIP is an ideal choice. Protected by U.S. patent numbers 6,486,737B1; 6,518,842B1 1 Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2012 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com AD8028-KGD-CHIP Known Good Die TABLE OF CONTENTS Features ...................................................................................... 1 ESD Caution .......................................................................... 6 Applications ............................................................................... 1 Pad Configuration and Function Descriptions .................... 7 General Description ................................................................. 1 Outline Dimensions ................................................................. 8 Revision History ....................................................................... 2 Die Specifications and Assembly Recommendations ...... 8 Specifications............................................................................. 3 Ordering Guide ..................................................................... 8 Absolute Maximum Ratings.................................................... 6 REVISION HISTORY 11/12—Rev. A to Rev. B Changed AD8028-KGD-CHIPS to AD8028-KGD-CHIP.......................................................... Universal Changes to Table 1 ............................................................................ 3 Changes to Table 2 ............................................................................ 4 Changes to Table 3 ............................................................................ 5 9/12—Rev. 0 to Rev. A Changes to Table 1 ........................................................................... 3 Changes to Table 2 ............................................................................ 4 Changes to Table 3 ............................................................................ 5 Updated Outline Dimensions ......................................................... 8 Changes to Ordering Guide ............................................................ 8 7/12—Revision 0: Initial Version Rev. B | Page 2 of 8 Known Good Die AD8028-KGD-CHIP SPECIFICATIONS VS = ±5 V at TA = 25°C, RL = 1 kΩ to midsupply, G = 1, unless otherwise noted. Table 1. Parameter DYNAMIC PERFORMANCE –3 dB Bandwidth Bandwidth for 0.1 dB Flatness Slew Rate Settling Time to 0.1% NOISE/DISTORTION PERFORMANCE Spurious-Free Dynamic Range (SFDR) Input Voltage Noise Input Current Noise Differential Gain Error Differential Phase Error Crosstalk, Output to Output DC PERFORMANCE Input Offset Voltage Input Offset Voltage Drift Input Bias Current Input Offset Current Open-Loop Gain INPUT CHARACTERISTICS Input Impedance Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio SELECT PIN Crossover Low, Selection Input Voltage Crossover High, Selection Input Voltage Disable Input Voltage Disable Switching Speed Test Conditions/Comments Min Typ G = 1, VOUT = 0.2 V p-p G = 1, VOUT = 2 V p-p G = 2, VOUT = 0.2 V p-p G = +1, VOUT = 2 V step/G = −1, VOUT = 2 V step G = 2, VOUT = 2 V step 138 20 190 32 16 90/100 35 Short-Circuit Output Off Isolation Capacitive Load Drive POWER SUPPLY Operating Range Quiescent Current/Amplifier Quiescent Current (Disabled) MHz MHz MHz V/µs ns dBc dBc nV/√Hz pA/√Hz % Degrees dB SELECT = three-state or open, PNP active 200 µV SELECT = high NPN active 240 µV TMIN to TMAX VCM = 0 V, NPN active TMIN to TMAX VCM = 0 V, PNP active TMIN to TMAX VOUT = ±2.5 V 1.50 4 4 −8 −8 ±0.1 110 VCM = ±2.5 V 6 2 −5.2 to 5.2 110 MΩ pF V dB −3.3 to +5 −3.9 to −3.3 −5 to −3.9 980 V V V ns 45 ns 40/45 ns Three-state < ±20 µA 50% of input to <10% of final VOUT VIN = +6 V to −6 V, G = −1 −VS + 0.20 Sinking and Sourcing VIN = 0.2 V p-p, f = 1 MHz, SELECT = low 30% overshoot +VS − 0.06, −Vs + 0.06 120 −49 20 2.7 6 Tested −11 Tested ±0.9 Tested +VS Tested µV/°C µA µA µA µA µA dB V mA dB pF 6.5 12 8.5 Tested V mA 0.8 3 Tested mA SELECT = low −VS 1 GBD GBD 120 80 4.3 1.6 0.1 0.2 −93 +VS Power Supply Rejection Ratio Status 1 Unit fC = 1 MHz, VOUT = 2 V p-p, RF = 24.9 Ω fC = 5 MHz, VOUT = 2 V p-p, RF = 24.9 Ω f = 100 kHz f = 100 kHz NTSC, G = 2, RL = 150 Ω NTSC, G = 2, RL = 150 Ω G = 1, RL = 100 Ω, VOUT = 2 V p-p, VS = ±5 V @ 1 MHz Enable Switching Speed OUTPUT CHARACTERISTICS Output Overdrive Recovery Time (Rising/Falling Edge) Output Voltage Swing Max −0.9 VS ± 1 V −0.6 110 GBD is guaranteed by design. Rev. B | Page 3 of 8 Tested mA dB AD8028-KGD-CHIP Known Good Die VS = 5 V at TA = 25°C, RL = 1 kΩ to midsupply, unless otherwise noted. Table 2. Parameter DYNAMIC PERFORMANCE −3 dB Bandwidth Bandwidth for 0.1 dB Flatness Slew Rate Settling Time to 0.1% NOISE/DISTORTION PERFORMANCE Spurious-Free Dynamic Range (SFDR) Input Voltage Noise Input Current Noise Differential Gain Error Differential Phase Error Crosstalk, Output to Output DC PERFORMANCE Input Offset Voltage Input Offset Voltage Drift Input Bias Current Input Offset Current Open-Loop Gain INPUT CHARACTERISTICS Input Impedance Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio SELECT PIN Crossover Low, Selection Input Voltage Crossover High, Selection Input Voltage Disable Input Voltage Disable Switching Speed Test Conditions/Comments Min Off Isolation Short-Circuit Current Capacitive Load Drive POWER SUPPLY Operating Range Quiescent Current/Amplifier 1 Max Status 1 Unit G = 1, VOUT = 0.2 V p-p 131 G = 1, VOUT = 2 V p-p 18 G = 2, VOUT = 0.2 V p-p G = +1, VOUT = 2 V step/G = −1, VOUT = 2 V step G = 2, VOUT = 2 V step 185 28 12 85/100 40 ns fC = 1 MHz, VOUT = 2 V p-p, RF = 24.9 Ω fC = 5 MHz, VOUT = 2 V p-p, RF = 24.9 Ω f = 100 kHz f = 100 kHz NTSC, G = 2, RL = 150 Ω NTSC, G = 2, RL = 150 Ω G = 1, RL = 100 Ω, VOUT = 2 V p-p, VS = ±5 V @ 1 MHz 90 64 4.3 1.6 0.1 0.2 −92 dBc dBc nV/√Hz pA/√Hz % Degrees dB SELECT = three-state or open, PNP active SELECT = high NPN active 200 800 Tested µV 240 900 Tested µV TMIN to TMAX VCM = 2.5 V, NPN active TMIN to TMAX VCM = 2.5 V, PNP active TMIN to TMAX VOUT = 1 V to 4 V 2 4 4 −8 −8 ±0.1 105 µV/°C µA µA µA µA µA dB VCM = 0 V to 2.5 V 6 2 −0.2 to +5.2 105 MΩ pF V dB 1.7 to 5 1.1 to 1.7 0 to 1.1 1100 V V V ns 50 ns 50/50 ns Three-state < ±20 µA 50% of input to <10% of final VOUT Enable Switching Speed OUTPUT CHARACTERISTICS Overdrive Recovery Time (Rising/Falling Edge) Output Voltage Swing Typ VIN = −1 V to +6 V, G = −1 RL = 1 kΩ −Vs + 0.12 VIN = 0.2 V p-p, f = 1 MHz, SELECT = low Sinking and sourcing 30% overshoot +VS − 0.04, −Vs + 0.04 −49 105 20 2.7 GBD GBD +Vs V dB mA pF 12 6 Tested MHz MHz MHz V/µs GBD V mA Quiescent Current (Disabled) SELECT = low 320 µA Power Supply Rejection Ratio VS ± 1 V 105 dB GBD is guaranteed by design. Rev. B | Page 4 of 8 Known Good Die AD8028-KGD-CHIP VS = 3 V at TA = 25°C, RL = 1 kΩ to midsupply, unless otherwise noted. Table 3. Parameter DYNAMIC PERFORMANCE –3 dB Bandwidth Bandwidth for 0.1 dB Flatness Slew Rate Settling Time to 0.1% NOISE/DISTORTION PERFORMANCE Spurious-Free Dynamic Range (SFDR) Input Voltage Noise Input Current Noise Differential Gain Error Differential Phase Error Crosstalk, Output to Output DC PERFORMANCE Input Offset Voltage Input Offset Voltage Drift Input Bias Current Input Offset Current Open-Loop Gain INPUT CHARACTERISTICS Input Impedance Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio SELECT PIN Crossover Low, Selection Input Voltage Crossover High, Selection Input Voltage Disable Input Voltage Disable Switching Speed Enable Switching Speed OUTPUT CHARACTERISTICS Output Overdrive Recovery Time (Rising/Falling Edge) Output Voltage Swing Short-Circuit Current Off Isolation Capacitive Load Drive POWER SUPPLY Operating Range Quiescent Current/Amplifier Quiescent Current (Disabled) Power Supply Rejection Ratio 1 Test Conditions/Comments Min Typ G = 1, VOUT = 0.2 V p-p G = 1, VOUT = 2 V p-p G = 2, VOUT = 0.2 V p-p G = +1, VOUT = 2 V step/G = –1, VOUT = 2 V step G = 2, VOUT = 2 V step 125 19 180 29 10 73/100 Max Status 1 Unit GBD GBD MHz MHz MHz V/µs 48 ns fC = 1 MHz, VOUT = 2 V p-p, RF = 24.9 Ω fC = 5 MHz, VOUT = 2 V p-p, RF = 24.9 Ω f = 100 kHz f = 100 kHz NTSC, G = 2, RL = 150 Ω NTSC, G = 2, RL = 150 Ω G = 1, RL = 100 Ω, VOUT = 2 V p-p, VS = 3 V @ 1 MHz 85 64 4.3 1.6 0.15 0.20 –89 dBc dBc nV/√Hz pA/√Hz % Degrees dB SELECT = three-state or open, PNP active SELECT = high NPN active TMIN to TMAX VCM = 1.5 V, NPN active TMIN to TMAX VCM = 1.5 V, PNP active TMIN to TMAX 200 µV VOUT = 1 V to 2 V 240 2 4 4 –8 –8 ±0.1 100 µV µV/°C µA µA µA µA µA dB RL = 1 kΩ VCM = 0 V to 1.5 V 6 2 –0.2 to +3.2 100 MΩ pF V dB 1.7 to 3 V 1.1 to 1.7 V 50% of input to <10% of final VOUT 0 to 1.1 1150 50 V ns ns VIN = –1 V to +4 V, G = –1 55/55 ns Three-state < ±20 µA RL = 1 kΩ –VS + 0.09 Sinking and sourcing VIN = 0.2 V p-p, f = 1 MHz, SELECT = low 30% overshoot +VS – 0.03, –Vs + 0.03 72 –49 +VS Tested mA dB 20 2.7 SELECT = low VS ± 1 V GBD is guaranteed by design. Rev. B | Page 5 of 8 pF 12 6.0 300 100 V GBD V mA µA dB AD8028-KGD-CHIP Known Good Die ABSOLUTE MAXIMUM RATINGS ESD CAUTION Table 4. Parameter Supply Voltage Common-Mode Input Voltage Differential Input Voltage Storage Temperature Operating Temperature Range Junction Temperature Rating 12.6 V ±VS ± 0.5 V ±1.8 V –65°C to +125°C –40°C to +125°C 150°C Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Rev. B | Page 6 of 8 Known Good Die AD8028-KGD-CHIP PAD CONFIGURATION AND FUNCTION DESCRIPTIONS 10 1 9 8 2 3 5 6 10787-003 7 4 ADI Logo Figure 1.Pad Configuration Table 5. Pad Function Descriptions Pad No. 1 2 3 4 5 6 7 8 9 10 X-Axis −326 −547 −590 −592 −286 +325 +593 +596 +324 +86 Y-Axis +491 −212 −346 −490 −492 −489 −490 −350 +491 +492 Mnemonic VOUTA −IN A +IN A −VS Disable Control/Select A Disable Control/Select B +IN B −IN B VOUTB +VS Rev. B | Page 7 of 8 Description Output A. Inverting Input A. Noninverting Input A. Negative Supply. Disable Control/Select Mode A. Disable Control/Select Mode B. Noninverting Input B. Inverting Input B Output B. Positive Supply. AD8028-KGD-CHIP Known Good Die OUTLINE DIMENSIONS 1.415 10 1 9 1.205 8 2 3 7 5 6 TOP VIEW (CIRCUIT SIDE) 0.076 × 0.076 08-23-2012-A 4 Figure 2. 10-Pad Bare Die [CHIP] (C-10-3) Dimensions shown in millimeters DIE SPECIFICATIONS AND ASSEMBLY RECOMMENDATIONS Table 6. Typical Die Specifications Parameter Chip Size Scribe Line Width Die Size Thickness Bond Pads (Min Size) Bond Pad Composition Backside Passivation ESD Value 1420 × 1290 75 55.7 × 47.4 305 76 × 76 1% Copper Doped Aluminum Si Doped oxide/SiN HBM 2000 Unit µm µm Mil µm µm % Not Applicable Not Applicable V Table 7. Assembly Recommendations Assembly Component Die Attach Bonding Method Recommendation Ablestik 84-1LMIS R4 1 mil gold ORDERING GUIDE Model AD8028-KGD-CHIP Temperature Range –40°C to +125°C Package Description 10-Pad Bare Die ©2012 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D10787-0-11/12(B) Rev. B | Page 8 of 8 Package Option C-10-3