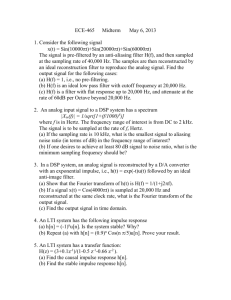

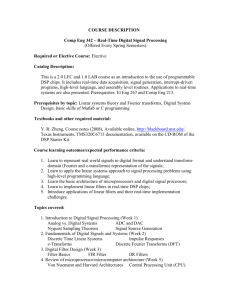

SECTION 9 DSP APPLICATIONS

advertisement