Proposed solution for inf3410 exam 2010

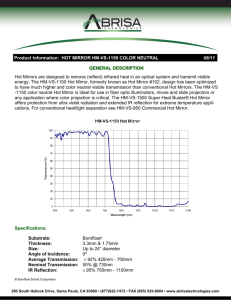

advertisement

Proposedsolutionforinf3410exam2010 Problem 1: “An important design element of integrated amplifiers is a current mirror. Draw the schematics of such a mirror and explain functional properties and potential errors introduced by the circuit.” The main function of the current mirror is to make a copy of a current. In addition scaling of the input current may be done by designing transistors with different sizes. The major issue with the current mirror (simple) is the channel length shortning of the output transistor. Major deviation from the input current as the output current is increased as a function of the (unknown) output voltage. Problem 2: This circuit is basically a combination of two current mirrors. The series output connection will limit the output current by the smallest input currents. a) I1 = I2 When input currents are the same, the output current should be approximately the same as the input currents with some minor error due to the stacking. The I1 current mirror will limit output current to I1 and the I2 mirror will limit to I2. However, the I2 mirror is “source degenerated” leading to the somewhat reduce mirror of I2 current. b) I1 < I2 When I1 is less than I2, the I1 input current will limit the current supplied to the I2 output transistor and will ensure Iout=I1. The M4 transistor will enter triode region and appear as a series resistor. c) I1 > I2 When I2 is the smallest current, we know that the M2 device is in triode region and is equivalent to a resistor. The series resistor at the source of M4 will “soften” the reference and shift he source voltage somewhat from ground. This will reduce the output current, I2, somewhat. However, I2 will still set the maximum allowed. Problem 3 Since M4 is “on” when I1 < I2 it will operate (close to) the triode region, while the M2 device will limit the current and work in saturation. When I1 > I2 we have the M2 transistor with highest gate voltage and limiting the output current by the I2 input. The M2 device will operate in the triode region, while the M4 device will operate in saturation. Problem 4 4a) All nodes are low impedance, except for the voltage mode output node. The input stage may be considered as two current mirrors back‐to‐back allowing for bidirectional input current. For negative input current (sinking), the M5‐M6 current mirror will increase the pull‐up current multiplied by the transistor ration, B2. The lower mirror, M7‐M8 will get less current and reduce the pull‐down current by a similar fraction. A similar behavior will occur for positive currents (source). 4b: This circuit is a transimpedance or transresistance amplifier converting current to voltage. 4c) The primary gain of the circuit is simply the current gain introduced in the m5‐m6 and m7‐m8 current mirrors indicated by B2. The transresistance is therefore given by: AR Vout B 2 B2 ro 6 || ro8 I in Gout 4d) The B1 transistor ratio is used to scale down the biasing current saving power. The B2 transistor ratios (upper and lower) are setting the gain of the circuit by design. 4e) With only one high impedance node in this circuit, the bandwidth is limited by the frequency characteristics on the output node. Assuming a load capacitance CL and additional node capacitance of Co, we may write: BW 1 ro 6 || ro 8 C L Co 4f) It is impossible to determine the GBW because the gain is a transresistance which cannot be set to unity (=1).