On the Potential of CMOS Recharged Semi-Floating Gate Devices used... Balanced Ternary Logic

advertisement

On the Potential of CMOS Recharged Semi-Floating Gate Devices used in

Balanced Ternary Logic

Henning Gundersen

Department of Informatics, Nanoelectronic Systems Group, University of Oslo

Blindern, NO-0316, Oslo, Norway

Email: henningg@ifi.uio.no

Abstract

Most of the electronic circuits designed today use binary

logic. However, will binary logic be the leading technology

in the future, why not uses balanced ternary logic, implemented using recharged semi-floating gate (RSFG) devices,

instead? This paper gives some measurements and analyzes

novel applications using CMOS RSFG technology.

1

Introduction

Use of transistors has forced the developers to use binary

solutions based on the fact that a transistor usually has two

stable states; "on" or "off". And somewhere between the

two stable states, it is an analog state of behaviour. Donald

Knuth a famous computer scientist which wrote "The Art

of Computer Programming", said "If it would have been

possible to build reliable ternary architecture, everybody

would be using it" [17]. If we use balanced ternary numbers, we can add both negative and positive numbers without any use of a sign bit. This is one of my motivations

to use Recharged Semi-Floating Gate technology to cope

with balanced ternary logic. By using this technology, we

are one step closer to find a possible solution to a reliable

ternary hardware. This paper presents some novel applications which hopefully can be used in a ternary logic design

in the future.

2

2.1

Recharged Semi-Floating Gate CMOS

Technology

Volatile Floating Gate Circuits

Volatile Floating gate transistors are not genuine floating

gates since the gate node is not completely isolated. There

are several methods to maintain the charge on the floating

gate node; pseudo, semi and recharged. This paper focuses

on recharged semi-floating gate technology.

Floating gate circuits need to be initialized, either once

only or frequently. The once and for all initialization is synonymous with programming. By recharging the floating

gate frequently, we avoid problems with any leakage currents and random or undesired disturbance of the floatinggate charges. The reset or recharge scheme can be used to

overcome some problems associated with floating-gate circuit design [2]. In a modern CMOS processes thin gate oxide makes it almost impossible to design a genuine floating

gate structure, because of the constant gate oxide current

leakage [13, 19].

2.2

Recharged Semi-Floating Gate

Devices

Recharged floating gate is also known as switched or

clocked floating gate transistors. This method was presented by Kotani et al. in 1998 [18]. It makes it easy to control the charge on the floating gate. However, the transmission gate used for the clocking introduces a constant leakage

current. This makes the circuit more suitable to be used in

digital applications, with sufficient clock frequency.

2.3

RSFG Binary Inverter

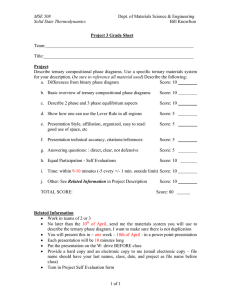

A simple binary single input gate, an inverter, is shown

in figure 1. By equalizing the transfer parameters βn and

βp of the N- and P-transistor, we obtain an equilibrium state

when the recharge clock is 1. The output and gate are driven

toward V2dd . When the recharge clock is 1, we have two

distinct cases. Assuming that the input signal is initially

1 (Vdd ), the SFG voltage can be expressed as ( V2dd ) x (1

+ ki ), where ki = Ci /Ct and Ct is the total capacitance

seen by the SFG, and the output is equal to 0. The output and the SFG will be forced toward V2dd simultaneously.

The recharge current which will pull the SFG down towards

Vdd

2 , is larger than the equilibrium current (Ibec ). We define

+ CLK

Pe

Ci

VIN

Ci

+ CLK

uses an equal amount of transistors, because the V2dd input in

Figure 2 (a) is made using a diode couple N and P transistor.

VOUT

VIN

+ CLK

VOUT

− CLK

VDD/2

Ne

VOUT VIN

− CLK

VIN

Figure 1. A typical recharged semi-floating gate binary inverter

VOUT

+ CLK

+ CLK

the recharge rise rime tr as the time required to recharge the

output from 0 to V2dd (and the SFG simultaneously). If the

input signal is initially 0, the SFG voltage is ( V2dd ) x (1 - ki )

and the output is 1. The recharge current will be reduced

compared to the former case due to the body effect of the

n-channel recharge transistor. In order to achieve a correct

recharge to the equilibrium state in a chain of gates, we need

to recharge all gates and all inputs simultaneously. In addition, we need to develop a synchronization scheme for the

recharge. We define the recharge fall time tf as the time

required to recharge the output from 1 to V2dd . The recharge

frequency is twice the frequency of the input signal.

2.4

The Auto-Zero Element

The Auto-Zero Element (AZE) can be seen as a signal

converter. By using the AZE we are able to use DC signals

in addition to a conventional binary signal as input to the

RSFG circuits. When interfacing with a binary signal, the

clock frequency has to be twice the input frequency of the

binary signal. An example of AutoZero elements is seen

in figure 2. Figure 2 (a) consist of two Pass Gate circuits

which is opposite clocked. The upper has V2dd as input, the

lower Pass Gate circuit has the input signal Vin as input.

Measured typical output characteristics of the circuit in

figure 2 (a) is presented in figure 12, 13 and 14. The upper

signal signifies the clock signal (1Vpp), the lower is the output signal. The input signals are DC-signals: ’-1’ (100mV),

’+1’ (900mV) and ’0’ (500mV). The clock frequency is 200

KHz. This shows a typical recharge signal, with three significant levels. The refresh or recharge period is when the

clock is high, the evaluate period is when the clock is set

low.

Figure 2 (b) shows another solution. It has stacked transistors, and therefore has limitations on use in very high

frequency applications due to the body effect. The N and

P transistors connected to the rails, Vdd and Vss , has to have

matched transfer parameters (βn and βp ). The two solutions

a)

b)

Figure 2. Typical auto-zero elements

3

Ternary Logic vs. Multiple Valued Logic

in the last few decades Multiple-Valued logic (MVL)

has been proposed as a possible substitute to binary logic.

While binary logic is limited to only two states, "true" or

"false", multiple-valued logic can replace these with finitely

or infinitely numbers of values. A MVL system is defined

as a system operating on a higher radix than two [20]. A

radix-n set has n elements, {0, 1, ...., n-1}. The practicability of MVL depends on the accessibility of the devices

constructed for MVL operations [6]. The devices should

be able to switch between the different logical levels, and

preferably be less complex than the binary counterparts.

Ternary logic is MVL compliant. However, it only uses

three logic states, "0","1" and "2". Higher radix gives more

complexity, but is there an optimal radix? If we look at

the r ∗ w product, where r is the radix and w is the width

of the word, this product is said to be a good estimate for

optimal hardware complexity. The derivation of the function r ∗ w gives a minimal point at 2.71828; the radix and

width is treated as contentious variables. This is remarkably the napierian base1 [1]. The minimal point is closer

to radix 3 than to radix 2, hence base 3 is the most optimal numbering system. Here is an example for the r ∗ w

product for the decimal number 1024. By using the decimal numbering system with radix=10, the r ∗ w product is

given as 10 ∗ 4 = 40, binary with radix=2 (10000000000)

gives 2 ∗ 11 = 22, ternary with radix=3 (1101221) gives

3 ∗ 7 = 21.

1 Named after the Scottish mathematician John Napier (1550-1671), he

developed the concept of the logarithm and also effectively introduced the

modern notation of decimal fractions

3.1

The Balanced Ternary Numbering

System

Balanced ternary is a non-standard positional numeral

system (a balanced form), useful for comparison logic. It

is a ternary system, but unlike the standard (unbalanced)

ternary system, the digits have the values -1, 0, and +1.

This combination is especially usable for comparison between two values, where the three possible relationships are

less-than, equals, and greater-than. Balanced ternary can

represent all integers without resorting to a separate minus

sign. As early as 1840, Thomas Fowler, a self-taught English mathematician, invented a ternary mechanical calculating machine which used balanced ternary notation. All

details on the calculating machine were lost, until recently.

A research project, started in 1997, have managed to get

enough information needed to create a complete historical

replica [7].

The balanced ternary radix notation has some beneficial

properties:

a) ’Ternary inversion’is easy, change -1 with +1, and vice

versa [21]. This is a simpler than the rule for the twos complement in binary.

b) The sign of a number is given by its most significant

nonzero ’trit2 ’

c) The operation of rounding to the nearest integer is identical to truncation.

d) Addition and subtraction are essentially the same operation; you merely add the digits using the rules for addition

of digits.

e) Carry occurs less often because only 2/9 of the possible

digits sums results in carry, compared to 1/4 in binary. Carry

ripples tend to be shorter in balanced ternary than what is

the case in binary, due to a zero result from a plus carry into

a minus digit or vica versa.

There has been several attempts to realize arithmetic applications by using the ternary numbering system, but currently they lack any commercial success [12, 5].

3.2

The MAX and MIN Circuit

MAX and MIN functions are fundamental functions in

multiple valued logic and it is analogous to the OR- and

AND-function in the binary world [16, 14]. M. Inaba et al.

have presented the MAX and MIN function implemented

using Neuron-MOS Transistors in floating gate technology

[15, 14, 16]. However, another way of realizing these functions is by using recharged Semi-Floating Gate Logic. This

makes it possible to implement a low-power digital system

with reduced dynamic power dissipation without any postproduction of the chips. The advantage of this technology

2 One

trit has 3 values -1, 0, and +1, it is analogous to bit in the binary

world (0 , 1).

is presented in [2] and the circuits are presented in figure 3

and figure 4. As the figure shows, the circuit use an analog

inverter (MVL inverter) and a down literal circuit to make a

voltage comparator [3, 4, 8]. The output of the voltage comparator gives a selection signal to the pass gate circuitry,

which consists of a pPassGate (pPG), a nPassGate (nPG)

and a inverter. The pPG let the signal through when the output of the comparator is "0", and the nPG let the signal pass

when the output of the comparator is "1". To obtain a MIN

function, the nPG can swap place with the pPG, as is shown

in figure 4.

Measurements of the MAX circuit is provided in figure 11. Figure 11 verifies the operation of the circuit showing satisfactory noise margins. The output signal of the

MAX circuit is given in balanced ternary notation (-1, 0,

+1).

4

Balanced Ternary Arithmetic

4.1

Balanced Ternary Adders

My contribution to the balanced ternary arithmetic is

the hardware implementation of a Balanced Ternary Adder

(BTA) [9] and balanced ternary counters (BTC) [11, 10]. A

BTA is an essential component in arithmetic circuits, and

is used in multiplication and division structures. The first

implementation of a one trit adder, which was presented

at ISMVL in 2006, takes two Ternary inputs (X and Y)

and generate the SUM output (S0 and S1 ). The complete

schematic diagram of the first Balanced Ternary Adder circuit is shown in figure 5. Supplementary measurement results are provided in figure 15 and 16.

4.2

Balanced Ternary Counters

A balanced ternary counter (BTC) is comparable with a

ternary full adder, where the carry signal can have all logic

values (1,0 and 1). A balanced ternary counter sums up the

inputs Xi , where i is number of trits of the same weight,

and gives an output in balanced ternary notation.

4.3

The Balanced Ternary (4,2) Counter

The balanced ternary (4,2) counter (figure 6) is a modification of the BTA presented at ISMVL2006, and has similar functionalities. A (4,2) ternary counter has 4 balanced

ternary inputs (X1 ..X4 ) and two balanced ternary outputs

(S0 , S1 ). A (4,2) is also known as a 4 to 2 reducers [22].

4.3.1

The Carry Detect Stage

The carry detect stage

P4 generates a ternary carry signal, when

the input signals i=1 Xi is less than −2 and greater than

2.

pPG

INPUT 2

+ CLK

+ CLK

C2

+ CLK

C3

C5

C1

C4

OUTPUT

BIN

MVL INVERTER

OUT

DLC

nPG

INPUT 1

VOLTAGE COMPARATOR

Figure 3. A recharged semi-floating gate MAX circuit

INPUT 2

nPG

+ CLK

+ CLK

C2

+ CLK

C3

C5

C1

C4

OUTPUT

BIN

MVL INVERTER

OUT

DLC

INPUT 1

pPG

VOLTAGE COMPARATOR

Figure 4. A recharged semi-floating gate MIN circuit

+ CLK

C1

+ CLK

+ CLK

AZC

C2

− CLK

i4

i1

C12

C3

+ CLK

C16

C20

+ CLK

+ CLK

C−HIGH

C18

C13

+ CLK

C4

+ CLK

i9

i7

S1

AZC

C5

− CLK

i2

i5

C−LOW

___

C6

+ CLK

X

AZC

− CLK

C7

+ CLK

C8

C9

C11

+ CLK

+ CLK

C10

i3

Y

S1

CARRY DETECT

C14

C17

C21

+ CLK

+ CLK

C19

C15

i6

i8

AZC

− CLK

PRE−ADDER

Figure 5. A recharged semi-floating gate balanced ternary adder

i 10

S0

C1

X1

C2

X2

+ CLK

+ CLK

i1

i2

C3

X3

C23

C25

+ CLK

+ CLK

C4

X4

C5

C18

+ CLK

C−HIGH

C24

i5

C19

i6

S1

C6

− CLK

C−LOW

C7

+ CLK

+ CLK

__

S1

C8

i3

i4

C9

CARRY DETECT

C10

C13

C20

C14

+ CLK

C22

+ CLK

C21

C15

i7

S0

i8

C16

C17

Figure 6. A recharged semi-floating gate balanced ternary (4,2) counter

This is achieved by using a 5 input threshold circuit (i1 and

i3). Looking at figure 6, we see that the 4 inputs X1 ..X4 , are

compared to the clock pulse ’+Clk’ and ’-Clk’, connected

respectively to input capacitors C5 and C6 .

The upper circuits i1 and i2 generates the binary ’CHIGH’ signal, which is set to the logic level ’1’ when the

sum of the inputs Xi , is greater than 2. The input capacitors

C1 ..C4 are equal. Capacitor

P4 C5 determines the threshold of

i1, by comparing the i=1 Xi with the ’+Clk’ signal (The

’+Clk’ signal is in phase with reference clock).

’C-LOW’ is set in a similar way, except it will be set

to logic level ’−1’ when the sum of the inputs Xi is less

than -2. The threshold of i3 is determined by the capacitor

C6 , which is connected to the ’-Clk’ signal (The ’-Clk’ is in

opposite phase with the reference clock).

The inverter i5 is a binary to ternary converter. It converts the two binary carry signals (C-LOW, C-HIGH) to a

balanced ternary carry signal (S1 ).

4.3.2

The Output Stages, S0 and S1

To generate the correct ’S1 ’ signal, we need to do a ternary

inversion of the output signal of inverter i5 (S1 ). This is

done by using the ternary inverter i6. The adder circuits i7

and i8 generates the ’S0 ’ signal. This is done by weighting

the inverted ’S1 ’ three times the input signals Xi , which in

turn is done by choosing C13 three times larger than each of

the input capacitors C14 ..C17 .

A 4 trit balanced ternary adder can be realized by using four (4,2) counters as shown in figure 7, compared to

a binary solution, it uses less active devices, hence reduced

power consumption [10].

Z 3 Y3 X 3

1

0

Z 2 Y2 X 2

0

−1 0

(4,2)

BTC

S4

0

0

(4,2)

BTC

S3

0

S4

Z 1 Y1 X1

0

S3

1

S3

0

0

(4,2)

BTC

S2

0

Z 0 Y0 X 0

−1

−1

S2

S2

C0

1

0

(4,2)

BTC

S1

0

S1

−1

S1

S0

0

1

S0

Figure 7. An example of a 4 trit parallel balanced

ternary adder using (4,2) counters

5

Measurements and Results

Two prototype chips where produced. They where made

by STMicroelectronics using a 90nm CMOS process. A

layout of the second chip is shown in figure 8; the areal of

the chip is 1mm3 . The first chip contained some simple

RSFG structures: Auto-zero, MAX, Ternary-NOT and the

simple balanced ternary adder. The second chip contained

a balanced ternary (4,2) counter, a 4 trit parallel balanced

ternary adder and a (13,3) counter. The lower part of the

chip in figure 8 is the MVL applications. It shows ten (4,2)

counters; the four leftmost are used in the 4 trit parallel

balanced ternary adder, the five rightmost counters utilize

the (13,3) counter. The one in the middle is a single (4,2)

counter. This paper does not support measurement results

from the second chip; they will be made available later.

Figure 9 shows the measurement set-up for the first

chip. The measurement was done using the Tektronix TDS

3052 digital oscilloscope, with a 10x probe with load of

8pF ,10M Ω. This limits the output frequency, since none

of the circuits has an output buffer. All inputs are connected

to an auto-zero element, which makes it possible to use DC

signals as input to the chip.

A measurement of a simple binary RSFG inverter is supported in figure 10. The DC gain, ADC is ≈ 1. The DCcharacteristic is interpolated from the recharged signal measured on the oscilloscope.

The poor open-loop gain makes it difficult to maintain

logic depths, hence it is difficult to make complex logical gates. This is the problem measured for the balanced

ternary adder in figure 15 and 16, which has a limited signal

amplitude of 120mV for logical ’-1’ and 176mV for logical

’+1’. A correct operation would have given +/ − 400mV .

For a simple structures the functionality is maintained, as

measured for the auto-zero element, figure 12, 13 and 14

and the MAX circuit, figure 11.

Figure 8. Chip layout of the second MVL chip, designed by using a 90nm CMOS process from STMicroelectronics

Figure 9. The instruments set-up for the measurement of the first MVL chip.

6

Conclusions

This paper presents some useful implementations for realizing balanced ternary arithmetic circuits, which can be

used in future VLSI/ULSI circuits. The balanced ternary

counters can be implemented in arithmetic applications,

for instance in multiplication and division circuits. They

are compatible with their binary counterparts, and can replace any binary full adder structure with a similar balanced

ternary full adder structure. This a great leap toward realizing a fully ternary ALU in the future. The drawback is that

the measurement results show the RSFG circuits need some

further development to work properly.

A floating gate structure will generally generate a larger

chip area compared to a conventional design, because of the

capacitors used in the design. However, by using very small

metal-capacitors and stacking, we are able to minimize the

area needed. The 90nm CMOS process from STMicroelectronics that was used, has 7 metal layers.

In this paper, balanced ternary adder structures using balanced ternary counters have been presented. It has the following beneficial properties:

1. There is no reason to worry about the sign bit, since

the structures use balanced ternary notation.

2. The resolution compared to number of transistors is

higher than with a typical binary solution [10]

3. It is possible to build fast addition structures, using

the theory from the binary world.

1

1

0.9

INPUT 1

In

Out

0.8

0.5

0

0.7

−1

−1

−1

0

0

0

+1

+1

+1

−1

0

+1

−1

0

+1

−1

0

+1

−1

0

+1

0

0

+1

+1

+1

+1

0.6

INPUT 2

Output (volt)

1

0.5

0.5

0.4

0

0.3

"+1"

OUTPUT

0.2

0.1

0

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

"0"

"−1"

1

Input (volt)

Figure 10. Measured DC response of the RSFG binary inverter

Figure 11. Measured output charcteristics of the

RSFG MAX-circuit

References

[1] R. Appleyard. The Direct Measurment of the Napierian

Base. Proc. Phys. Soc. London, 26:178–182, 1913.

[2] Y. Berg, S. Aunet, O. Mirmotahari, and M. Høvin. Novel

Recharge Semi-Floating-Gate CMOS Logic For MultipleValued Systems. Proceedings of the 2003 IEEE International Symposium on Circuits And Systems in Bangkok,

2003.

[3] Y. Berg, T. S. Lande, Ø. Næss, and H. Gundersen. Ultra LowVoltage Floating Gate Transconductance Amplifiers. IEEE

Trans. Circuits and Systems-II: Analog and Digital Signal

Processing,vol.48,no.1, Jan. 2001.

[4] Y. Berg, Ø. Næss, M. Høvin, and H. Gundersen. Ultra Lowvoltage Floating-gate (FGUVMOS) Amplifiers. Analog Integrated Circuits and Signal Processing, 26:63–73, 2001.

[5] K. Diawuo and H. T. Mouftah. A Three-Valued CMOS

Arithmetic Logic Unit Chip. Proceedings of the 17th IEEE

International Symposium on Multiple-Valued Logic, pages

215–220, 1987.

[6] D. Etiemble. On the Performance of Multiplevalued Integrated Circuits: Past, Present, and Future. Proceedings of

the 22th international symposium on Multiple-valued logic,

pages 156–164, 1992.

[7] M. Glusker, D. M. Hogan, and P. Vass. The Ternary Calcualating Machine of Thomas Fowler. IEEE Annals of the

History of Computing, pages 4–22, 2005.

[8] H. Gundersen and Y. Berg. MAX and MIN Functions Using Multiple-Valued Recharged Semi-Floating Gate Circuits.

Proceedings of the 2004 IEEE International Symposium on

Circuits And Systems in Vancouver, pages 857–860, 2004.

[9] H. Gundersen and Y. Berg. A Novel Balanced Ternary

Adder Using CMOS Recharged Semi-Floating Gate De-

[10]

[11]

[12]

[13]

[14]

[15]

[16]

[17]

vices. Proceedings of the 36th IEEE International Symposium on Multiple-Valued Logic in Singapore, pages 18–21,

2006.

H. Gundersen and Y. Berg. Fast Addition using Balanced

Ternary Counters Designed with CMOS Semi-Floating Gate

Devices. Proceedings IEEE 37th International Symposium

on Multiple-Valued Logic, page 6p, May 2007.

H. Gundersen and Y. Berg. A Balanced Ternary Multiplication Circuit using Recharged Semi-Floating Gate Devices.

Proceedings IEEE 24th Norchip Conference, pages 205–208,

Nov. 2006.

A. Herrfeld and S. Hentsche. Ternary Multiplications Using

4-Input Adder Cells and Carry Look-Ahead. Proceedings of

the 29th IEEE International Symposium on Multiple-Valued

Logic, 1999.

P. Häfliger and H. K. O. Berge. Exploiting Gate Leakage in Deep-Submicrometer CMOS for Input Offset Adaptation. IEEE Transactions on Circuits and Systems-II:Express

Briefs, 54(2):127–130, February 2007.

M. Inaba, K. Tanno, and O. Ishizuka. Realization of NMAX

and NMIN Functions with Multi-Valued Voltage Comparators. Proceedings of the 31nd IEEE International Symposium

on Multiple-Valued Logic(ISMVL’01), 2001.

M. Inaba, K. Tanno, and O. Ishizuka. Analog Inverter with

Neuron-MOS Transistors and Its Application. IEICE Trans.

Fundamentals, Vol.E85-A, No.2 February 2002, pages 360–

365, 2002.

M. Inaba, K. Tanno, and O. Ishizuka. Multi-Valued FlipFlop with Neuron-CMOS NMIN Circuits. Proceedings of

the 32nd IEEE International Symposium on Multiple-Valued

Logic(ISMVL’02), 2002.

D. Knuth. The Art of Computer Programming, Second edition. Addison-Wesley Publishing Company, 1981. Vol 2.

Seminumerical Algorithms, pages 190-193.

Figure 12. Measured output characteristics of the

auto-zero element in figure 2(a) with input signal -1

Figure 14. Measured output characteristics of the

auto-zero element in figure 2(a) with input signal +1

Figure 13. Measured output characteristics of the

auto-zero element in figure 2(a) with input signal +0

Figure 15. Measured output characteristics (S0) of

the BTA circuit, with input signal (+1,+1)

[18] K. Kotani, T. Shibata, M. Imai, and T. Ohmi. Clocked

Neuron-MOS Logic Circuits Employing Auto Threhold Adjustment. IEEE International Solid-State Circuits Conference(ISSCC), pages 320–321,388, 1995.

[19] D. Lee, D. Blaauw, and D. Sylvester. Gate Oxide Leakage

Current Analysis and Reduction for VLSI Circuits. IEEE

Transactions on Very Large Scale Intergration (VLSI) Systems, 12(2):155–166, February 2004.

[20] K. C. Smith. Multiple-Valued logic: A Tutorial and Appreciation. IEEE Computers Vol. 21, pages 17–27, 1988.

[21] S. Stakhov. Brousentsov’s Ternary Principle, Bergman’

Number System and Ternary Mirror-symmetrical Arithmetic. The Computer Journal, Vol. 45, No.2, pages 221–236,

2002.

[22] Z. G. Vranesic and V. C. Hamacher. Threshold Logic in Fast

Ternary Multipliers. Proceedings of the 1975 IEEE International Symposium on Multiple-Valued Logic, pages 373–387,

1975.

Figure 16. Measured output characteristics (S1) of

the BTA circuit, with input signal (+1,+1)