Dbsign Sec Processing All

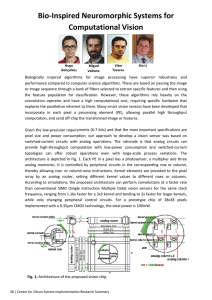

advertisement