The 12 week exam will cover everything assigned or discussed... 1. Appendix B (logic, including sequential logic)

advertisement

The 12 week exam will cover everything assigned or discussed in class from:

1. Appendix B (logic, including sequential logic)

2. Chapter 3 (computer arithmetic)

3. Chapter 4 (single cycle implementation)

4. Any extra material in the lecture notes

5. Earlier material – not focus of this exam, but may need basic info (e.g. to write and

understand MIPS code)

Below is an actual old exam. Of course, review all your notes and homework, not just the

concepts that happened to be covered in this exam.

NOTE NOTE NOTE:

1. This exam is closed-book, closed-notes EXCEPT that you will be provided with a

copy of both sides of the MIPS “green sheet”. Make sure you know how to read this!

2. You may not bring your own copy of the green sheet.

3. Students taking the “practice exam” below did NOT have access to the green sheet.

Therefore, some of the questions we might ask would naturally be different now.

4. You WILL be provided with a copy of the “single cycle datapath”

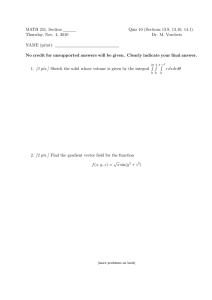

IC220 Computer Architecture

12-week Exam

SAMPLE exam

Last Name ____________________ First Name _______________

Section: 1001

3001

Alpha _____________________

5001

Note: This exam is closed-book, closed-notes.

No calculators are permitted.

To receive partial credit, show all work.

WORK QUICKLY AND DO THE EASY PROBLEMS FIRST!

Possibly useful information:

1. A copy of the single-cycle datapath is provided to you – see last page.

2. For function calls:

Integer values are passed in $a0, $a1, $a2, $a3

Floating point values are passed in $f12, $f14

Integer values are returned in $v0

Floating point values are returned in $f0.

3. ALU control

ALUOp = 00 ALU will Add

ALUOp = 01 ALU will Subtract

ALUOp = 10 ALU will perform action indicated by the instruction’s function field

NOTE: This is an exam that will be given to multiple sections and possibly to students after the

primary exam day. You may not discuss it with anyone until after XXX

(4 pts) Express -910 in the following binary forms:

6 bit, two’s complement

6 bit, sign magnitude

(2 pts) Add the following 4-bit binary, two’s complement numbers.

(1 pts) Did overflow occur?(circle one) Yes No

0011

+ 0101

(2 pts) Below is a 4-bit binary, two’s complement number. What would the equivalent number be as an 8-bit

binary, two’s complement number?

1110

(2 pts) Assume $t0 and $t1 both hold the values of two small positive integers. Write some brief MIPS code

to compute the product $t0 * $t1 and store the result in $s0. You may NOT use any pseudo-instructions.

(1 pts) Which kind of logic is a flip-flop?

COMBINATIONAL

RELATIONAL

SEQUENTIAL

TRANSITIVE

(1 pts) If a multiplexor has four data inputs, how many selector bits does it need?

Answer: ______________

IC220 SAMPLE Exam

1

(8 pts) Convert the following C code into MIPS.

float GoNavy (int k, float C[]) {

return C[4] / C[k];

}

IC220 SAMPLE Exam

2

(5 pts) From the truth table below, reduce the function y (show work and correct K-Map).

W

0

0

0

0

1

1

1

1

X

0

0

1

1

0

0

1

1

Y

0

1

0

1

0

1

0

1

Z

0

1

0

0

1

1

1

0

Z = _______________________

(4 pts) Simplify the following two equations. SHOW your work.

(F G) (F G H )

( A A)( B 0)(C 1) (C 0)( D 1)

(3 pts) Draw a picture of a circuit for the following. Do NOT simplify anything, just draw according to the

formula:

z ( A B )( B C )

.

(3 pts) A certain multiplexor has 8 data inputs. Draw a picture of this multiplexor, showing all inputs and

outputs.

IC220 SAMPLE Exam

3

The questions on this page all refer to the Single-Cycle Datapath

(see attached figure)

(4 pts) Provide the requested control signals for the following instruction. Show don’t cares if appropriate.

sw $t0, -16($t1)

(just show the answer – no explanation needed)

ALUOp

=

ALUSrc

=

Branch

=

MemtoReg

=

MemRead

=

MemWrite

=

RegDst

=

RegWrite

=

(4 pts) Provide the requested control signals for the following instruction. Show don’t cares if appropriate.

add $t0, $t1, $t2

(just show the answer – no explanation needed)

ALUOp

=

ALUSrc

=

Branch

=

MemtoReg

=

MemRead

=

MemWrite

=

RegDst

=

RegWrite

=

IC220 SAMPLE Exam

4

(11 pts) Consider the hypothetical MIPS instruction baleq (branch and link on equal). This instruction has the

same format (instruction encoding) and has the same basic functionality as a normal “beq” instruction. In

addition, if and only if the branch is taken then the address of the next sequential instruction after the “baleq”

instruction is written to register $ra (which is register #31). Formally, it does this:

if (Regs[rs] == Regs[rt]) {

// branch IS taken so do two things…

PC = BranchTarget

// 1. take the branch, same as normal beq

Regs[31] = PC+4

// 2. Save PC+4 to register #31

else {

PC = PC+4

// branch is NOT taken: goto next instruction

}

Example: baleq $s0, $t1, Label37

- If $t0 equals $t1, then this instruction will branch to Label37 AND it is hard-wired to write PC+4 to

register $ra (#31).

- If $t0 does NOT equal $t1, then this instruction will simply move on to the next instruction (at

PC+4).

The specific value of the opcode is irrelevant, so we’re omitting the details.

a.) (6 pts) On the next page is a copy of the Single-Cycle Datapath we have discussed in class. Add any

hardware (gates, adders, wires, etc.) to this figure that is necessary to support the new baleq

instruction. Be sure to draw your changes neatly and clearly. Plan in advance how your

picture can clearly indicate what is happening!

Your changes must NOT break the functioning of existing instructions!!!!

c.) (5 pts) Show the control signals here for this new instruction. Show don’t cares if appropriate. If you

need any new control signal(s), add them and also show their value(s).

ALUOp

=

ALUSrc

=

Branch

=

MemtoReg

=

MemRead

=

MemWrite

=

RegDst

=

RegWrite

=

IC220 SAMPLE Exam

5

Use this page for your answer for the new instruction.

If you need to start over, clearly cross out this page, and use the copy on the back of this paper instead.

IC220 SAMPLE Exam

6

Use this page for general reference, or if you need to start over on adding the new instruction.

Work on this page will NOT be graded unless the picture on the other side is clearly crossed out.

IC220 SAMPLE Exam

7