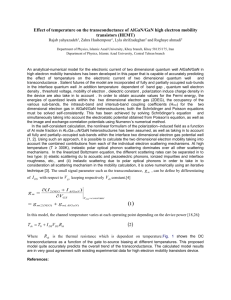

Electric Field Engineering in GaN High Electron ... Transistors

advertisement