Document 10974568

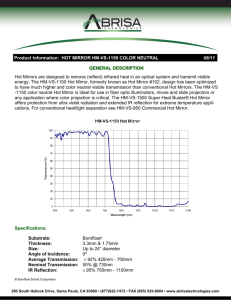

advertisement