N41T Artificial Intelligence Laboratory Qtia"llitain XT Report 1355

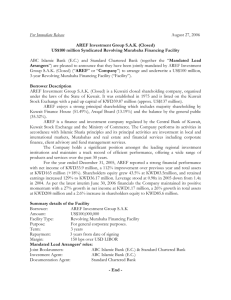

advertisement