Modeling 0.18µm BiCMOS (S18) High Sheet Resistance (RPH) Polysilicon Resistor Lifetime Drift

Modeling 0.18

µ m BiCMOS (S18) High Sheet

Resistance (RPH) Polysilicon Resistor Lifetime

Drift

by

Anartya Mandal

S.B., Massachusetts Institute of Technology (2013)

Submitted to the Department of Electrical Engineering and Computer

Science in partial fulfillment of the requirements for the degree of

Degree of Master of Engineering in Electrical Engineering and

Computer Science at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2014

Copyright 2014 Anartya Mandal. All rights reserved.

The author hereby grants to M.I.T. permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole and in part in any medium now known or hereafter created.

Author . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Department of Electrical Engineering and Computer Science

May 18, 2014

Certified by . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Jesus del Alamo

Professor of Electrical Engineering

Thesis Supervisor

Certified by . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Craig Easson

Executive Director of IC Design at Maxim Integrated

Thesis Supervisor

Accepted by . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Prof. Albert R. Meyer

Chairman, Masters of Engineering Thesis Committee

2

Modeling 0.18

µ m BiCMOS (S18) High Sheet Resistance

(RPH) Polysilicon Resistor Lifetime Drift

by

Anartya Mandal

Submitted to the Department of Electrical Engineering and Computer Science on May 18, 2014, in partial fulfillment of the requirements for the degree of

Degree of Master of Engineering in Electrical Engineering and Computer Science

Abstract

A highly accelerated lifetime test (HALT), is a stress testing methodology for accelerating product reliability that is universally conducted during the engineering development process. In conducting a HALT for circuit components, a burn-in procedure is executed, where the circuit/device is heated to a high temperature for a number of days until finally cooled back to room temperature in order for voltage, current or parameter variations to be compared. When such changes to voltage, current, or parameters are permanent, no amount of further burn-ins, cool downs or temperature cycling can return the parameter of interest back to its original value it held prior to the burn-in. This is called lifetime-drift and is a problem that circuit simulators do not model. The inability to simulate life-time drift leads to production delays, increasing costs and decreased reliability. In this thesis, I investigated the physics, created a circuit simulation model and implemented an easy-to-use utility for detecting and measuring lifetime drift in 0.18m BiCMOS high sheet resistance

(RPH) polysilicon resistors. The circuit model was made using Cadence-Spectre and

Verilog-A. The lifetime drift utility was written using Ocean scripting language.

Thesis Supervisor: Jesus del Alamo

Title: Professor of Electrical Engineering

Thesis Supervisor: Craig Easson

Title: Executive Director of IC Design at Maxim Integrated

3

4

Acknowledgments

I would like to thank Craig Easson, my supervisor, for guidance and patience; Kejun

Xia and William Liu, co-workers, whose expert knowledge in the field helped me learn as quickly as I could. Cheng-Wei Pei and Min Park for their support as alumni of

VI-A. And lastly my parents, for their love.

5

6

Contents

1 Introduction

1.1

High Accelerated Life Test (HALT) . . . . . . . . . . . . . . . . . . .

1.2

Cadence Virtuoso Spectre Circuit Simulator . . . . . . . . . . . . . .

11

1.3

Thin-Film and Polysilicon Resistors . . . . . . . . . . . . . . . . . . .

12

9

9

2 Measuring Lifetime Drift in RPH Polysilicon Resistors 13

2.1

RPH Resistor Layout . . . . . . . . . . . . . . . . . . . . . . . . . . .

13

2.2

Experimental Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14

2.3

Experimental Measurements . . . . . . . . . . . . . . . . . . . . . . .

15

3 Device Physics of RPH Polysilcon Resistors 17

3.1

Basic RPH Resistor Model . . . . . . . . . . . . . . . . . . . . . . . .

17

3.2

Physics of Lifetime Drift . . . . . . . . . . . . . . . . . . . . . . . . .

21

3.3

Modeling Lifetime Drift . . . . . . . . . . . . . . . . . . . . . . . . .

23

3.4

Modeling 2nd-Order Effects . . . . . . . . . . . . . . . . . . . . . . .

25

3.5

Complete RPH Resistor Model . . . . . . . . . . . . . . . . . . . . .

26

4 Simulating RPH Resistor Lifetime Drift in Cadence 29

4.1

Previous RPH Resistor Modeling Scheme . . . . . . . . . . . . . . . .

29

4.2

Simulations of RPH Resistor Lifetime Drift . . . . . . . . . . . . . . .

30

4.3

Simulation of RPH Resistor Lifetime Drift in Non-inverting Operational Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

33

4.4

Impact of Simulating RPH Resistor Lifetime Drift . . . . . . . . . . .

35

7

5 Design of GUI Utility For Quick Integration in Design Phase 37

5.1

Motivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

37

5.2

Graphical User Interface Design . . . . . . . . . . . . . . . . . . . . .

38

5.3

Graphical User Interface Functionality . . . . . . . . . . . . . . . . .

40

6 Concluding Remarks 41

6.1

Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

41

6.2

Future Work . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

42

A Spectre Model File Code for RPH Resistor

B Verilog-A Code Modeling Lifetime Drift in RPH Resistor

C Skill GUI Code

D Bibliography

43

61

65

71

8

Chapter 1

Introduction

In this thesis, we experimentally measure, evaluate device physics, simulate in a circuit environment and create a graphical user interface for modeling lifetime drift in polysilicon resistors.

In Chapters 1, we describe what is lifetime drift under the context of high accelerated lifetime tests and why they are so important.

In Chapters 2, we describe how to experimentally measure lifetime-drift.

In Chapters 3-4, we create a mathematical model for lifetime drift by understanding the device physics and simulate it in a Cadence’s circuit simulating environment.

In Chapter 5, we design a designer-friendly graphical user interface that will allow easy integration and simulation of lifetime drift.

1.1

High Accelerated Life Test (HALT)

A highly accelerated life test (HALT), is a stress testing methodology for accelerating product reliability during the engineering development process. It is commonly applied to electronic components and is performed to identify, understand, and resolve design, process, and layout defects in newly-developed equipment in order to validate reliability.

The methodology greatly reduces the probability of in-service failures and thus increases the product’s reliability, while decreasing both monetary costs and design

9

time.

Using this method, weaknesses can be identified using a small number of samples in the shortest possible time, with the least expense. A second function of

HALT testing is the characterization of the equipment undergoing testing; that is, the identification of the equipment’s safe ”operating limits” and ”design margins”[7].

Several standards and test methods are available for a HALT test.

Different stresses are applied with different failures occurring during each. The types of stress typically employed are: cold step, hot step, rapid temperature cycling, stepped repetitive shock, and combined environment stress (temperature cycling with repetitive shock plus power switching and power margining).

The results of HALT on a finished product provide an estimate of its long-term reliability. When HALT testing is applied during the design process, it can produce a very robust product without undue cost. Individual components such as resistors, capacitors, and diodes, printed circuit boards, and whole electronic products such as cell phones, PDAs, and televisions, eventually fail at different rates under different end-user stress levels. Therefore, failure rate data used to select any device in a product must correlate with the stress levels in the product or application [7].

A significant advantage of accelerated life testing is that it can be conducted during the development phase of a product to weed out design problems and marginal components. Thus a consumer products company can achieve better customer satisfaction because fewer products have to be returned for repair, and can also save money on warranty returns. Another major advantage is that the design team can be moved on to designing new products rather than becoming occupied with problems in older products. HALT does not measure or determine equipment reliability or life expectancy but it does serve to improve the robustness of a product. It is an empirical method used across industry to identify the limiting failure modes of a product and the stresses at which these failures occur [7].

For the case of conducting a HALT for integrated circuits (ICs), a burn-in procedure is executed. In this process, the IC to be tested is placed in an oven at a fixed temperature for a number of days until finally cooled back to room temperature in order for measurements to be taken at the nodes of interest. If we observe any voltage,

10

current or parameter variations different from measurements taken prior to having been placed in the oven, we call that lifetime drift. But the distinguishing factor of lifetime drift is that it is permanent, no amount of further burn-ins, cool downs or temperature cycling can return the parameter of interest back to the original value it held prior to the burn-in.

1.2

Cadence Virtuoso Spectre Circuit Simulator

This software is the industry standard for circuit design and simulation. It provides fast, accurate SPICE-level simulation for tough analog, radio frequency (RF) and mixed-signal circuits. It is tightly integrated with the Virtuoso custom design platform and provides detailed transistor-level analysis in multiple domains. Its architecture allows for low memory consumption and high-capacity analysis.

Spectre can perform circuit analysis while sweeping a parameter. The parameter can be frequency, temperature, component instance parameter, component model parameter, or netlist parameter. If changing a parameter affects the DC operating point, the operating point is recomputed at each step. It is also possible to sweep the circuit temperature by specifying the parameter name as ”Temp with no Dev” or ”Mod Parameter”. One can also sweep a netlist parameter by adding ”No Dev”, or ”Mod Parameter” to the parameter name. After the analysis has completed, the modified parameter returns to its original value.

Although circuits can be well simulated for basic behavior, Cadence cannot predict phenomena such as long term-drift. This is because the software sweeps a temperature parameter while keeping the circuit fixed. With this type of simulation only a one-toone functional mapping is possible where temperature is the independent variable and the various parameters are the dependent variable. The phenomenon of long term drift is not a one-to-one functional mapping because we have to introduce time as an additional independent variable with temperature to take into account the variations that occur in time while keeping temperature fixed.

This is a huge limitation to circuit designers, which leads to production delay, as

11

additional precise experiments need to be conducted to identify the problem, track its root cause and propose a solution. Ultimately this becomes not just circuit designer’s burden, but also the project director’s, business managers’, investors’ and obviously the customers’. This is a huge loss for the company.

1.3

Thin-Film and Polysilicon Resistors

Resistors are key building blocks in mixed signal integrated circuits. The ways to avoid lifetime drift phenomena in resistors is heavily dependent on the process technology that is being used to fabricate the resistor. Thin-film and Polysilicon resistors are among the most common. Although in terms of quality, under the criteria of low/high frequency noise, low temperature coefficients, and tolerance, thin-film is much more desired than Polysilicon [2]. However, Polysilicon is used primarily due to its low cost, lead time and cycle time [3].

However, Polysilicon resistors have added effects such as low/high frequency noise, high temperature coefficients, tolerance and ultimately lifetime drift [4]. Much of these effects currently cannot be well predicted by default Cadence models. However it is possible to gather experimental data and create a customized model which can be imported to Cadence in order to take into account these additional effects to produce a more accurate prediction of circuit behavior under many more circumstances.

This would not only help in making better decisions during the circuit design phase, but can greatly reduce production delay, as problems could be predicted beforehand and corrected, reducing the need for additional empirical debugging. This greatly reduces productivity delay for both the company and the customer.

In next chapter, we describe how to experimentally measure lifetime-drift. In

Chapter 3, we create a mathematical model for lifetime drift by understanding the device physics. In Chapter 4, we simulate it in a Cadence’s circuit simulating environment. Finally in Chapter 5, we design a graphical user interface that will allow easy integration and simulation of lifetime drift.

12

Chapter 2

Measuring Lifetime Drift in RPH

Polysilicon Resistors

2.1

RPH Resistor Layout

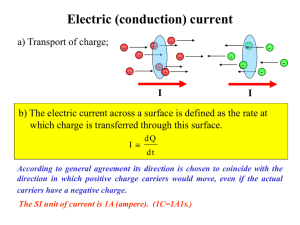

The high sheet resistance (RPH) polysilicon resistor has three terminals. The top two are connected to the p-type polysilicon segment shown in blue. And the third terminal is connected to the n-typed epi layer mounted on top of a p-typed substrate. This is shown in Figure 2.1. The equivalent circuit model depicting the three terminals are shown in Figure 2.2. This is the existing circuit model that is used in Cadence.

Figure 2-1: This is the circuit model for the RPH Polysilicon Resistor

13

Figure 2-2: This is the device cross-section and terminals of the RPH Polysilicon

Resistor

2.2

Experimental Setup

In measuring lifetime drift for resistors, the typical setup that is used involves a resistor divider, where the V

POS and V

NEG add up to zero. This is shown in Figure

2-3. The red numbers in the figure denote the voltage drop across the field oxide.

On average, R

1 has a -7.5V drop across the field oxide, while R

2

, -22.5V. This is referred as an asymmetrical divider, as the effective V epi of 7.5 and 22.5V differ in the two resistors. The relatively large value of V epi provides the fundamental driving force that causes the poly resistance to drift with time, and eventually saturates at a constant value. Unequal V epi also causes the resistor to drift by different amounts.

In this divider, R

1

' 19.1 kΩ and R

2

' 16.6 kΩ at room temp. We apply V

POS

=

15V and V

NEG

= -15V. The current flowing through these resistors is 0.84 mA, which is below I max of 1 mA (J max

= 0.5 mA/ µ m and these resistors have W=2 µ m). By solving for V mid using the Kirchoff’s Voltage Law in the resistor divider, we obtain:

V mid

= V pos

−

V pos

− V neg

1 +

R

2

R

1

(2.1)

In this experiment, we connect the backplate(V epi

) of the resistors to V

POS

= 15V shown. In this way, R

1 of this divider experiences an averaged V epi

= 7.5V, and R

2

,

22.5V.

14

Figure 2-3: Resistor divider setup for measuring the lifetime drift of V mid

2.3

Experimental Measurements

In step (A) after we bias the resistor pair with V epi

= 22.5V for 10 min, V mid does not change because the characteristic time constant τ

43 at 43 o

C is close to 105 hrs. As we heat up to 85 o C in step (B), we see that V mid changes by 14 mV after 50 min, and increases to 30 mV after close to 4 hrs of stressing. The characteristic time constant

τ

85 is around 5 hr at 85 o C. So it is estimated that 30 mV is near the maximum

∆V mid after stressing. In step (C) when we lower the temperature back to 43 o

C, the stress is remembered, and we observe a ∆V mid close to 30 mV. Figure 2-4 shows the measured response and Figure 2-5 shows the basic dependence of the characteristic time constant τ to V epi and temperature.

This memory effect is characteristic of lifetime drift. If V mid had returned back to it’s original value after cooling the circuit down, it would not be considered lifetime drift. The fact that we can see V mid increase in time at 85 o

C shows time dependence, characteristic of lifetime drift. Temperature has a greater impact in accelerating lifetime drift of V mid

, rather than in changing how much V mid drifts by.

At the beginning, V mid is about -0.965V, corresponding to a R

2

/R

1 ratio of 0.879.

In order to attain a 30 mV shift, the R

2

/R

1 ratio has to increase to 0.883. Therefore the R

2

/R

1 ratio has to increase by 0.883/0.879 = 1.0046. So R

2

, which experiences an averaged V epi

= 22.5V, increases by 0.73 %. We know that R

1

, which experiences

15

Figure 2-4: Describes the memory effect in RPH resistors. (A) Under normal temperatures, V mid is constant in time. (B) When held at a higher temperature, V mid

(C) When brought back down to original temperature, V mid drifts.

experiences lifetime drift as V mid is permanently higher than before

Figure 2-5: Shows the simplified dependence of characteristic time constant τ to V epi and Temperature an averaged V epi

= 7.5V will increase by a smaller fraction than at 22.5V. Therefore, we expect R to increase by 0.24 % for V epi

= 7.5V. Therefore, the final R

2

/R

1 ratio, based on device level data, is 1.0073/1.0024 = 1.0049. This is consistent with the resistor divider result of 1.0046.

16

Chapter 3

Device Physics of RPH Polysilcon

Resistors

3.1

Basic RPH Resistor Model

The basic structure of the RPH polysilicon resistor is shown in figure 3-1. The device has three terminals labeled n 1, n 2, and sub . The polysilicon is mounted on top of a silicon substrate. The distinctive feature of polysilicon, is it’s grains, and grain boundaries. These grains and grain boundaries are complex structures that consist of a few atomic layers of disordered atoms. They are transitional between different orientations of neighboring grains. Because of this irregular structure, carriers traps are a concern, unlike amorphous silicon. We will find that this granular structure is what gives rise to the lifetime drift found experimentally in Chapter 2.

17

Figure 3-1: This is the device cross-section and terminals of the RPH Polysilicon

Resistor showing the grain boundaries in the polysilicon layer

In order to create a mathematical model for the polysilicon resistor we have to look at it’s band structure, shown in figure 3-2.

Figure 3-2: This is the band diagram terminals of the RPH Polysilicon Resistor

The first thing we have to model is resistivity. Based on the Conduction Channel

18

Model [1] and Thermionic Emission(TE)-Thermionic Field Emission(TFE)-Thermionic

Field Emission Scattering(TFES) Model [5], resistivity can be written as [6]:

ρ = ρ

G

1 −

2 W + δ

L

+ ρ

GB

δ

L

+ ρ

B

2 W

L

(3.1)

Where:

ρ : Resistivity in polysilicon layer

ρ

G

: Resistivity in grain

ρ

B

: Resistivity of barrier

ρ

GB

: Resistivity of grain boundary

L : Grain length

W : Width of the depletion layer

δ : Width of amorphous grain boundary

Here we can see that we have taken into account resistivity in the grain, barrier and grain boundary in order to calculate the resistivity in the polysilicon layer.

After modeling resistivity in the polysilicon layer, we can proceed to modeling the total resistance. The approach will be to make a basic model without taking into account lifetime drift. Then we improve the model by incorporating lifetime drift.

And finally improve it even further by adding the second-order effects of heating.

We first start by looking at the different modes of operation in the polysilicon resistor. Normally, without applying a voltage on the substrate and simply setting it to ground, we only focus on the conduction inside the polysilicon layer. If the voltage on n2, V n 2 is greater than the voltage on n1, V n 1

, we have current flowing from n2 to n1. When we apply a voltage on the substrate we create a depletion layer in the polysilicon, shown in Figure 3-3.

19

Figure 3-3: Applying a voltage across the substrate causes a depletion region to form in the polysilicon that changes the effective resistance in the polysilicon layer

At constant current, the depletion layer effectively increases the current density, by deceasing the effective cross sectional area through which the current flows. If the effective area is reduced the overall resistance in the polysilicon layer is increased.

This effect can be modeled by a parameter, V

C 1

. The greater the average voltage applied between the polysilicon region and silicon subtrate, the greater the the overall resistance. The overall equation can be seen below:

R = R o

1 + V

C 1

R o

=

ρ L poly

A poly

( V n 1

− V sub

) + ( V n 2

2

− V sub

)

(3.2a)

(3.2b)

Where:

R : Total Resistance

R o

: Resistance due to ρ

V

C 1

: Takes into account the change in effective length and width of polysilicon due to formation of depletion layer

ρ : Resistivity of polysilicon

L poly

: Length of polysilicon

A poly

: Cross-sectional area of polysilicon through which current flows.

20

3.2

Physics of Lifetime Drift

Before creating the mathematical modeling of Lifetime, we take a closer look at the granular structure of polysilicon shown in figure 3-4.

Figure 3-4: Trapped Hydrogen lies within the granular structure of polysilicon. These are bonded to the silicon

As mentioned previously the granular structure of polysilicon makes it susceptible to trapped impurities. For the case of polysilicon, trapped hydrogen is an issue. This is hydrogen that is bonded to silicon. This arises from the usage of Silane (SiH

4

) in the chemical process of adding polysilicon on silicon wafers.

When a voltage is applied on the substrate, the trapped hydrogen moves in the direction of the electric field. The rate at which the hydrogen moves is dependent on the temperature and activation energy of the process. As bonds must be broken and reformed when the hydrogen moves and relocates, an activation energy is required.

This is depicted in figure 3-5.

21

Figure 3-5: Applying a voltage across the substrate causes the hydrogen to move, by bonding and de-bonding. This changes the band structure of the polysilicon layer which in turn changes the resistance

After sometime the hydrogen will try to settle back down to a more entropically favorable configuration, shown in figure 3-6.

Figure 3-6: After some time, the trapped hydrogen settles back down. Temperature affects how fast it takes to settle. However, the configuration before and after the applied voltage on the substrate is different. This permanently changes the band structure of the device, causing lifetime drift. This is what causes resistance to be different before and after burn-in

22

The key point of note after the hydrogen settles back down is that it is no longer in the same configuration as it began originally. Since the configuration of the hydrogen traps affects the band structure of the polysilicon, the resistance of the polysilicon is also affected. In other words, the resistance changes permanently after the hydrogen settles back down!

If we take a look at this diagram under the same context as the resistor divider in chapter 2, we notice that both resistors have a substrate that is connected to a positive voltage. This means, based on figure 3-5, that the trapped hydrogen will move. When we increase the temperature, we increase the rate at which the hydrogen re-configures. That means the band structure is changing and so the resistance of the device must change when held at a higher temperature. After the temperature cools down, the rate at which the trapped hydrogen re-configures is reduced. This causes the configuration of the hydrogen to no longer be the same as what it was initially.

This is precisely the reason why we observe the memory effect of RPH polysilicon, where the resistance is permanently altered to something different from nominal. This is the lifetime drift that we observe in RPH polysilicon resistors.

3.3

Modeling Lifetime Drift

Before incorporating lifetime drift into the mathematical model, some restrictions are imposed. We choose to focus on the amount of lifetime drift that occurs, rather than the time-dependent behavior or memory effect. From a circuit designer’s perspective, the lifetime drift of polysilicon resistors needs to be within a certain amount such that the circuit still operates properly in order to meet industry standards. It is not important how fast the lifetime drift occurs as the circuit is heated, but rather how much it drifted while held at a higher temperature. The resistance is different from nominal when cooled back down, because the resistance had drifted while held at a higher temperature. Cooling the circuit down only held that change in resistance.

That is why the amount of lifetime drift is more important to model than the timedependent behavior.

23

We start by adding V drif t to the previous equation 3.2a, in order to get the following:

R = R o

1 + ( V

C 1

+ V

Drif t

)

( V n 1

− V sub

) + ( V n 2

− V sub

)

2

(3.3)

Where:

R : Total Resistance

R o

: Resistance due to ρ

V

C 1

: Takes into account the change in effective length and width of polysilicon due to formation of depletion layer

V

Drif t

: takes into account the change in V

C 1 across polysilicon layer due to trapped hydrogen

The greater the average voltage between the polysilicon layer and silicon substrate the greater the drift of trapped hydrogen. Since there is more hydrogen in the polysilicon layer there is more scattering of electrons and holes leading to an increase in resistance. This effect can be modeled by the parameter, V

Drif t

.

If we wish to incorporate a time and temperature dependent effect we simply subtract from equation 3.3, ( R − R |

V

Drif t

=0

) exp

− t

τ

. This is shown below as:

R ( t ) = R − ( R − R |

V

Drif t

=0

)exp

1

τ ∝

T

− t

τ

(3.4a)

(3.4b)

Where:

R ( t ) : Time-dependent resistance

R : Resistance with V

Drif t

= 0

τ : Characteristic time constant of lifetime drift dependent on temperature.

T : Temperature

So at t = 0, the the resistance is R |

V

Drif t

=0

, the resistance with no lifetime drift and at a t >> τ , the resistance is R , the resistance with drift. Which is what we

24

expect. Now, τ is a function of temperature. We expect that it takes longer for the resistance to drift at lower temperature than higher temperatures so τ must be inversely proportional to temperature.

3.4

Modeling 2nd-Order Effects

While resistance is affected by mode of operation and lifetime drift of trapped hydrogen, the polysilicon also heats up. Self-heating of the polysilicon causes thermal expansion which in-turn changes the resistance of the device. The temperature coefficient of resistance is what is necessary here labeled T c

. Using this, we can look at the change in resistance shown below.

∆ R

Heat

= R T c

∆ T

∆ T = P R th

P =

( V n 2

− V n 1

)

2

R

∆ R

Heat

= V

C 2

( V n 2

− V n 1

)

2

V

C 2

=

T c

R th

R

Where:

∆ R

Heat

: Change in resistance due to self-heating

T c

: Temperature coefficient

∆ T : Change in temperature

P : Power dissipated across polysilicon layer

R th

: Thermal resistance

R : Total resistance

V

C 2

: Takes into account the change in resistance due to self-heating

The change in temperature can be related to the power and thermal resistance of the device. Using this we can rewrite equation 3.5a, in terms of voltages at nodes

25

(3.5a)

(3.5b)

(3.5c)

(3.5d)

(3.5e)

n1, n2 and sub while incorporating the thermal effects in V

C 2 and add this to our previous equation for total resistance shown below.

R = R o

1 + ( V

C 1

+ V

Drif t

)

( V n 1

− V sub

) + ( V n 2

2

− V sub

)

1 + V

C 2

( V n 2

− V n 1

)

2

(3.6)

Where:

R : Total Resistance

R o

: Resistance due to ρ

V

C 1

: Takes into account the change in effective length and width of polysilicon due to formation of depletion layer

V

Drif t

: takes into account the change in V

C 1 across polysilicon layer due to trapped hydrogen

V

C 2

: Takes into account the change in resistance due to self-heating

3.5

Complete RPH Resistor Model

We have now incorporated all of the aspects necessary to mathematically modeling the effect of lifetime drift on the resistance of RPH polysilicon resistors. The complete model is shown below.

R = R o

1 + ( V

C 1

+ V

Drif t

)

− t

R ( t ) = R − ( R − R |

V

Drif t

=0

)exp

τ

( V n 1

− V sub

) + ( V n 2

− V sub

)

2

(3.7a)

1 + V

C 2

( V n 2

− V n 1

)

2

(3.7b)

Where:

R ( t ) : Time-dependent resistance

R : Total Resistance with V

Drif t

= 0

R o

: Resistance due to ρ

26

V

C 1

: Takes into account the change in effective length and width of polysilicon due to formation of depletion layer

V

Drif t

: takes into account the change in V

C 1 across polysilicon layer due to trapped hydrogen

V

C 2

: Takes into account the change in resistance due to self-heating

τ : Characteristic time constant of lifetime drift dependent inversely on temperature.

We will use this mathematical model to create a circuit model in Cadence so we can simulate lifetime drift during the circuit phase design in the next chapter.

27

28

Chapter 4

Simulating RPH Resistor Lifetime

Drift in Cadence

4.1

Previous RPH Resistor Modeling Scheme

Now that we have created a mathematical model for the RPH resistor, we can now proceed to incorporate this mathematical model into Cadence. But before that, we need to take a look at the limitations of Cadence and the previous RPH modeling scheme as well as how lifetime drift is treated by circuit designers prior to our modeling scheme. In previous modeling schemes, any form of resistance drift not limited to RPH is treated as a process variation, not a lifetime effect. That means resistance variations were handled by corner models, or time-independent variations. The major problem with this modeling scheme is that it leads circuit designers believe that that such a variation can be trimmed out, or adjusted through the use of digitally controlled potentiometers. Figure 4-1 shows such a potentiometer.

29

Figure 4-1: This is a digitally controlled potentiometer. A Digital value is loaded into memory and decoded to select which switches to turn on/off in order to attain a range of resistance values.

The problem is that there is no way to remove lifetime drift simply by trimming out the resistance. What’s worse is that lifetime drift is not modeled as a time dependent resistor, so transient simulations fail to reveal the time-dependent behavior.

That means the only way lifetime drift can be detected is from lab experiment after the circuit has undergone a burn-in. Since a burn-in is a standard process that all circuit designs have to pass, the circuit will return to the designer unable to pass the requirements due to lack of insight during design phase. This leads to time being wasted trying to find the source of lifetime drift and to solve the issue.

4.2

Simulations of RPH Resistor Lifetime Drift

In order to address these issues, lifetime drift in RPH polysilicon resistors must be modeled as a time-dependent resistor. The greatest difficulty in creating a timedependent resistor in Cadence, is that there is no way to make it using only the programming language of the modeling library, Spectre. While Spectre can create transient solutions with capacitors and inductors, it can only create resistors dependent on currents, voltages, derivatives or integrals of currents, derivatives or integrals

30

of voltages. There is no way to create a resistor dependent on simulation time. In order to do this, Verilog-A resistor was instantiated in the Spectre Modeling Library.

Verilog-A is capable of modeling resistors dependent on simulation time. Using the complete mathematical model of the RPH resistor created in chapter 3, the model for RPH polysilicon resistor incorporating lifetime drift was created.

In order to test whether we can see the lifetime drift, we set up the resistor divider described on chapter 2. The schematic is shown in figure 4-2.

Figure 4-2: This same exact resistor divider as chapter 2, constructed in cadence.The

one on the right is the existing RPH resistor model that doesn’t incorporate lifetime drift. The one on the left is the newly modeled RPH resistor that contains the effects of lifetime drift. We will be comparing V mid and V midrph in time

The one on the right is the existing RPH resistor model that doesn’t incorporate lifetime drift. The one on the left is the newly modeled RPH resistor that contains the effects of lifetime drift. In order to compare the two resistor models with each other we do a transient analysis of the circuit at 85 o C specifically comparing V mid and V midrph in time. The plots are shown in figure 4-3.

31

Figure 4-3: These are plots of V mid

(top and blue) and V midrph

(bottom and red) in time at 85 o C.

V midrph uses the existing model that incorporated no lifetime drift.

V mid uses the model we created that incorporates lifetime drift. The existing model,

V midrph does not simulate lifetime drift, but our model does

The red flat line near the bottom of the graph is V midrph

, which uses the existing model that incorporated no lifetime drift. The blue curved line on the top is V mid

, which uses the model we created that incorporates lifetime drift. We know based on the data collected in chapter 2, that the voltage between the two resistors must change in time, which is precisely what we get in our model, V mid in blue. But you can clearly see that the existing model has no time-dependent effect. Which is why circuit designers incorrectly believe that a digitally controlled potentiometer can compensate for lifetime drift.

32

4.3

Simulation of RPH Resistor Lifetime Drift in

Non-inverting Operational Amplifier

Although the example resistor divider in chapter 2 clearly showcases lifetime drift, such simple circuits aren’t too sensitive to such minor changes in resistance. Most analog circuits require differential amplifiers in a feedback loop configuration in order to provide gain, stability, buffering, power etc. But the amount of gain, frequency response, stability, and power is highly dependent on the resistance of the resistors that are used. If any of these resistors experience lifetime drift, the circuit would experience gain mismatch, loss of quality factor, instability and power loss that may ultimately damage the circuit and cause it to permanently fail. These types of circuits are highly sensitive to lifetime drift of resistors. It would be much more impacting to show lifetime drift in the simulation of an op-amp that uses a feedback resistor. A commonly used non-inverting op-amp circuit is shown below in figure 4-4.

The resistor on the top is a digitally controlled potentiometer made with ideal resistors, and on the bottom we have an RPH resistor with lifetime drift. We have set the trim code such that the top resistor is initially 8KΩ and the bottom 2.9KΩ. The supply voltages top to bottom are 15V and -15V, respectively. The input voltage is

2V. So we expect V outtrim

= V in

1 +

R trim

R rph

= 7 .

51 V initially. The typical simulation for such a setup, would require ramping the supply voltages until the output is 7.51

V. Then in this example, at a later time, we trim the top resistor until the output is

8 V. What circuit designers would like to see after trimming is completed is for the output voltage to be fixed at 8V. But with lifetime drift, this is not the case shown in figure 4-5.

33

Figure 4-4: This is a basic non-inverting op-amp, with 15V and -15V supplies and a

2 V input. The top resistor is a digitally controlled potentiometer made with ideal resistors, and the bottom is our RPH resistor with lifetime drift. We are looking at the output V outtrim in time

34

Figure 4-5: Since the supply rails are ramped, V outtrim also ramps until the output is 7.51 V and settles. At this point, we have not placed the circuit for burn-in so there should not be any drift. Then, we trim the top resistor until the output is 8 V.

Again, there should not be any drift as the circuit was not in burn-in. We apply the drift model after the trimming is conducted because burn-ins are conducted after the circuit has the desired output. We can clearly see that lifetime drift is not a process variation that can be trimmed out.

This example clearly demonstrates that lifetime drift is not a process variation that can be trimmed out, but a lifetime effect.

4.4

Impact of Simulating RPH Resistor Lifetime

Drift

Even though, our model clearly demonstrates the change in resistance at higher temperatures, our model does not show the memory effect which occurs after cooling down, because the change in resistance that occurs at higher temperature would remain when cooled down. So it is apparent to the designer that lifetime drift is an

35

issue. If the resistance did not vary when held at a higher temperature, then we would know that the resistance would not be different if we cooled it down as it never changed in in the first place. So there is no need to model the memory effect.

So our model for the first time, can simulate lifetime time drift effect in transient simulations on Cadence. Our model does not treat as a process variation that can be trimmed out by digitally controlled potentiometers, but rather as a lifetime effect.

With this model, circuit designers can see in the design phase whether lifetime drift is an issue or not, before having to send in their whole circuit for burn-in.

Although, we can see lifetime drift in the design phase, we have only created a model for RPH polysilicon resistors. Lifetime drift is an issue in many other devices as well. It would be much more beneficial to create a framework through which any type of lifetime drift can be incorporated into cadence. In chapter 5, we create a graphical user interface through which designers can easily incorporate lifetime drift into their simulations without having to replace all of their device models.

36

Chapter 5

Design of GUI Utility For Quick

Integration in Design Phase

5.1

Motivation

In order to create a utility to make it easier for designers to visualize lifetime drift, we must make sure that our utility is a graphical user-interface (GUI). One of the biggest issues with incorporating a new device model is having to change the design of the entire circuit, replacing all of the no-drift modeled resistors with drift modeled resistors. It would be optimal to have a way such that the designer doesn’t have to make changes to their design. The best way to do this is to create a utility which is programmed to automatically replace the instantiated non-drift model file with drift model file in the ocean script. In addition, often times simulations have a start-up sequence, where power supplies are ramped. In such circumstances, it takes some amount of time for the circuit to fully settle. It would be convenient for a designer, if we can specify at what time we wish to switch from the non-drift resistor to the drift resistor. Since lifetime drift only occurs when a circuit is placed for burn-in, there is no need to use the lifetime drift at the start-up sequence, as it is a longterm model. Although the amount of drift is dependent on the equations modeled, the characteristic time constant for lifetime drift may have variation from lot-to-lot dependent on process. So it would be convenient if there is an option to specify the

37

scale of our time constant. Finally, Lifetime drift is an issue in many other devices as well. It would be much more beneficial to create a framework through which any type of lifetime drift can be incorporated into cadence. These aspects together are incorporated in the basic layout of the GUI shown in Figure 5-1.

Figure 5-1: This is the basic layout of out GUI. It takes as an input an ocean script file generated from cadence for the specific circuit to be tested. The user selects what drift model resistor (RPH in this case), what start time in order to turn on the drift model and scale factor pertaining to the time constant specific to the drift need to be simulated. The ”Run” button is pressed and the output is a graph showing outputs specified in the ocean file with lifetime drift taken into account

5.2

Graphical User Interface Design

The design of our GUI takes as an input an Ocean Script file(.ocn) of the prepared transient simulation. Then the user selects at what time to apply the drift model.

The drift model file contains a time parameter that is set by the user to simulate start of drift. The scale factor sets the time constant of the characteristic lifetime drift to be simulated. This is not limited to RPH lifetime drift and can be extended to include other models as well such as BJTs and MOS devices. The output of the drift utility is a transient simulation plot that shows the effects of lifetime drift. Figure

5-2 shows how the GUI translates to the graph of the simulation.

38

Figure 5-2: The start time is typically after trimming is conducted and the scale factor adjust the time constant specific to the device as indicated by the arrows

In order to program this GUI we require three pertinent scripting languages:

Ocean for the GUI, Spectre for the Model file, and Verilog-A in order to program time dependent effects in Spectre. The basic block diagram for our code and the types of inputs/files that it needs to interact with is shown in figure 5-3.

Figure 5-3: This is the block diagram showing inputs/files used for our code. The inputs are Ocean script for the specific circuit to be tested and the start and scale times. The output is a graph plotted in cadence. The GUI interacts with Spectre

Model file, and Verilog-A in order to program time dependent effects in Spectre.

39

The Ocean script is generated by netlisting a desired circuit design on Cadence and is required. The inputs are the type of device to model drift for, the time after which we want of apply the drift model, and the time constant pertinent to lifetime drift which we would like to simulate.

5.3

Graphical User Interface Functionality

The GUI basically looks at the netlist files and searches for the RPH resistor instantiated and replaces it with the RPH resistor model we created that incorporates lifetime drift. Then it sets our desired input values for drift start and time constant for the parameters in our model file. When the ”run” button is pressed, it generates a netlist that is the exact same as the input except with only the pointer to the rph model file replace with a pointer to the RPH model file with lifetime drift. Cadence then runs the new netlist which calls the Spectre model library for each device. When it calls the RPH resistor, the Spectre file calls Verilog-A in order to simulate time-dependent behavior for the RPH. After this is completed, a graph is finally generated which shows the same exact graph as figure 5-2.

The key benefits of this framework is that a designer doesn’t have to make changes to their design. They can just run this GUI on their un-modfied circuit netlist and the utility just replaces the non-drift model file with drift model file in the ocean script and runs it. Lifetime drift can now finally be transparent to designers. But what is key here is that the model file we created is for RPH. It can easily be changed with different equations to include lifetime drift in for example BJTs. All one would have to do is create that model file and alter the GUI code so that it searches for

BJT files and replaces all of them to a new pointer pointing to the new BJT model file created. So this utility is not limited to RPH drift and can be extended to include other models like BJT. This is extremely beneficial to industry. Lifetime drift can be detected without lab experiment before design is completed. Designs will have a better chance to pass specs requirements. Designers can have more insight on lifetime drift during the design phase.

40

Chapter 6

Concluding Remarks

6.1

Conclusion

We measured lifetime drift by looking at the mid point voltage of a resistor divider.

We noticed that at room temperature the resistance is constant in time. But when held at a higher temperature, resistance changes in time. That change in resistance is seen when cooled down as the memory effect, where the resistance was not the same before and after the burn-in procedure.

The reason lifetime drift occurs in RPH polysilicon resistors is due the redistribution of trapped Hydrogen. When a voltage is applied on the substrate, the trapped hydrogen move in the direction of the electric field. The rate at which the hydrogen move is dependent on the temperature. As bonds must be broken and reformed when the hydrogen move and relocated. After the hydrogen settles back down, it is no longer in the same configuration as it began originally. Since the configuration of the hydrogen traps affects the band structure of the polysilicon, the resistance of the polysilicon changes permanently.

After developing our lifetime drift model for the RPH resistor, we were able to, for the first time, simulate lifetime drift simulations on cadence. Lifetime drift is not treated as a process variation that can be trimmed out by digitally controlled potentiometers, but rather as a lifetime effect. With this model, circuit designers can see in the design phase whether lifetime drift is an issue or not, before having to send

41

in their whole circuit burn-in.

We created a utility to make it easier for designers to visualize lifetime drift through a graphical user-interface (GUI). A designer doesn’t have to make changes to their design. They can just run this GUI on their un-modified circuit netlist and the utility just replaces the non-drift model file with drift model file in the ocean script.

Lifetime drift can be detected without lab experiment before design is completed.

Designs will have a better chance to pass specs requirements.

6.2

Future Work

Since I have only modeled one specific type of lifetime drift for the case of RPH resistor, I would like to model other types of lifetime drift for different devices. This would involve refining the accuracy of drift models for very large scale integration.

The bigger goal would be to create a general framework through which other nonideal device effects can become transparent to a circuit designer. This would allow for a much easier way to integrate non-ideal effects without having to waste valuable time trying to find a way to model each and every non-ideal effect in a different way.

42

Appendix A

Spectre Model File Code for RPH

Resistor

// * Mandatory commented line to begin file simulator lang=spectre library s18_rc

// ********************************************************************

// ********************************************************************

// ** **

// **

// ** libraries in the model files **

**

// **

// **

// **

// **

.lib

.lib

.lib

.lib

r_typ r_high r_low res

// **

// **

// **

// **

.lib

c_typ

// ** .lib

c_high

// ** .lib

c_low

.lib

cap typical corner model high(large value) resistor model low(low value) resistor model main resistor model libaray typical corner model high(large value) cap model low(low value) cap model main cap model libaray

**

**

**

**

**

**

**

**

**

**

43

// ********************************************************************

// ********************************************************************

// ********************************************************************

// ********************************************************************

// **

// **

// **

// ** corner model library

**

**

**

**

// ********************************************************************

// ********************************************************************

// ** **

// **

// ** typical corner library: r_typ **

**

// ********************************************************************

// * section r_typ

// Random function for lot variation real aunif_r(real unif_rand,real val_typ,real val_range) { return (val_typ+val_range*unif_rand)

} parameters rr_lot=0 statistics { process { vary rr_lot dist=unif N=1

}

} real gauss_rr(real gauss_rand, real val_typ, real per_range, real f) { return (val_typ+gauss_rand*per_range*f)

} parameters rrr_lot=0

44

statistics { process { vary rrr_lot dist=gauss std=1

}

}

// * parameters maxlot_r=1

// ** monte carlo matching for thin film resistors parameters dtf=12.7e-9 drp=10.0e-9 drps=18.7e-9 drph=11.02e-9 drphn=14e-9 parameters dm1=20e-9 dm2=25e-9 dm3=25e-9 dtm=50e-9

// ** thin film resistor: f corner parameter parameters rhotfnom=3000 rhotf_lot=aunif_r(rr_lot,3000,600*maxlot_r) parameters rhotf=rhotf_lot parameters dwtfnom=0 dwtf_lot=aunif_r(rr_lot,0,0.1e-6*maxlot_r) dwtf=dwtf_lot parameters dltf0=-0.0625e-6 dltf10=-0.09357e-6 dltf=0 dsqtf=0 parameters tc2f=3.75e-8

// ** unsalicaide poly resistor: rp corner parameter parameters rhorpnom=260 rhorp_lot=aunif_r(rr_lot,260,52*maxlot_r) parameters rhorp=rhorp_lot parameters dwrpnom=0.020e-6 dwrp_lot=aunif_r(rr_lot,0.020e-6,0.06e-6*maxlot_r) parameters dwrp=dwrp_lot parameters rctrpnom=112.5e-6 rctrp_lot=aunif_r(rr_lot,112.5e-6,22.5e-6*maxlot_r) parameters rctrp=rctrp_lot parameters tc1rp_lot=aunif_r(rr_lot,-25e-6,-200e-6*maxlot_r) tc1rp=tc1rp_lot parameters tc1rpct_lot=aunif_r(rr_lot,-1400e-6,-1400e-6*250/875*maxlot_r) parameters tc1rpct=tc1rpct_lot parameters fvc2rp=1 parameters rpdriftp=0 parameters rpdriftn=0

// **+ dwrpnom=0 dwrp=0

45

// ** high value poly resistor: rph corner parameter parameters rhorphnom=1000 rhorph_lot=aunif_r(rr_lot,1000,150*maxlot_r) parameters rhorph=rhorph_lot parameters dwrphnom=0.03e-6 dwrph_lot=aunif_r(rr_lot,0.03e-6,0.6e-7*maxlot_r) parameters dwrph=dwrph_lot parameters tc1rph=-875e-6 parameters fvc2rph=1 parameters rphdriftp=0 parameters rphdriftn=0

// ** narrow high value poly resistor: rphn corner parameter parameters rhorphnnom=1550 rhorphn_lot=aunif_r(rr_lot,1550,620*maxlot_r) parameters rhorphn=rhorphn_lot parameters dwrphnnom=0e-6 dwrphn_lot=aunif_r(rr_lot,0e-6,0e-7*maxlot_r) parameters dwrphn=dwrphn_lot parameters tc1rphn=-1100e-6 parameters fvc2rphn=1 parameters rphndriftp=0 parameters rphndriftn=0

// ** salicaide poly resistor: rps corner parameter parameters rhorpsnom=8 rhorps_lot=aunif_r(rr_lot,8,5*maxlot_r) parameters rhorps=rhorps_lot parameters dwrpsnom=-0.014e-6 dwrps=-0.014e-6

// **+ dwrpsnom=0 dwrps=0

// ** metal 1 resistor: m1 corner parameter parameters rhom1nom=85e-3 rhom1=85e-3 dwm1nom=0 dwm1=0

// ** metal 2 resistor: m2 corner parameter parameters rhom2nom=85e-3 rhom2=85e-3 dwm2nom=0

// ** metal 3 resistor: m3 corner parameter parameters rhom3nom=85e-3 rhom3=85e-3

// ** top metal resistor: mt corner parameter dwm3nom=0 dwm2=0 dwm3=0

46

parameters rhomtnom=8e-3

// **

// **

// ** tsv50 corner parameters ls_tsv50=20.3e-12 parameters rs_tsv50=4.6e-3 parameters cs_tsv50=110e-15

// **

// ** tsv20 corner rhomt=8e-3 dwmtnom=0 dwmt=0 parameters ls_tsv20=46e-12 parameters rs_tsv20=5.9e-3 parameters cs_tsv20=140e-15

// **

// include "s18_rc.scs" res endsection r_typ

// *

// ********************************************************************

// **

// ** high corner library: r_high

**

**

// ** **

// ********************************************************************

// * section r_high

// Random function for lot variation real aunif_r(real unif_rand,real val_typ,real val_range) { return (val_typ+val_range*unif_rand)

} parameters rr_lot=0 statistics { process {

47

vary rr_lot dist=unif N=1

}

} real gauss_rr(real gauss_rand, real val_typ, real per_range, real f) { return (val_typ+gauss_rand*per_range*f)

} parameters rrr_lot=0 statistics { process { vary rrr_lot dist=gauss std=1

}

}

// * parameters

// ** monte carlo matching for thin film resistors parameters dtf=12.7e-9 drp=10.0e-9 drps=18.7e-9 drph=11.02e-9 drphn=14e-9 parameters dm1=20e-9 dm2=25e-9 dm3=25e-9 dtm=50e-9

// ** thin film resistor: f corner parameter parameters rhotfnom=3000 rhotf=3600 parameters dltf0=-0.075e-6 parameters tc2f=5.59e-8 dwtfnom=0 dwtf=0.10e-6 dltf10=-0.168e-6 dltf=-0.1e-6 dsqtf=0.35

// ** unsalicaide poly resistor: rp corner parameter parameters rhorpnom=260 rhorp=312 dwrpnom=0.020e-6 dwrp=0.080e-6 parameters rctrpnom=112.5e-6 rctrp=135e-6 parameters tc1rp=-225e-6 parameters tc1rpct=-1400e-6*1125/875 parameters fvc2rp=225/25 parameters rpdriftp=1e-2 parameters rpdriftn=-0.25e-2

// ** high value poly resistor: rph corner parameter

48

parameters rhorphnom=1000 rhorph=1150 parameters tc1rph=-1125e-6 parameters fvc2rph=1125/875 parameters rphdriftp=2e-2 dwrphnom=0.03e-6 dwrph=0.09e-6 parameters rphdriftn=-0.5e-2

// ** narrow high value poly resistor: rphn corner parameter parameters rhorphnnom=1550 rhorphn=2170 dwrphnnom=0e-6 dwrphn=0e-6 parameters tc1rphn=-1600e-6 parameters fvc2rphn=1600/1100 parameters rphndriftp=2e-2 parameters rphndriftn=-0.5e-2

// ** salicaide poly resistor: rps corner parameter parameters rhorpsnom=8 rhorps=12 dwrpsnom=-0.014e-6 dwrps=-0.014e-6

// ** metal 1 resistor: m1 corner parameter parameters rhom1nom=85e-3 rhom1=100e-3 dwm1nom=0

// ** metal 2 resistor: m2 corner parameter parameters rhom2nom=85e-3 rhom2=100e-3 dwm2nom=0 dwm1=0 dwm2=0

// ** metal 3 resistor: m3 corner parameter parameters rhom3nom=85e-3 rhom3=100e-3 dwm3nom=0

// ** top metal resistor: mt corner parameter parameters rhomtnom=8e-3 rhomt=10e-3 dwmtnom=0

// **

// **

// ** tsv50 corner parameters ls_tsv50=20.3e-12 parameters rs_tsv50=10.0e-3 parameters cs_tsv50=200e-15

// **

// ** tsv20 corner parameters ls_tsv20=46e-12 dwm3=0 dwmt=0

49

parameters rs_tsv20=7.40e-3 parameters cs_tsv20=175e-15

// **

// include "s18_rc.scs" res endsection r_high

// *

// ********************************************************************

// ** **

// ** low corner library: r_low **

// ** **

// ********************************************************************

// * section r_low

// Random function for lot variation real aunif_r(real unif_rand,real val_typ,real val_range) { return (val_typ+val_range*unif_rand)

} parameters rr_lot=0 statistics { process { vary rr_lot dist=unif N=1

}

} real gauss_rr(real gauss_rand, real val_typ, real per_range, real f) { return (val_typ+gauss_rand*per_range*f)

} parameters rrr_lot=0 statistics { process { vary rrr_lot dist=gauss std=1

50

}

}

// * parameters

// ** monte carlo matching for thin film resistors parameters dtf=12.7e-9 drp=10.0e-9 drps=18.7e-9 drph=11.02e-9 drphn=14e-9 parameters dm1=20e-9 dm2=25e-9 dm3=25e-9 dtm=50e-9

// ** thin film resistor: f corner parameter parameters rhotfnom=3000 rhotf=2400 dwtfnom=0 dwtf=-0.10e-6 parameters dltf0=-0.05e-6 dltf10=-0.019e-6 dltf=0.1e-6 dsqtf=-0.35

parameters tc2f=2.31e-8

// ** unsalicaide poly resistor: rp corner parameter parameters rhorpnom=260 rhorp=208 dwrpnom=0.020e-6 dwrp=-0.040e-6 parameters rctrpnom=112.5e-6 rctrp=90e-6 parameters tc1rp=175e-6 parameters tc1rpct=-1400e-6*625/875 parameters fvc2rp=1 parameters rpdriftp=0.5e-2 parameters rpdriftn=-0.5e-2

// ** high value poly resistor: rph corner parameter parameters rhorphnom=1000 rhorph=850 dwrphnom=0.03e-6 dwrph=-0.03e-6 parameters tc1rph=-625e-6 parameters fvc2rph=625/875 parameters rphdriftp=1e-2 parameters rphdriftn=-1e-2

// ** narrow high value poly resistor: rphn corner parameter parameters rhorphnnom=1550 rhorphn=930 dwrphnnom=0e-6 dwrphn=0e-6 parameters tc1rphn=-600e-6 parameters fvc2rphn=600/1100 parameters rphndriftp=1e-2

51

parameters rphndriftn=-1e-2

// ** salicaide poly resistor: rps corner parameter parameters rhorpsnom=8 rhorps=3 dwrpsnom=-0.014e-6 dwrps=-0.014e-6

// ** metal 1 resistor: m1 corner parameter parameters rhom1nom=85e-3 rhom1=60e-3

// ** metal 2 resistor: m2 corner parameter dwm1nom=0 dwm1=0 dwm2=0 parameters rhom2nom=85e-3 rhom2=60e-3

// ** metal 3 resistor: m3 corner parameter parameters rhom3nom=85e-3 rhom3=60e-3 dwm2nom=0 dwm3nom=0 dwm3=0

// ** top metal resistor: mt corner parameter parameters rhomtnom=8e-3 rhomt=6e-3 dwmtnom=0

// **

// **

// ** tsv50 corner parameters ls_tsv50=20.3e-12 parameters rs_tsv50=4.6e-3 parameters cs_tsv50=110e-15 dwmt=0

// **

// ** tsv20 corner parameters ls_tsv20=46e-12 parameters rs_tsv20=5.9e-3 parameters cs_tsv20=140e-15

// **

// include "s18_rc.scs" res endsection r_low

// *

// ********************************************************************

// **

// **

// ** typical corner library: c_typ

**

**

**

52

// ******************************************************************** section c_typ

// Random function for lot variation real aunif_c(real unif_rand,real val_typ,real val_range) { return (val_typ+val_range*unif_rand)

} parameters cr_lot=0 statistics { process { vary cr_lot dist=unif N=1

}

} parameters dmm=20.0e-9

// * corner of mim cap ** parameters cmm_cscale=1 tc1_mim=28.5e-6 dwl_mim=0.02e-6

// * corner of cxfpe_int parameters cxfpe_cscale=1

// *

// * pa1c unit-cell corner parameters c_1c_unit=0.45e-9 parameters tc1_1c=2.7e-4 parameters vc1_1c=-5e-5 parameters vc2_1c=2.6e-4

// * pa2c unit-cell corner parameters c_2c_unit=0.89e-9 parameters tc1_2c=2.7e-4 parameters vc1_2c=-5e-5 parameters vc2_2c=2.6e-4

// include "s18_rc.scs" section=cap endsection c_typ

53

// ********************************************************************

// ** **

// **

// ** low corner library: c_low **

**

// ******************************************************************** section c_low parameters dmm=20.0e-9

// * corner of mim cap ** parameters cmm_cscale=0.85

tc1_mim=0.0e-6 dwl_mim=0.08e-6

// * corner of cxfpe_int parameters cxfpe_cscale=0.85

// *

// * pa1c unit-cell corner parameters c_1c_unit=0.36e-9 parameters tc1_1c=2.7e-4 parameters vc1_1c=-5e-5 parameters vc2_1c=2.6e-4

// * pa2c unit-cell corner parameters c_2c_unit=0.71e-9 parameters tc1_2c=2.7e-4 parameters vc1_2c=-5e-5 parameters vc2_2c=2.6e-4

// include "s18_rc.scs" section=cap endsection c_low

// ********************************************************************

// **

// ** high corner library: c_high

// ** **

// ******************************************************************** section c_high

**

**

54

parameters dmm=20.0e-9

// * corner of mim cap ** parameters cmm_cscale=1.15

tc1_mim=100.0e-6 dwl_mim=-0.04e-6

// * corner of cxfpe_int parameters cxfpe_cscale=1.15

// *

// * pa1c unit-cell corner parameters c_1c_unit=0.54e-9 parameters tc1_1c=2.7e-4 parameters vc1_1c=-5e-5 parameters vc2_1c=2.6e-4

// * pa2c unit-cell corner parameters c_2c_unit=1.1e-9 parameters tc1_2c=2.7e-4 parameters vc1_2c=-5e-5 parameters vc2_2c=2.6e-4

// include "s18_rc.scs" section=cap endsection c_high

// *********************************************************************

// **

// ** main resistor models: res1 nr=1 crc parasicit model

**

**

// ** **

// *********************************************************************

// * section res1 real gauss_r(real gauss_rand, real val_typ, real per_range, real f) { return (val_typ+gauss_rand*per_range*f)

}

// Random function definition for TF resistor mismatch parameters tf_mis_rand=0

55

statistics { mismatch { vary tf_mis_rand dist=gauss std=1

}

} real unif_r(real unif_rand, real val_typ, real per_range, real f) { return (val_typ+unif_rand*per_range*f)

} parameters ur_mis=0 statistics { mismatch { vary ur_mis dist=unif N=1

}

} real sgn_r(real x) { return ((x==0)*0+(x>0)-(x<0))

} real gt_r(real x, real y) { return (sgn_r(max(x,y)-y))

} real lt_r(real x, real y) { return (sgn_r(y-min(x,y)))

} real gte_r(real x, real y) { return (1-sgn_r(y-min(x,y)))

} real lte_r(real x, real y) { return (1-sgn_r(max(x,y)-y))

} real noteql_r(real x, real y) {

56

return (abs(sgn_r(x-y)))

} real equal_r(real x, real y) { return (1-abs(sgn_r(x-y)))

} real mod_r(real x, real y) { return (x-int(x/y)*y)

} real trunc_r(real x) { return (int(x))

} real bang_r(real x) { return (equal_r(x,0))

} real floor_r(real x) { return (lt_r(x,0)*int(x-1)+gte_r(x,0)*int(x))

} real mina_r(real x,real y,real delta) { return (x+y-sqrt((x-y)*(x-y)+delta))/2

} real maxa_r(real x,real y,real delta) { return (x+y+sqrt((x-y)*(x-y)+delta))/2

} real bounda_r(real x,real maxval,real minval,real delta) { return maxa_r(mina_r(x,maxval,delta),minval,delta)

}

// *

//modeloptions_rc_tnom10 options dcmmod=0

// .options tnom=33

// *.param gt_r(x,y)=’(sgn_r(max(x,y)-y))’ lt_r(x,y)=’(sgn_r(y-min(x,y)))’

57

+

+

+

+

+

+

+

+

+

+

+

+

// *+ gte_r(x,y)=’(1-sgn_r(y-min(x,y)))’

// *+ lte_r(x,y)=’(1-sgn_r(max(x,y)-y))’ noteql_r(x,y)=’(abs(sgn_r(x-y)))’

// *+ equal_r(x,y)=’(1-abs(sgn_r(x-y)))’

// *+ mod_r(x,y)=’x-int(x/y)*y’ bang_r(x)=’equal_r(x,0)’

// *+ floor_r(x)=’(lt_r(x,0)*int(x-1)+gte_r(x,0)*int(x))’

// *+ mina_r(x,y,delta)=’(x+y-sqrt((x-y)*(x-y)+delta))/2’

// *+ maxa_r(x,y,delta)=’(x+y+sqrt((x-y)*(x-y)+delta))/2’

// *+ bounda_r(x,maxval,minval,delta)=

’maxa_r(mina_r(x,maxval,delta),minval,delta)’

// *

// ************************************

// * rph: high value poly resistor model *

// ************************************ subckt rph ( n1 n2 sub ) ahdl_include "myresistor_EDIT.va" parameters w=1e-6 l=5e-6 rreq=5000 ma=1 nsig=0 bvca=8.5 lpe=0

+ layout=pow(abs(ma),sgn_r(ma)) dl=-0.04225e-6 v_cal=rreq*layout l_cal=v_cal/rhorphnom*(w-2*dwrphnom) pors=(1-sgn_r(ma))/2 v_l=pow(abs(ma),pors) pt=temp pvcp1=-5e-002 pgvc1=0.

pvcp2=2.979e-006 pvcp3=-1.486e+000 nseries=(abs(ma)-ma)/2+(sgn_r(ma)+1)/2 pgvc2=fvc2rph*1/(nseries*nseries)*

(248946/(l*l*1e12)+37.685)/(0.6+0.9/(w*1e6))*1e-6*0.8

ptcp1=tc1rph ptcp2=2.06e-006 tfacp=1.0+ptcp1*(pt-33.0)+ptcp2*(pt-33.0)*(pt-33.0)

58

+

+

+

+

+

+

+

+

+ pvcpde=-1.8e-4*(w+5.5e-6)/(w+3e-6) slopehalfdrift=0.1e-2/2 deltadrift=4e-6 vmis=drph/sqrt(2*w*l*abs(ma)) rrphmc=gauss_r(tf_mis_rand,0,1,1) rrphmis=rrphmc*vmis*(1-sgn_r(abs(nsig)))+nsig*vmis val=rhorph*l_cal/(w-2*dwrph)*tfacp/layout af_ex=1.96352+(-92.4185e-3*(1e-6/w))+(-363.013e-3*(1e-6/l)) kf_ex=670.099e-18/(((w)**742.174e-3)*((l)**-208.654e-3))*2 ma_exp=(ma>1.5)*(af_ex-1)+(ma<1.5) xr1 ( n1 n2 sub) resistor_va r=val vc1=pgvc1 vc2=pgvc2 drift_mag=10e-6 drift_tau=1u rrph=rrphmis pvc=pvcpde

+ mr=vmis*vmis*2

+ af=af_ex kf=kf_ex/(abs(ma))**(ma_exp) c1 ( n1 sub ) capacitor c=1.011e-4*((1.15*w)+0.335e-6)*l_cal*abs(ma)/2.0

c2 ( n2 sub ) capacitor c=1.011e-4*((1.15*w)+0.335e-6)*l_cal*abs(ma)/2.0

ends rph

// *

// *

// *

// * endsection cap endlibrary s18_rc

59

60

Appendix B

Verilog-A Code Modeling Lifetime

Drift in RPH Resistor

‘include "disciplines.vams"

‘include "constants.vams"

//‘include "constants.h"

//‘include "discipline.h"

//nature Current

// abstol=1e-12;

// access=I;

// units="A";

// blowup=1e15;

//endnature

//nature Voltage

// abstol=1e-12;

// access=V;

// units="V";

// blowup=1e15;

61

//endnature

‘ifdef __VAMS_COMPACT_MODELING__

‘define ALIAS(alias,parameter) aliasparam alias = parameter;

‘define ERROR(str) \ begin \

$strobe(str); \

$finish(1); \ end

‘define WARNING(str) $strobe(str);

‘define OPP(nam,uni,des) (*units=uni, desc=des*) real nam;

‘else // not__VAMS_COMPACT_MODELING__

‘define ALIAS(alias,parameter)

‘ifdef insideADMS

‘define ERROR(str) \ begin \

$strobe(str); \

$finish(1); \ end

‘define WARNING(str) $strobe(str);

‘define OPP(nam,uni,des) real nam (*units=uni desc=des ask="yes"*);

‘else // notInsideADMS

‘define ERROR(str) \ begin \

$strobe(str); \

$finish(1); \ end

‘define WARNING(str) $strobe(str);

‘define OPP(nam,uni,des) real nam;

‘endif

62

‘endif

‘define SPICE_GMIN 1.0e-20

‘define EXP_THRESHOLD 34.0

‘define MIN_EXP 1.713908431e-15

‘define MAX_EXP 5.834617425e14

module resistor_va(n1, n2, sub); inout n1, n2, sub; electrical n1, n2, sub; branch (n1,n2) br_r; parameter real r = 1 from [-inf:inf]; parameter real vc1=1 from [-inf:inf]; parameter real vc2=1 from [-inf:inf]; parameter real rrph=1 from [-inf:inf]; parameter real pvc=1 from [-inf:inf]; parameter real d_time=0.0009 from [-inf:inf]; parameter real scale=1 from [-inf:inf]; analog begin

V(br_r) <+ I(br_r)*(r +(1.0/(1+exp(-30000*

($abstime - d_time)))*(-2990 + 150000*$vt)*

(0.6 - 0.6*exp(-scale*10000000.0*$vt*(1+exp(-1.2*$temperature))

*($abstime - d_time)*(1.0/(1+exp(-$temperature+305))))))); end endmodule

63

64

Appendix C

Skill GUI Code

;;; creating the File Name field trFileNameField = hiCreateStringField(

?name ’trFileNameField

?prompt "Ocean Script:"

?defValue ".cshrc"

?callback "trDoFieldCheckCB( hiGetCurrentForm() )"

?editable t

) procedure( trDoFieldCheckCB( theForm ) prog( (window_id) inPort = infile( theForm->trFileNameField->value ) myPort = outfile("/design/mm/os20/users/anartya.mandal+ os20+os20a+1/drift_EDIT.ocn") when( inPort while( gets( nextLine inPort ) if( nextLine == " ’(\"$MAX_S18_PDKROOT/models

/spectre/s18_rc.scs\" \"res2\")\n" then fprintf( myPort " ’(\"/design/mm/os20

/users/anartya.mandal+os20+os20a+1

65

)

)

/s18_rc_drfit.scs\" \"res1\")\n" ) else fprintf( myPort nextLine ) close( inPort )

) close( myPort )

)

) trbrowseBtn = hiCreateFormButton(

?name ’browseBtn

?buttonText "Browse..."

?callback "ddsFileBrowseCB( hiGetCurrentForm() ’trFileNameField)"

)

;;; of the field and imbeds it in a message trConeRadioField = hiCreateRadioField(

?name ’trConeRadioField

?prompt "Select Drift Model: "

?choices list( "rph" "rp" )

?value "rph"

?defValue "rph"

)

;;; create the driftstarttime box trDriftstart = hiCreateFloatField(

?name ’trDriftstart

?prompt "Drift Start Time (s): "

?value 0.0009

66

?defValue 0.0009

)

;;; create the driftscale box trDriftscale = hiCreateFloatField(

?name ’trDriftscale

?prompt "Drift Scale Factor: "

?value 1.0

?defValue 1.0

)

;;; creating the run button trButton = hiCreateButton(

?name ’trButton

?buttonText "Run"

?callback "trButtonCB(hiGetCurrentForm())"

)

;;; creating the form hiCreateAppForm(

?name ’trSampleForm

?formTitle "Drift Simulation Utility"

?callback ""

?fields

list( list(trFileNameField 5:5 600:20 120) list(trbrowseBtn 610:5 90:30 70) list(trConeRadioField 5:45 600:20 120) list(trDriftstart 5:85 600:20 120) list(trDriftscale 5:125 600:20 120)

67

list(trButton 255:165 150:40 120)

)

?unmapAfterCB nil

) ; hiCreateAppForm

;;; displaying the form hiDisplayForm( trSampleForm ) procedure( trButtonCB( theForm ) prog( ( drift_start scale ) drift_start = theForm->trDriftstart->value scale = theForm->trDriftscale->value inPort = infile( "/design/mm/os20/users

/anartya.mandal+os20+os20a+1/myresistor.va") myPort = outfile("/design/mm/os20/users

/anartya.mandal+os20+os20a+1/myresistor_EDIT.va") when( inPort while( gets( nextLine inPort ) case( nextLine

( "parameter real d_time=0.0009

from [-inf:inf];\n" fprintf( myPort "parameter real d_time=%f from

[-inf:inf];\n" drift_start ))

( "parameter real scale=1 from

[-inf:inf];\n" fprintf( myPort "parameter real scale=%f from

[-inf:inf];\n" scale ))

( t

68

fprintf( myPort nextLine ))

) ; case

) close( inPort )

) close( myPort ) load("drift_EDIT.ocn")

)

) ; procedure

69

70

Appendix D

Bibliography

[1] D. M. Kim, et. al, IEEE Trans. Electron Devices , vol. ED-31, no. 4, pp. 480-493,

1984

[2] M. J. Deen, et al. Low frequency noise in heavily doped polysilicon thin film resistors IEEE.

1998

[3] Mann, et al., Silicides and Local Interconnects for high performance VLSI applications.

IBM J. Res. and Dev.

1995

[4] Matts R. and Ulf S. Long-Term Stability and Electrical Properties of Compensation Doped Poly-Si IC-Resistors.

IEEE Electron Devices , Vol. 47, No. 2, 2000

[5] N. C. C. Lu, et. al, IEEE Trans. Electron Devices , vol. ED-30, no. 2, pp. 137-149,

1983

[6] Raman, M.S, et. al, Electron Devices, IEEE Transactions on , Issue Date: Aug.

2006

[7] Wei Li, and Rong-Chang Feng. Highly Accelerated Life Test for the Reliability

Assessment of the Lead-Free SMT Mainboard.

IEEE. Microsystems, Packaging,

Assembly Conference Taiwan.

2006

71